优快云话题挑战赛第2期

参赛话题:学习笔记

AD9850 DDS 模块

该模块附带了标头,因此在构建该模块方面不用操心了;我只需要设计电路的其余部分,以便对齐各种控制线(时钟、数据、复位、FQ UP)与模块的引脚。模块上有四个输出引脚,两个用于方波,两个用于正弦波。给定布局,我从标题条末端的正弦波输出中获取输出。我没有弄乱板上的电位器;所有的校准都是在软件中完成的。

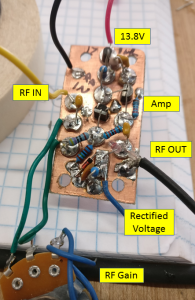

射频放大器

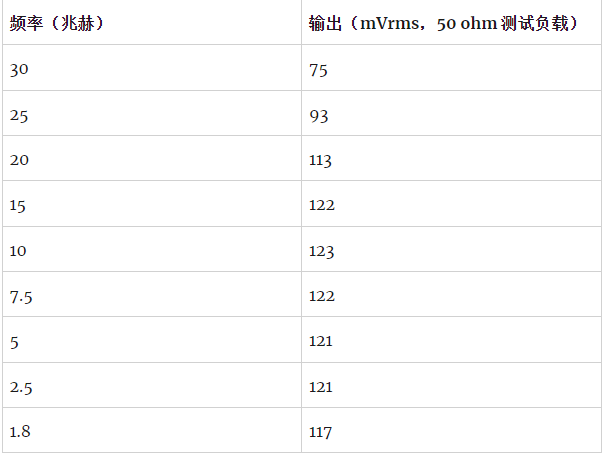

AD9850 的输出电平相对较低,幅度是频率的函数,随着频率的增加而下降。

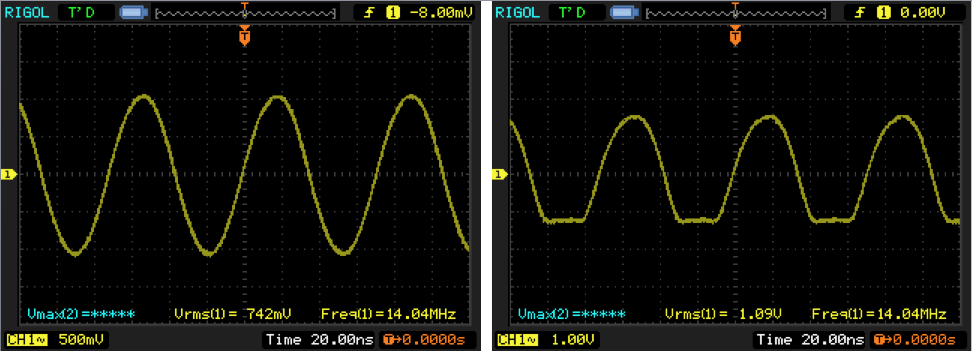

该放大器由 12V 电源轨供电,其输出电平与电压成正比。它基于两个 2N3904 晶体管,其效率也是频率的函数。好消息是,在较低频率下,电压输出令人印象深刻(在 15Mhz 时超过 1Vrms,在较低频率下更高),但通过观察到高于约 700 mV(rms),波形触底并失真,从而缓和了这一点。在 30Mhz 时,增益可以一直提高,输出保持正弦曲线,但在较低频率时,很容易将功率输出提高到失真点。

这是非常可重复的,并且在固定的测试负载下工作,我发现我可以在低频选择一个阈值电压电平,这对于干净的输出来说是一个安全的截止。我在输出端放置了一个电压整流器,并将其用作微处理器的一个 ADC 的输入。根据经验,我确定大约 800 mV 的电平是此放大器构建的一个很好的阈值。为了获得 ADC 的最大分辨率,我使用微处理器的内部 1.1V 电压基准作为满量程。当输出电压记录在 800mV 以上时,红色 LED 亮起,表示信号发生器处于或接近最大无失真输出。另一种方法是将值本身放在 LCD 显示屏上,但这感觉更直观。如果我真的需要知道价值,

由于这个 VFO 将在板凳上运行,最终我可能会做一些愚蠢的事情,比如将它连接到错误的负载上。作为保险,我在输出端添加了一个 4.7V 齐纳二极管,以防它最终馈入高阻抗负载。齐纳二极管会使电压读数失真,接近其齐纳电压,但下降到 1V 附近,在我们关心的地方,整流电压的测量值保持线性。

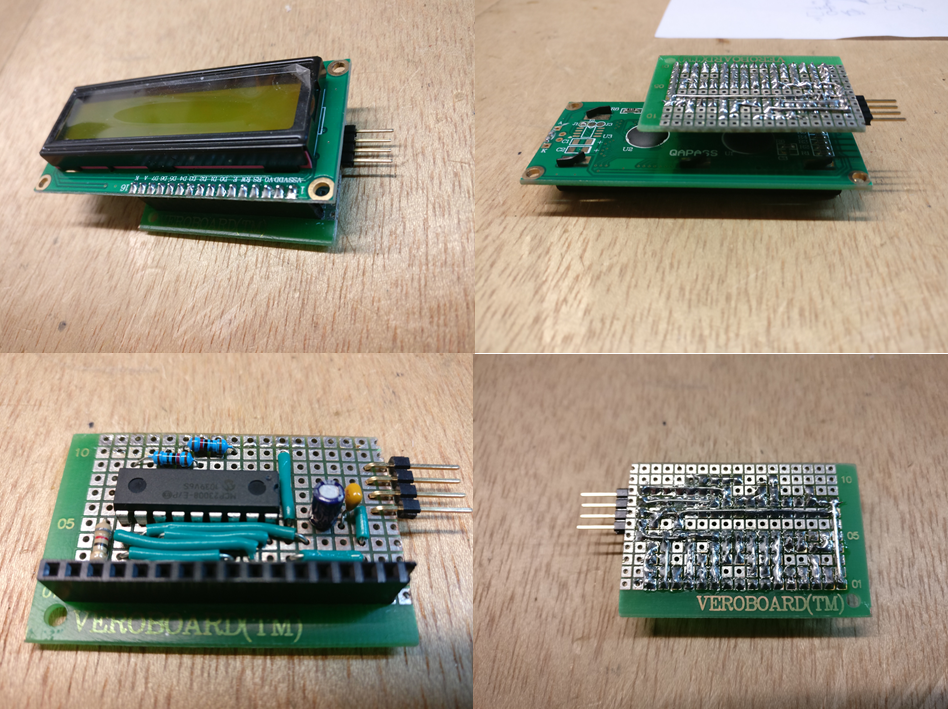

我为初学者引入了一些构建块:AD9850 的控制代码来自Let’s Build Something项目,保存记忆和上次设置的灵感来自AD7C 的 VFO项目,以及用于读取旋转编码器的中断服务例程来自我以前的说明。我还从 Adafruit (“Adafruit_LiquidCrystal.h) 中提取了通用的“wire”和“eeprom”库以及液晶显示库。

主回路密切关注输入,并根据需要做出反应以更新显示或调整 AD9850 的输出。它还密切关注 ADC 读取的值,以通过点亮警告 LED 来标记输出电平是否过高。

通过检查给定输入的读取频率的测试,最大限度地减少了专用于轮询的微处理器活动;如果最后一次读取时间太近,这些测试会围绕输入读取短路。在这和使用 ISR 捕捉旋转编码器的旋转之间,界面保持响应。

用户交互将通过旋转编码器设置频率。闪烁的光标始终出现在频率读数上,其位置决定了分别通过顺时针或逆时针旋转编码器来增加或减少哪个单位。按下旋转编码器将向右旋转位置,直到它到达几十赫兹的位置,此时它将环绕到几十兆赫兹。考虑到 vfo 的预期用途和 AD9850 的分辨率,赫兹单位显示为零且不可调整。

为了使调整更快,我实现了两个 VFO 存储器,它们保存在 eeprom(非易失性)存储器中。短按唤起记忆,长按设定。当设备开机时,如果没有设置内存或内存被破坏为无意义的值,处理器默认频率为 7.150 Mhz(硬编码)。但是,一旦设置了内存插槽 1,它就会在通电时始终设置为该频率。我考虑过 AD7C 的代码,它允许 VFO 打开到最后显示的频率,但这需要定期写入 eeprom。eeprom 中的每个内存位置都有有限(但非常大)数量的写入周期,他的代码通过仅在内存已更改并保留一小段时间后才写入来最小化写入频率,但我更喜欢让 eeprom 写入有意识的选择。

我的目标是对这个项目进行编码、构建和装箱,以便我可以实际使用它,但一个明显的改进是菜单系统。显示屏的第二行设置为在一定时间内显示一条消息,然后将其擦除。实现菜单模式并不难,其中旋转编码器可用于拨号(希望)配置设置的简短列表以及一些不太常用的功能。

一些参数是硬编码的,但可以通过这种方式设置:默认起始频率,以及高射频输出警告和 AD9850 晶振频率的经验确定值。对于一次性项目,我认为对这些进行硬编码很好,但如果生产了多个单元,每个单元都可能需要对这些值进行一些调整。

本文详细介绍了使用AD9850 DDS模块构建射频信号发生器的过程,包括电路设计、射频放大器的构建和优化。作者通过软件校准避免了硬件调整,并利用微处理器监控输出电平,以防止失真。此外,还讨论了如何通过电压阈值和LED指示器来管理输出限制,并分享了代码和库的来源。该设计还包括了两个存储器位置以保存频率设置,并在启动时恢复。最后,提出了菜单系统作为未来改进的方向。

本文详细介绍了使用AD9850 DDS模块构建射频信号发生器的过程,包括电路设计、射频放大器的构建和优化。作者通过软件校准避免了硬件调整,并利用微处理器监控输出电平,以防止失真。此外,还讨论了如何通过电压阈值和LED指示器来管理输出限制,并分享了代码和库的来源。该设计还包括了两个存储器位置以保存频率设置,并在启动时恢复。最后,提出了菜单系统作为未来改进的方向。

7502

7502

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?