ModelSim10.5c仿真详细过程记录

在学习使用QuartusPrime pro17.1时,发现仿真过程和低版本软件有所不同,查阅许多资料后了解到可以舍弃直接用Quartus调用ModelSim进行联合调试的方法,改为直接从ModelSim中打开testbench文件进行仿真调试,现将学习过程记录如下。

一.建立工程

-

先建立一个library工作库,命名为work,方法:File-new-library.(只在第一次创建时需要这一步,如果左下方library列表中已有work,可跳过这一步).

-

创建project,本文中以一个简单的二分频器为例,工程名设为half_clk,方法:File-new-project.

会跳出如下dialog,选择Create New Flie以创建新文件:

新文件命名与工程名相同,为half_clk:

最后将前一个对话框关掉即可(因为他不会自己关)。

二.编写主程序

代码如下:

module half_clk(clk_in,rst_n,clk_out);

input clk_in;

input rst_n;

output clk_out;

reg clk_out;

always@(posedge clk_in or negedge rst_n)

if(rst_n == 1'b0)

clk_out <= 1'b0;

else

clk_out <= ~clk_out;

endmodule

先保存,再编译,编译成功后左侧project列表里文件后面会出现一个绿色的对勾,下方Transcript框里会出现一行绿色的success字样。

三.编写仿真程序

在左侧空白区域右键单击添加testbench文件,过程:Add to Project - New Flie,命名为half_clk_tb,同样要注意将文件类型修改为Verilog!!(默认类型为HDL,生成的是一个压缩包,迷惑).

代码如下(是按照个人的编程习惯写的):

timescale 1ns/1ns(前面少一个角标)

`define clock_period 200

module half_clk_tb;

reg clk_in;

reg rst_n;

wire clk_out;

half_clk half_clk_0(

.clk_in(clk_in),

.rst_n(rst_n),

.clk_out(clk_out)

);

initial clk_in = 1'b1;

always #(`clock_period/2) clk_in = ~clk_in;

initial begin

rst_n = 1'b0;

#380;

rst_n = 1'b1;

#5000;

$stop;

end

endmodule

同样保存后再编译。

四.编译仿真

在上方菜单栏找到“Compile All”进行全编译,然后在左侧Library选项卡下右键单击testbench文件选择Simulate运行仿真。

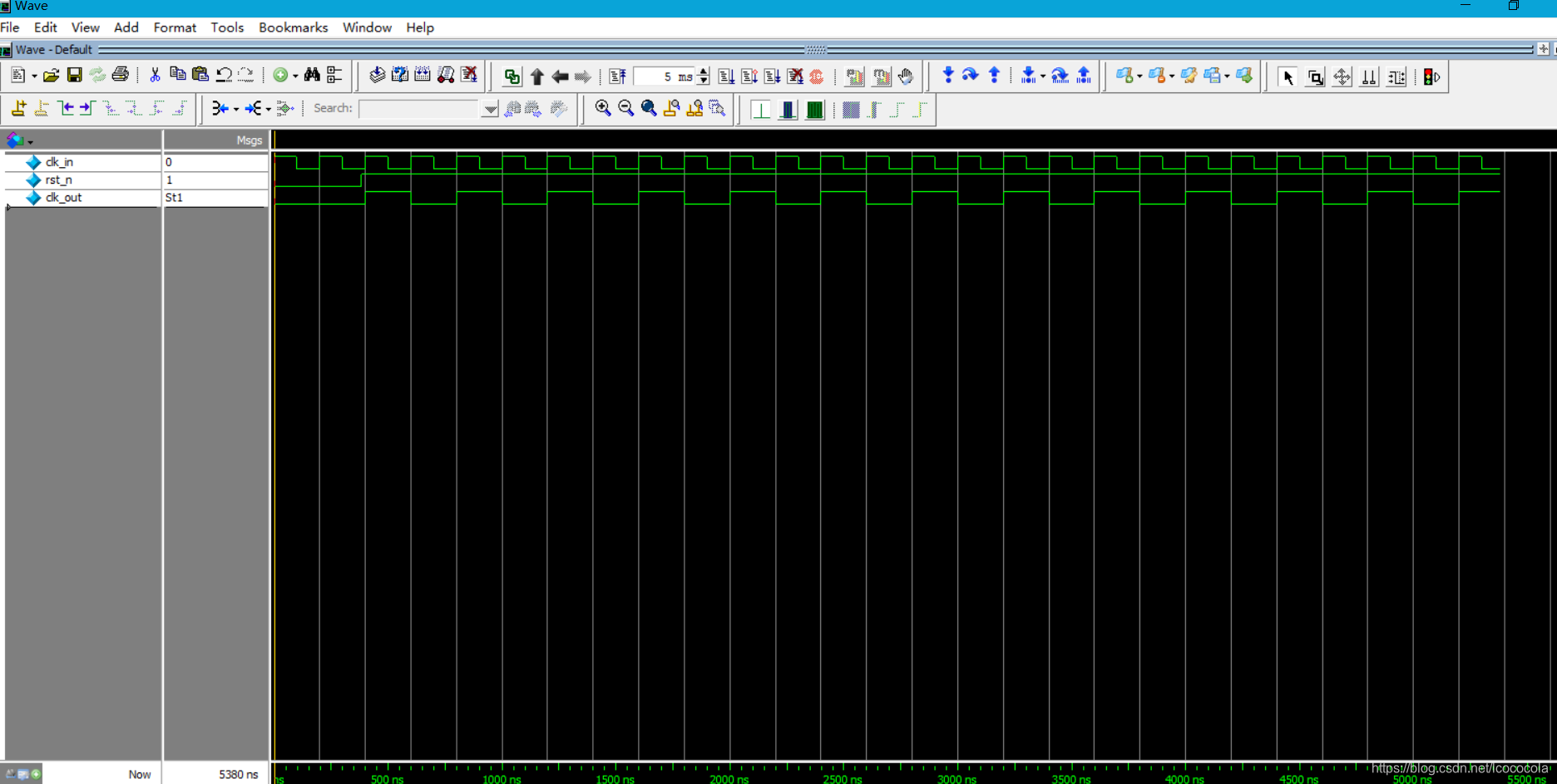

仿真完成后出现Object选项框,可以看到文件中涉及到的所有输入输出信号,ctrl+A全选,右键-Add wave添加波形,再打开wave窗口,上方工具栏找到Run all,就可以看到全部的仿真波形了。此时可以在wave窗口根据自己的喜好对所显示的内容继续宁增删或修改,方法跟旧版本ModelSim完全相同,于是不做赘述。效果如下:

仿真完成后记得quit,方法:Simulation - End Simulation。

至此,全部仿真结束。接下来打开一个之前用Quartus Prime pro17.1编写的工程文件测试一下是否能成功运行仿真。

五.尝试运用

- 采用直接打开之前编写的工程的方法。

发现open-不论是选择prj文件夹下的.qpf文件还是选择simulate-modelsim文件夹下的.vf文件,再全部编译时软件所编译的内容仍旧是上一个二分频工程里的file,与现在打开的文件无关,效果如下图, 可以说明这种尝试是无意义的。

- 新建一个project

前面的步骤跟上一个工程的创建步骤完全相同,这次将文件命名为fish(只是示例)

代码随便复制一段之前写的东西,然后编译。编译成功√

testbench也随便复制一段之前的,编译。√

add wave,run all,观察波形,如图

方法奏效。但这次所实验的只是一个简单的程序,如果涉及到的文件比较多,结构比较复杂了可能会麻烦一些。

THE END.(小白的学习笔记,如果有大佬看到希望可以不吝赐教🙏)

六.后记

在之后的使用过程中又有一点新的体会,记录如下:

按照上述记录来说,是无法直接打开quartus生成的project的,但随着ModelSim用的越来越多,现在也比以前更熟悉了,学会了使用Modelsim直接打开Quartus生成的程序的办法。

1.使用Quartus编写project(内含ip核),命名为ip_test

2.在top文件中例化pll ip核,定义输入时钟频率为100MHz,输出时钟频率为156.25MHz

3.程序写完之后在Quartus中全编译,成功

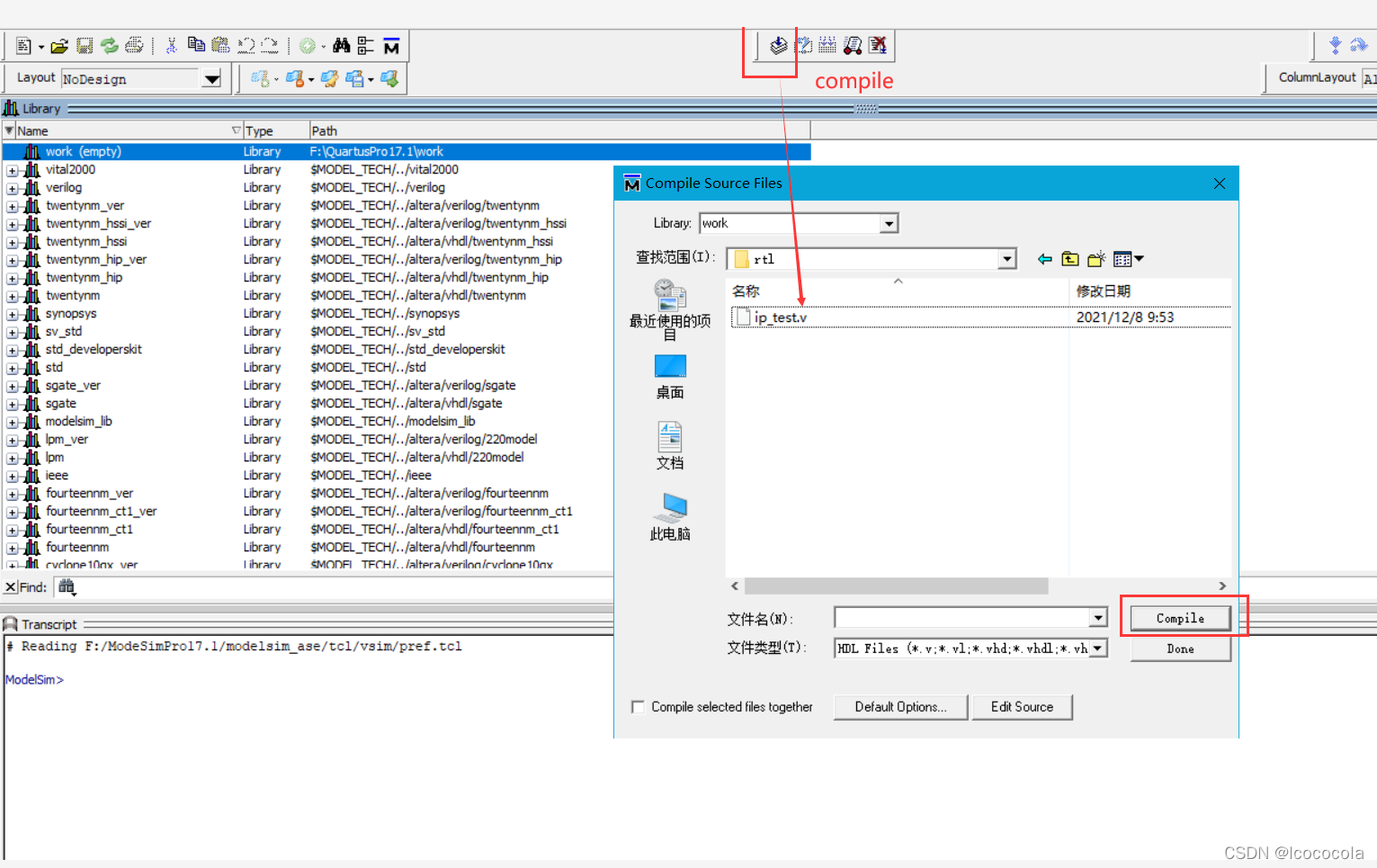

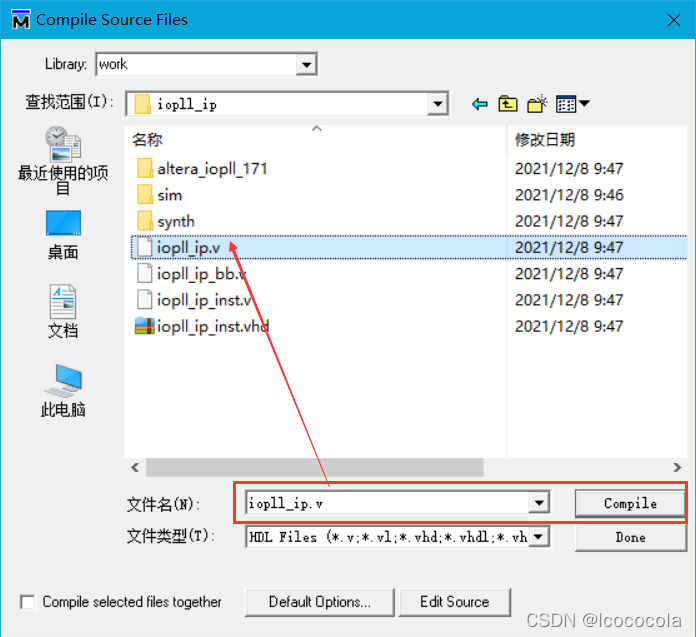

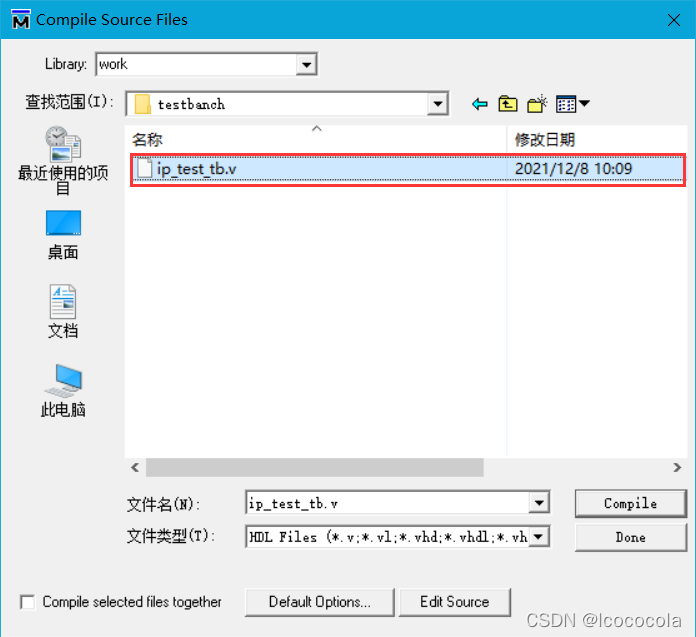

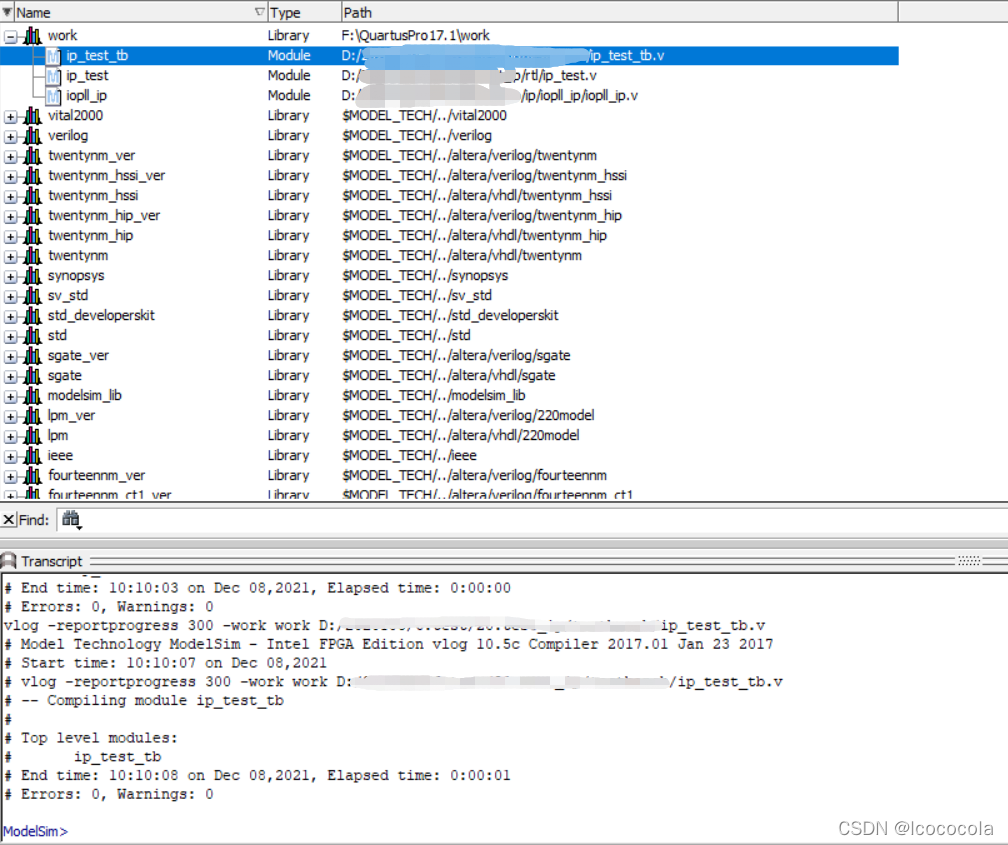

4.打开ModelSim,删除当前work中全部文件,将ip_test工程中的文件编译到work中,方法:

在这一步需要编译三个部分的文件:工程中涉及到的.v文件、testbench文件、ip核文件夹下的.v文件。

全部编译成功后,work库下是这样的:

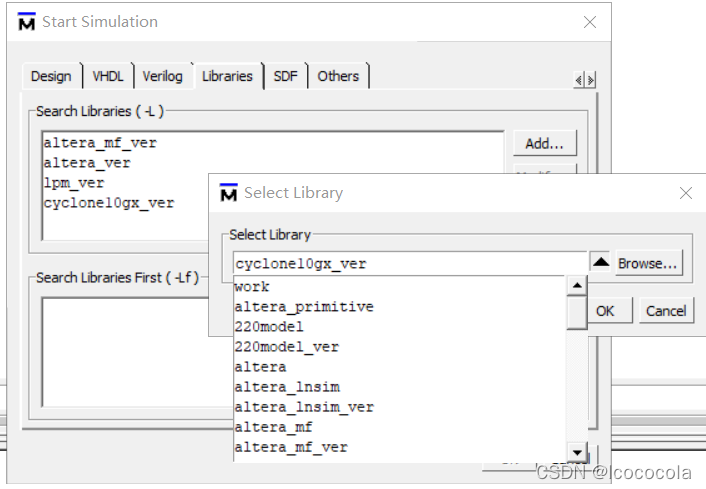

5.开始仿真。仿真前要注意添加几个lib:lpm库、primitive库、mf库、器件库,否则ip核仿真会失败,一般情况下这几个库就足够了,但如果所用到的ip核没有在这几个库中那就还需要自己查询并添加对应的lib(这一点我还在学习怎么查会更快速有效)。方法如下:Simulate-start simulation-libraries-add,然后从下拉选项中选择对应lib

添加完成后不要关闭对话框,切换到design选项卡下,选择要仿真的testbench文件,点击ok,仿真就开始运行啦!最后再根据自己的需求进行调试即可~

ModelSim10.5c与QuartusPrimepro17.1联合仿真步骤详解

ModelSim10.5c与QuartusPrimepro17.1联合仿真步骤详解

这篇博客详细记录了如何在ModelSim10.5c中直接进行Verilog项目的仿真调试,避免通过Quartus调用。首先介绍了创建library和project的步骤,接着编写了二分频器的主程序和testbench,并进行了编译。然后,重点讲解了如何在ModelSim中编译仿真程序,包括添加库、运行仿真和查看波形。最后,作者尝试直接打开Quartus工程进行仿真,但未成功,最后通过新建project实现了仿真。此外,还分享了后期如何处理Quartus生成的项目并在ModelSim中成功仿真的经验,涉及库的管理和ip核的仿真设置。

这篇博客详细记录了如何在ModelSim10.5c中直接进行Verilog项目的仿真调试,避免通过Quartus调用。首先介绍了创建library和project的步骤,接着编写了二分频器的主程序和testbench,并进行了编译。然后,重点讲解了如何在ModelSim中编译仿真程序,包括添加库、运行仿真和查看波形。最后,作者尝试直接打开Quartus工程进行仿真,但未成功,最后通过新建project实现了仿真。此外,还分享了后期如何处理Quartus生成的项目并在ModelSim中成功仿真的经验,涉及库的管理和ip核的仿真设置。

1374

1374

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?