目录

1.1 Analyze from the perspective of circuits

1.2 Analyze from the perspective of Flip-Flop

2.1 Analyze from the perspective of circuits

2.2 Analyze from the perspective of Flip-Flop

0 Overview

Firstly, we should know that Setup Time and Hold Time are attributes of Flip-Flops.

1 Setup Time

1.1 Analyze from the perspective of circuits

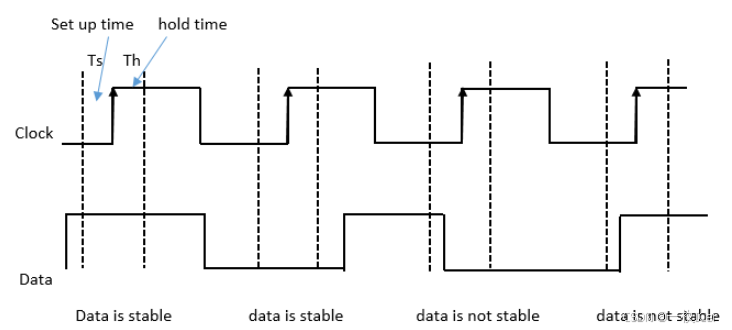

Definition of Setup Time: The minimum time for which the data should be stable at the input before the active edge of clock has arrived. In my opinion, the "stable" doe not mean "stay at here" but mean the time data enter the D pin.

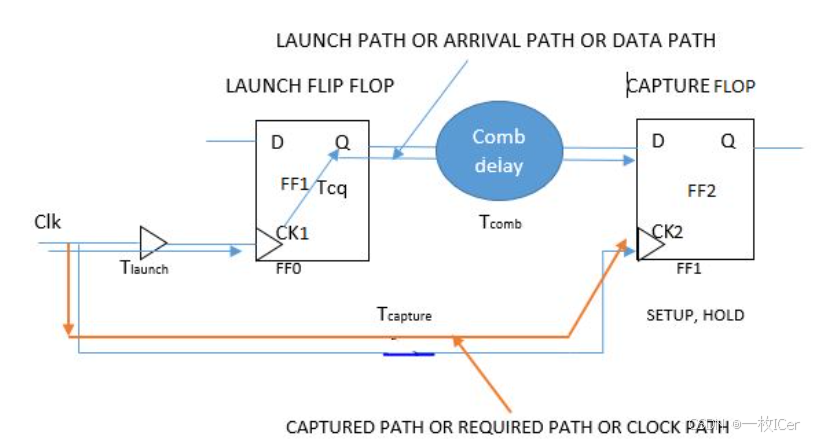

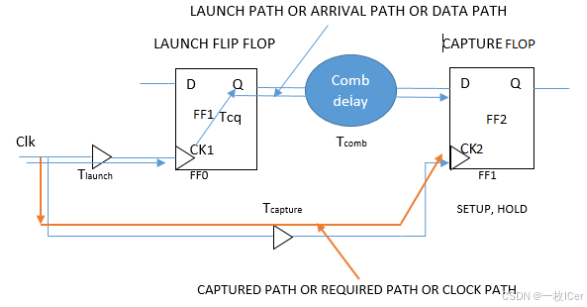

The data is launched from FF1 and captured at the FF2 at the next clock edge, The launched data should be present at the D pin of capture flop at least setup time before the next active edge of the clock arrives.

This time that data should arrive at the capture FF is called required time.

The time which is taken by data to actually arrive at the D pin of capture FF is called arrival time.

Expect not violation will produce

1.2 Analyze from the perspective of Flip-Flop

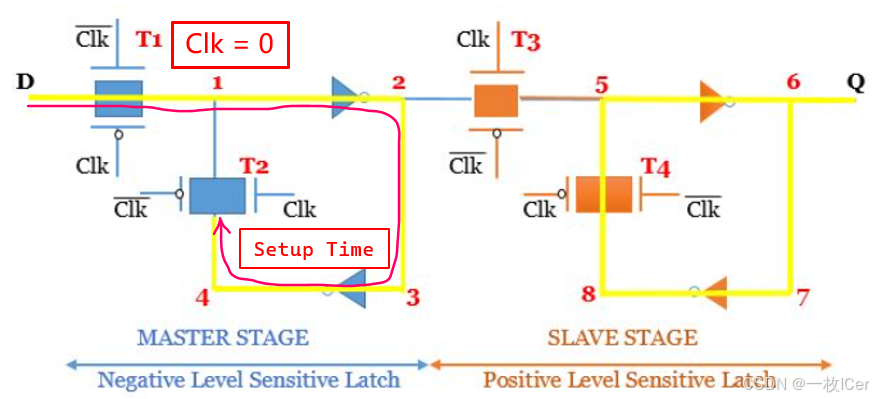

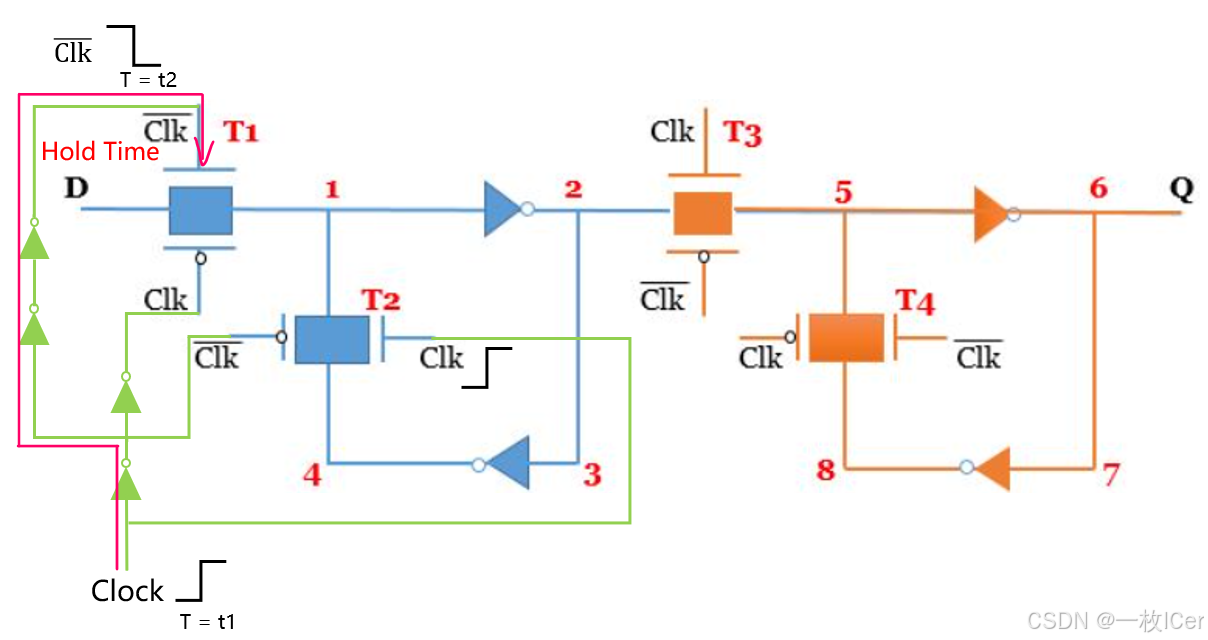

We have known the construction of Flip-Flops 【STA】 TRANSMISSION GATE, D-LATCH, D-FF

When the CLK is low the input (D) is following the path D-1-2-3-4 and it will take some time to reach at the node 4 that time we call setup time.

⭐In short, data travels along D-1-2-3-4 will cost the setup time.

Question : What happens if data is not stable for the setup time before the next active edge of the clock arrives ?

Answer : When the clock turns high the data which has to be launched should be present at node 4. However, since the speed of data is slow, data would not get enough time to travel to node 4, the data may be present somewhere between node 2 and 3. We don’t know which data will be launched at the rising edge of clock and output will be indeterminate because data is not reached at node 4 yet.

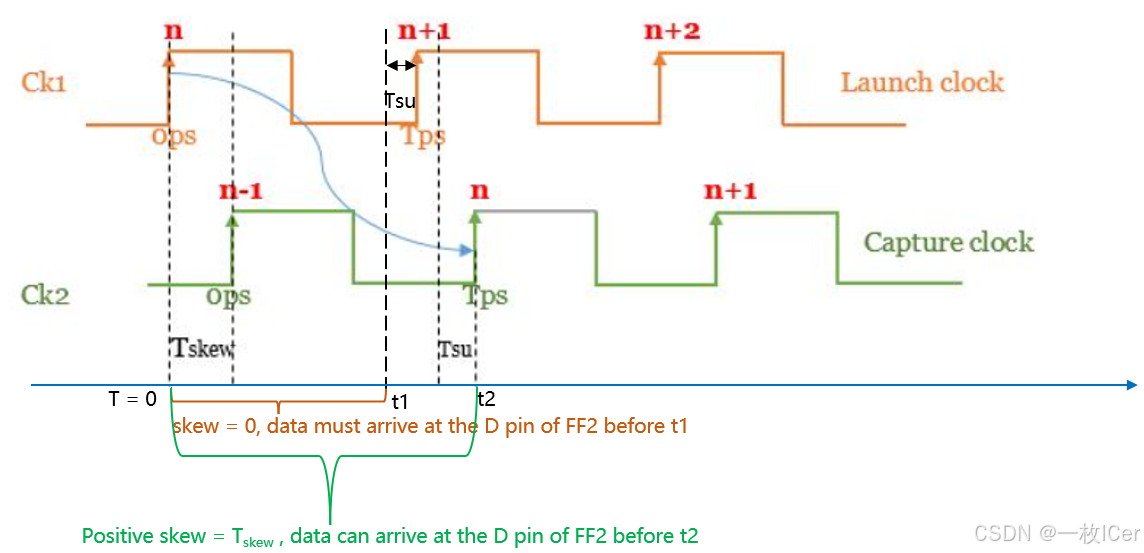

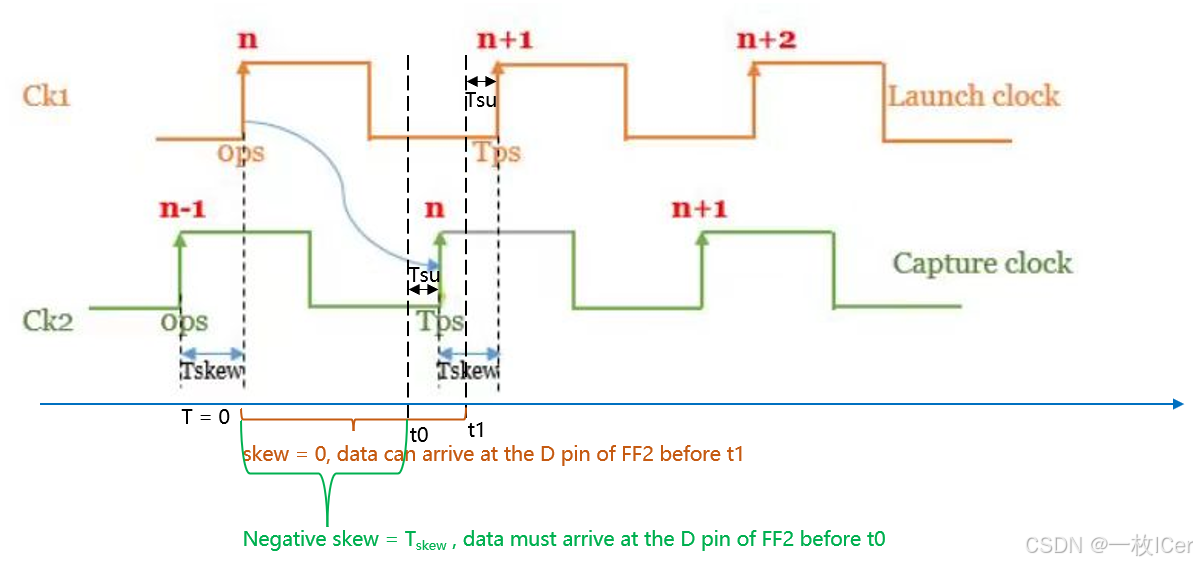

1.2.1 Positive Skew

If there is a positive skew (The triggering edge is relatively delayed), it means we are giving more time to data to arrive at D pin of capture FF. so positive skew is good for setup.

1.2.2 Negative skew

1.2.2 Negative skew

If there is a negative skew, it means we are giving less time to data to arrive at D pin of capture FF. so negtive skew is bad for setup.

2 Hold Time

2.1 Analyze from the perspective of circuits

Definition of Hold Time: The minimum time for which the data should be stable at the input after the active edge of clock has arrived.

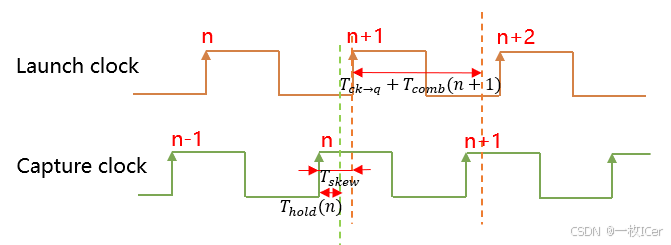

The data is launched from FF1 at 0 second and this data should be captured at FF2 after one clock period (Tclk). The hold time is to make sure that the current data (launched from rising edge n) which is being captured at the FF2 should not be corrupted by the next data (being launched from the rising edge n+1) at the same edge.

In my opinion, we don't allow data(n+1) come to the D pin of FF2 so fast regradless of the clk of T1 of capture FF2 is low or high at this time.

The time that data(n+1) will arrive at the D pin of capture FF is called Arrival time.

Basically this current data(n) should be held for enough time for it to be captured reliably, that enough time is called hold time.

Expect not violation will produce

2.2 Analyze from the perspective of Flip-Flop

The Clock is turning from low to high the T1 and T4 transmission gate is turned off and stop entering the new data into the device. However, transmission gate T1 does not turn off immediately, it will take some time to become OFF because the clock is passes through many buffer and inverter then reached to the transmission gate T1. In short, we can say that transmission gate T1 also take some time to turn OFF.

Basically new data should not enter into the devices during that time also so the hold time will be the time is to take the transmission gate to turn off completely after the clock edge has arrived(t2 - t1 in Fig).

If there is any combination delay in the data path then the hold requirement will change.

Question : What happens if data arrives at the D pin of capture FF faster than Clock arrives at the T1 ?

Answer : During the time when Clock has changed from low to high, data arrives at the D pin of capture FF faster than high Clock-level arrives at the T1, new data will come into D pin of FF2 and disturbed the current data which is being captured.

Next we will explore the HOLD TIME further, skew wil also be considered.

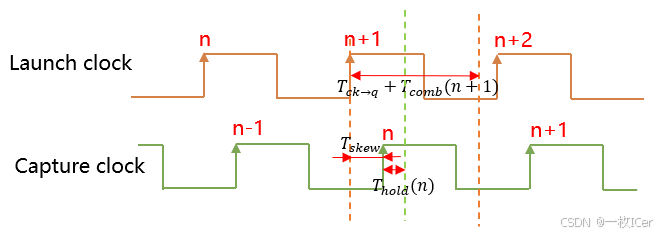

2.2.1 Positive Skew

It means the next data (n+1) will be launched earlier from the launch flop FF1 than the Capture Clock, when data(n+1) has arrived the D pin of FF2, the Capture Clock may not arrive here, so the data (n) also has not be captured yet.

When skew is positive, data(n) needs to be stable for longer time(Tskew+ Thold time) at the capture clock otherwise data(n) will be corrupted. So we can say Positive skew is bad for hold time.

2.2.2 Negative Skew

If exists a negative slew, the data(n) is being captured at captured flop FF2 earlier, but at the time data(n+1) will not be getting launched from the launched flip-flop FF1.

The data(n) has enough time to be hold at the input to be captured reliability but the launch flip-flop has not launched data(n+1). So negative skew is good for hold time.

3750

3750

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?