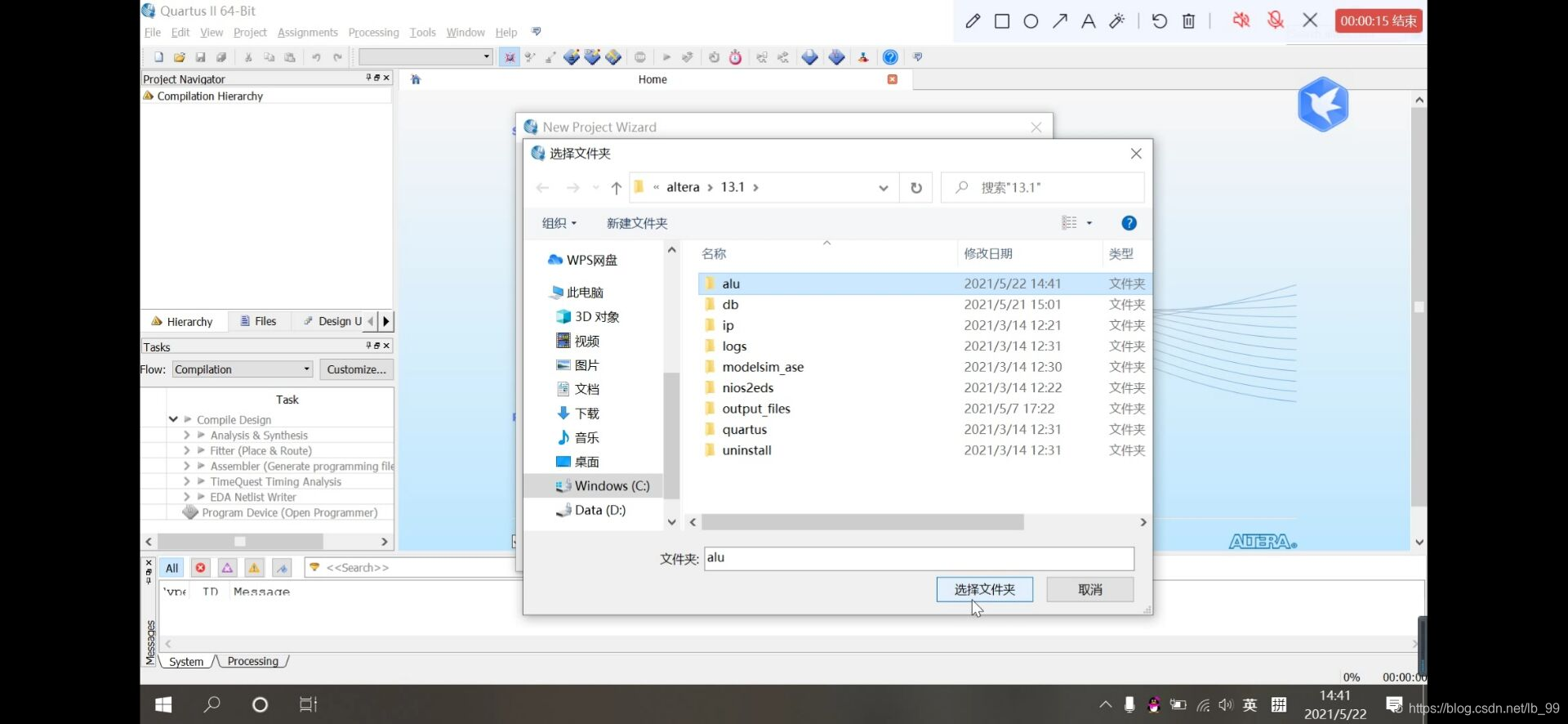

1.新建文件夹命名alu

2新建一个工程,点击输入框,输入代码

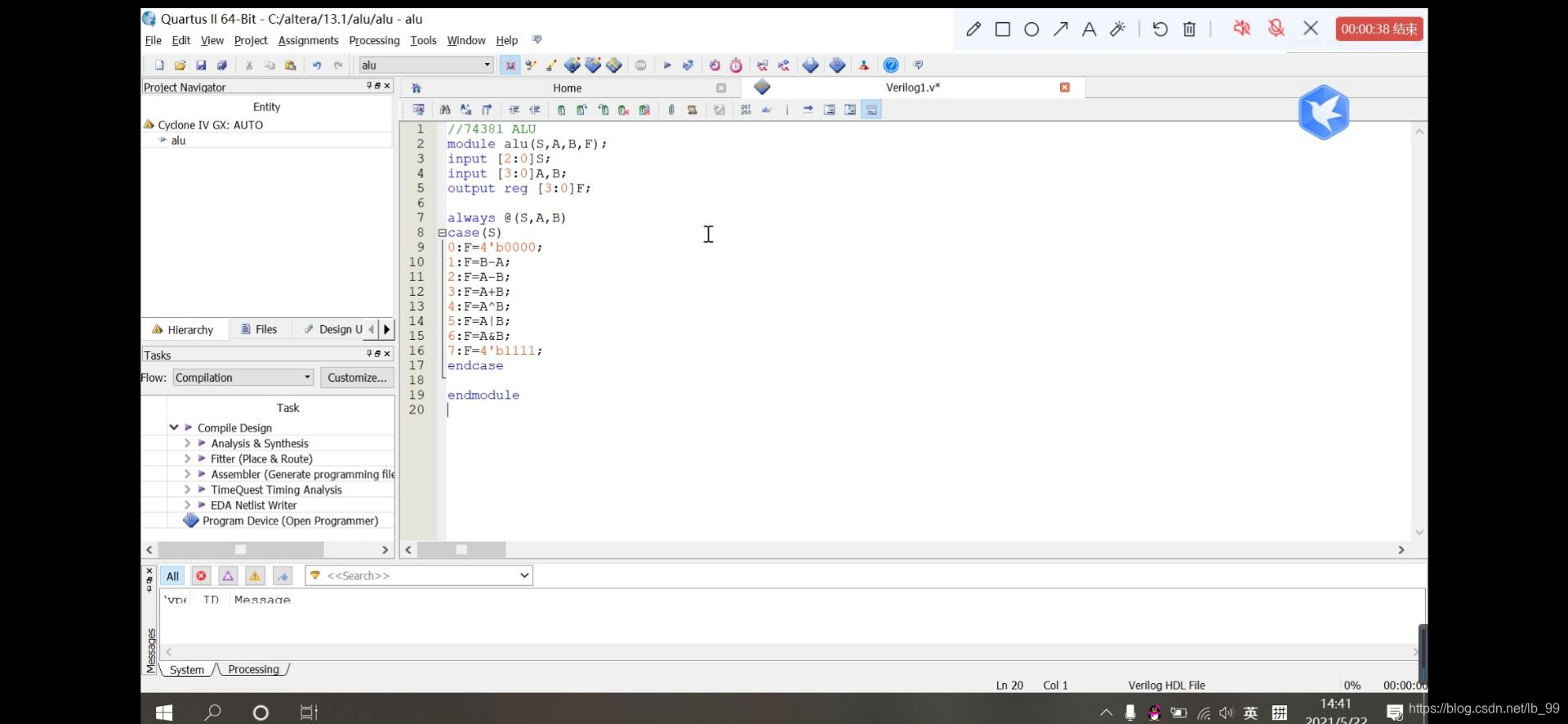

//74381 ALU

module alu(S,A,B,F);

input [2:0]S;

input [3:0]A,B;

output reg [3:0]F;

always @(S,A,B)

case(S)

0:F=4’b0000;

1:F=B-A;

2:F=A-B;

3:F=A+B;

4:F=A^B;

5:F=A|B;

6:F=A&B;

7:F=4’b1111;

endcase

endmodule

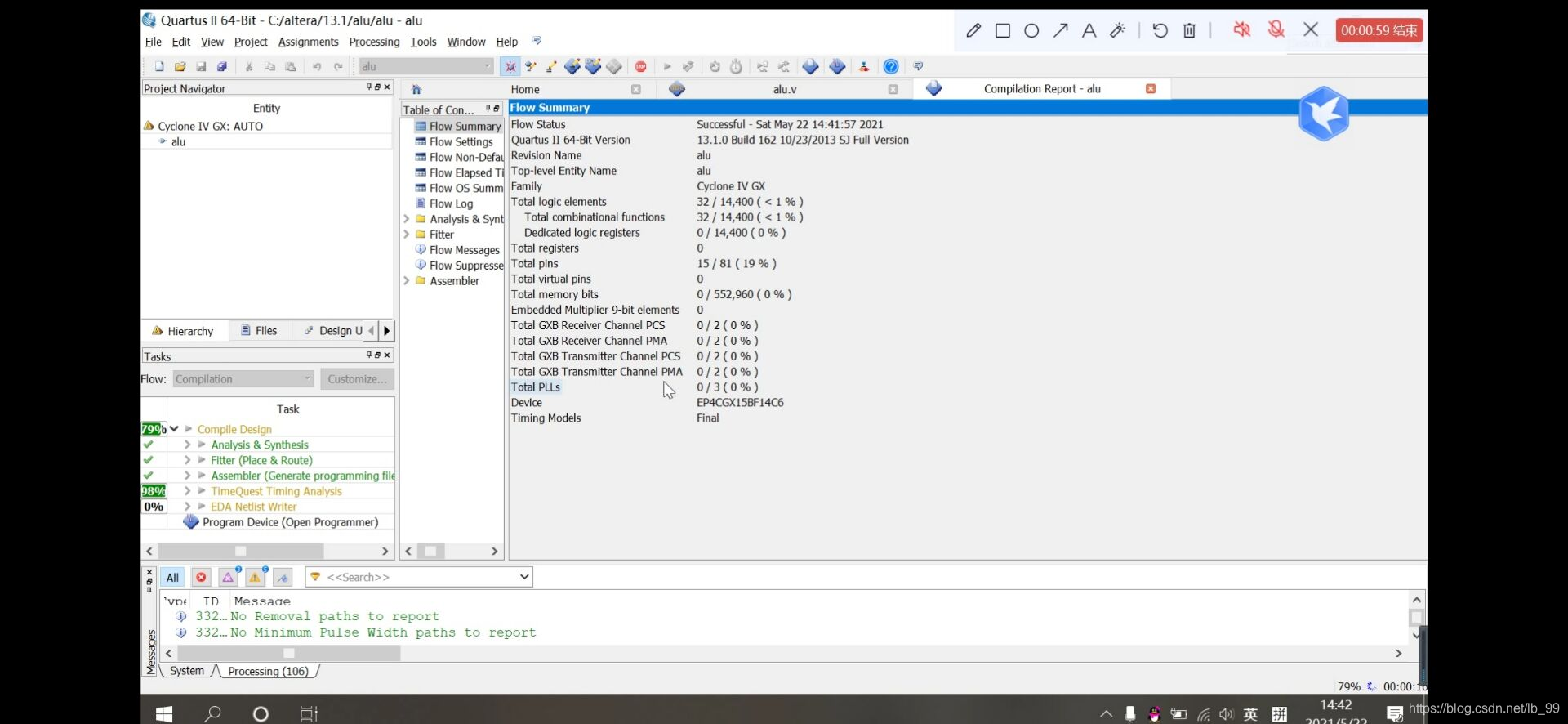

3.点击运行按钮,开始运行检查错

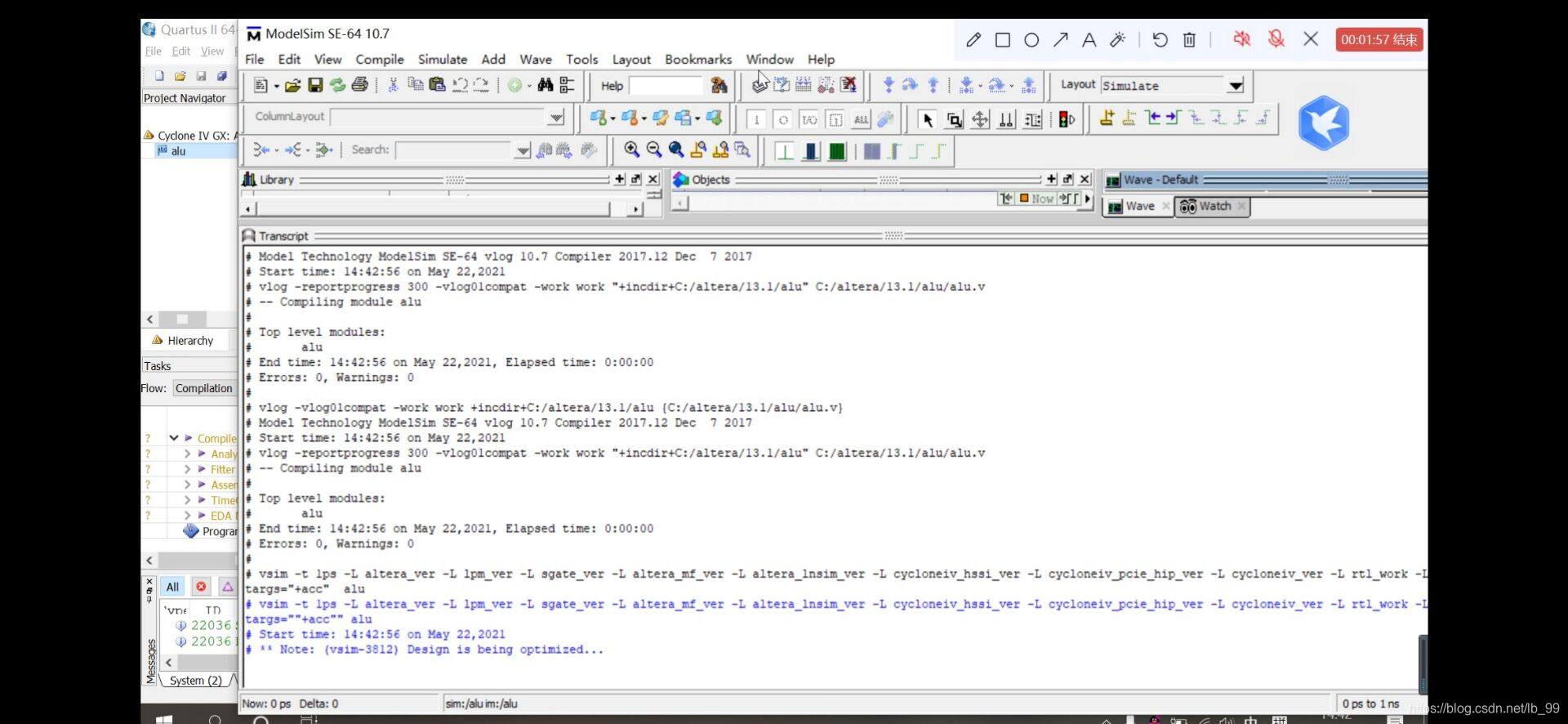

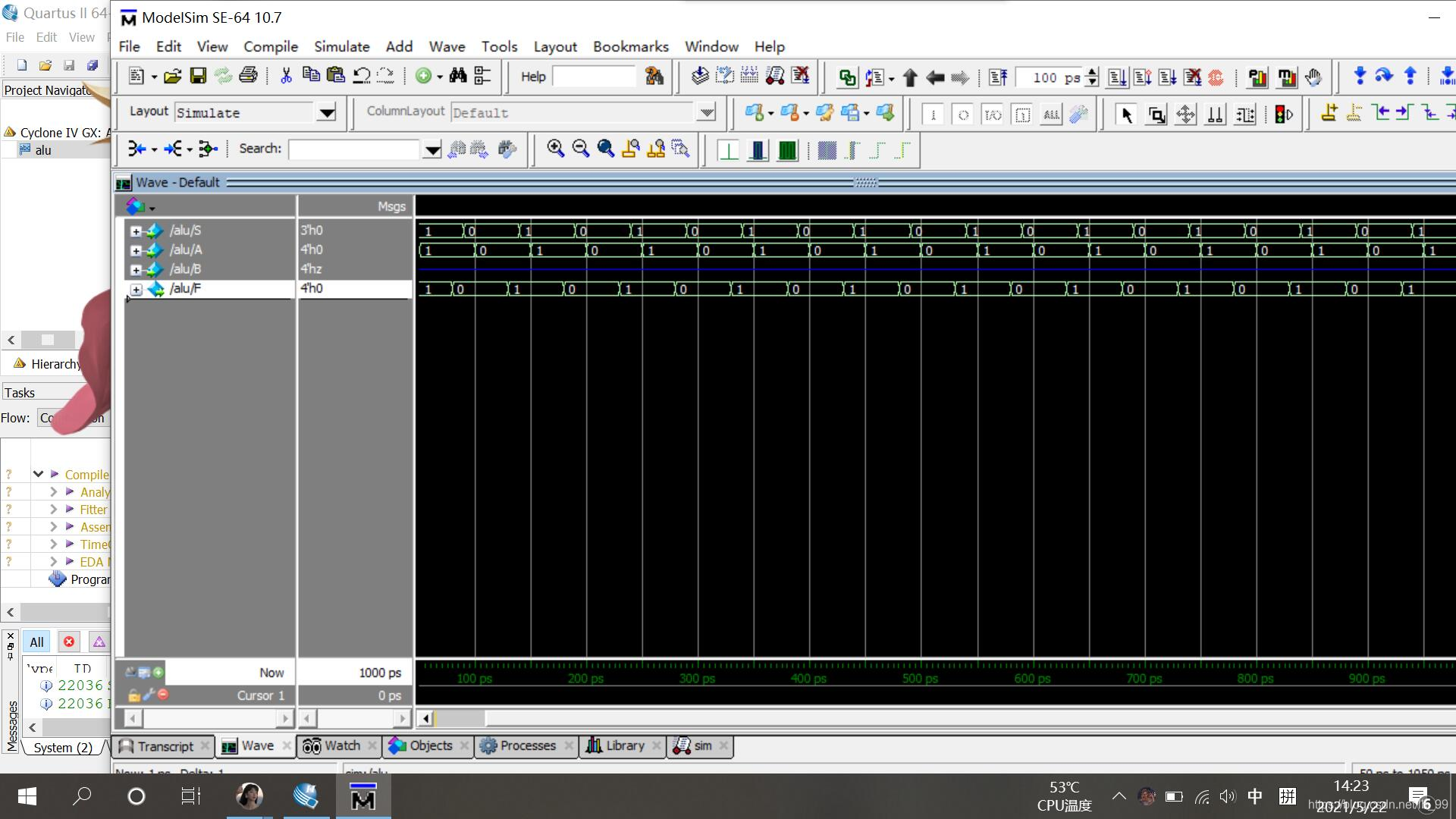

4.全部正确后,改变仿真途径为modelsim开始进行联合仿真

5.改变波长数值导出结果

6.视频链接:https://www.bilibili.com/video/BV1Yy4y1W789?share_source=copy_web

这篇博客详细介绍了如何使用Verilog语言新建并编写74381ALU(算术逻辑单元)的代码模块。在代码中,博主展示了如何根据输入信号S、A和B执行不同的逻辑运算,包括加减、异或、与、或等,并提供了仿真路径设置和波形导出的步骤。此外,还提供了一个视频链接辅助理解。

这篇博客详细介绍了如何使用Verilog语言新建并编写74381ALU(算术逻辑单元)的代码模块。在代码中,博主展示了如何根据输入信号S、A和B执行不同的逻辑运算,包括加减、异或、与、或等,并提供了仿真路径设置和波形导出的步骤。此外,还提供了一个视频链接辅助理解。

1584

1584

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?