一种基于XOR‐XNOR模块的可扩展高速混合1位全加器设计

1 | 引言

低功耗和便携式设备的广泛应用已极大地提高了对具有最小功耗的高速电子电路的需求。1因此,在当今的集成电路(IC)设计中,具有最佳速度和硅片面积的节能电路实现技术已成为关键焦点。2

全加器(FA)是现代数字系统中的关键元件,因为诸如乘法、减法和幅度比较等许多数学运算都需要加法操作。3此外,全加器在现代数字信号处理器、微处理器以及视频和图像处理器的多个算术模块中仍是一个核心操作。另外,在宽字长加法器的实现中也需要全加器。4,5因此,全加器模块的设计优化可以在各种算术单元中带来性能参数的全面改善。

本文提出了一种结合了CCMOS逻辑、传输管(PTs)和传输门(TGs)优点的新型全加器(FA)设计。为了研究所提出设计的性能,使用Cadence设计和仿真工具进行了全面的仿真。所提出的全加器性能与10种现有全加器设计进行了对比。电源电压在0.6至1.2 V范围内变化,以分析电压变化对全加器性能的影响。为了研究可扩展性,所有全加器设计均扩展至32位,并对性能参数进行了分析和比较。结果表明,与现有同类设计相比,所提出的全加器具有优越的性能指标。

2 | 现有研究综述

基于互补型传输管逻辑(CPL)的全加器被认为是最早的互补金属氧化物半导体型全加器拓扑结构。6由于存在电压退化、驱动能力低、功耗高、硅片面积大以及晶体管数量多等问题,目前在集成电路设计中已不再使用互补型传输管逻辑全加器。随后,CCMOS型全加器设计解决了驱动能力和电压退化的问题。7然而,与互补型传输管逻辑全加器相关的其余问题仍然存在。CPL和CCMOS全加器仅采用一种逻辑风格实现,因此属于单逻辑全加器的范畴。

近年来,利用多种逻辑技术的混合设计方法在设计人员和研究人员中引起了极大的关注。8,9 XOR‐XNOR模块在全加器中起着至关重要的作用,因为各种全加器设计方法同时使用异或‐同或信号。巴塔查里亚等人、10童等人、11以及帕拉梅斯瓦拉和斯里尼瓦萨亚12提出的全加器设计是基于XOR‐XNOR的全加器设计的示例。在这些设计中,异或‐同或信号作为内部节点工作。13哈苏内等人14开发的全加器采用了分支CMOS逻辑、传输管逻辑和互补CMOS逻辑。用于和与进位生成的电路外层端口包含互补CMOS反相器,以提供足够的驱动能力。米尔扎伊等人15开发的全加器输出端口也具有相同的情况。阿米尼‐瓦拉沙尼等人16和蒂鲁马拉塞蒂和马楚帕利17提出了另外两种基于混合逻辑的全加器设计。

门控扩散输入(GDI)方法可实现低晶体管数量的全加器设计。18,19但GDI单元存在阈值电压下降和驱动能力差的主要问题。萨纳帕拉和萨克提韦尔提出的基于GDI的全加器20仅需14个晶体管。为应对电压退化问题,肖巴和纳基兰开发了基于改进GDI单元的全加器。21然而,与非全摆幅GDI加法器相比,基于改进GDI单元的全加器的晶体管数量显著增加。

3 | 基于XOR‐XNOR的混合全加器设计

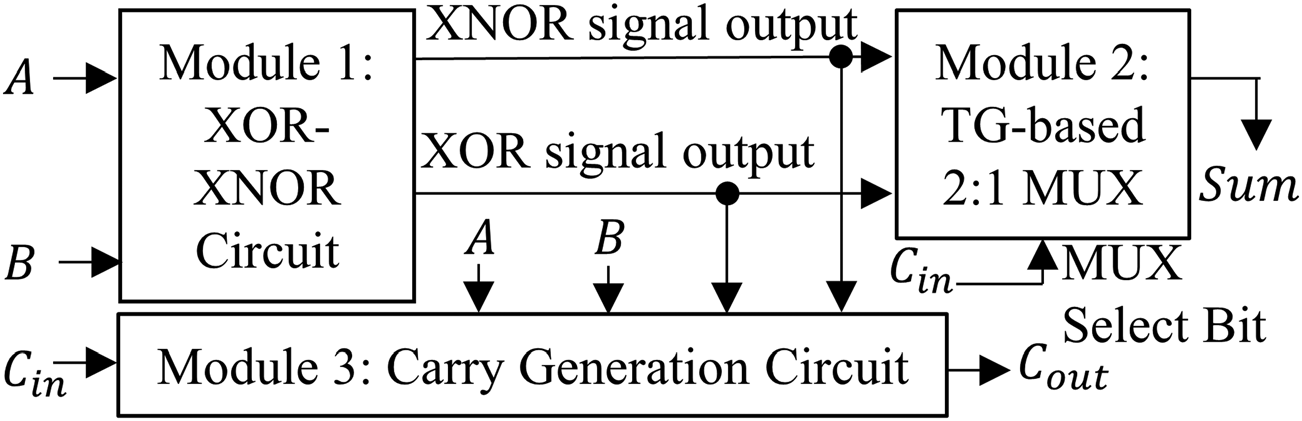

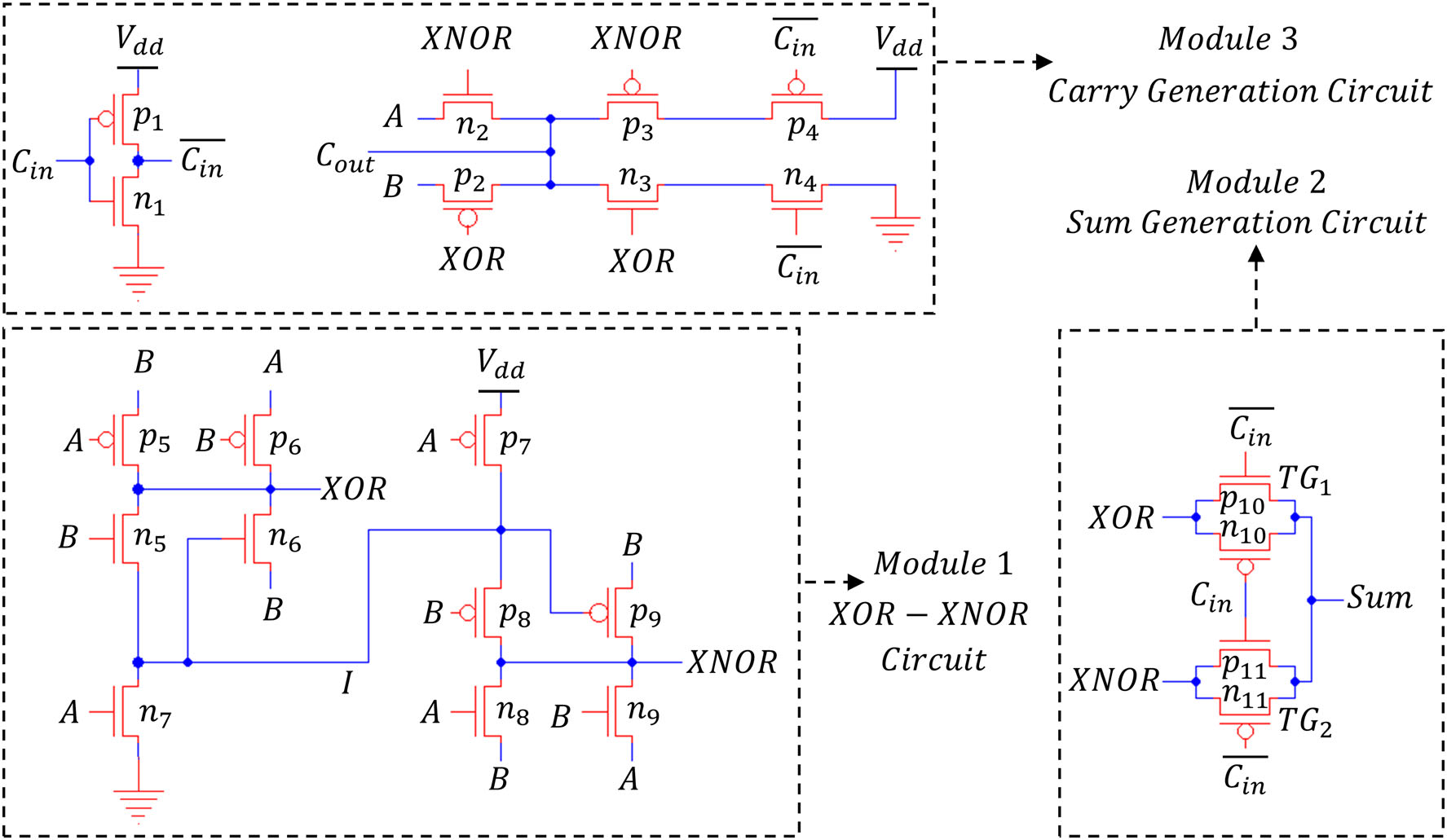

基于XOR‐XNOR模块的所提出的混合全加器的基本构建模块如图1所示。本研究中提出的基于XOR‐XNOR的全加器的完整原理图如图2所示,分为三个模块。

3.1 | 提出 XOR‐XNOR模块

分析表1中所示XOR操作的真值表,可得出以下适用于所提出的全摆幅双输入异或信号生成的条件。

条件1:如果 A = 0,B = 0,则 XOR = B。

条件2:如果 A = 0,B = 1,则 XOR = B。

条件3:如果 A = 1,B = 0,则 XOR = A。

条件4:如果 A = 1,B = 1,则 XOR = 地。

对于异或信号生成的条件1,p5和p6导通,导致弱逻辑0向异或节点传递(因为PMOS传递弱逻辑0)。为解决此问题并提供强逻辑0,使用了n6。在条件1下,A= 0使得p7导通,结果中间节点I变为逻辑1。该逻辑1使n6导通,从而将强逻辑0传递到异或节点(因为NMOS传递强逻辑1)。对于条件2,n5,

n6,和p5晶体管导通。尽管n5和n6传递弱逻辑1,但p5确保了全摆幅的强逻辑1。对于条件3,p6导通,将强逻辑1传递到异或节点。最后,对于条件4,n5和n7晶体管导通,向异或节点提供强逻辑0。

从表1分析可知,为提出的两输入同或信号生成确定的条件集如下:

条件1:如果 A = 0,B = 0,则 XNOR = Vdd 。

条件2:如果 A = 0, B = 1,则 XNOR = A。

条件3:如果 A = 1, B = 0,则 XNOR = B。

条件4:如果 A = 1, B = 1,则 XNOR = B。

对于2输入XNOR门的条件1,p7和p8晶体管导通,从而得到强逻辑1作为XNOR门输出。在条件2的情况下,通过n9提供强逻辑0。对于条件3,p8 ,、p9 ,和n8均

| 表1 提出的异或‐同或电路的真值表、晶体管路径和输出逻辑信号 | ||||||

|---|---|---|---|---|---|---|

| 输入信号部分 | 晶体管路径 | 输出信号部分 | ||||

| 条件编号 | A | B | 非全摆幅路径 | 全摆幅路径 | 输出信号 | 输出逻辑 |

| 异或信号 | ||||||

| 1. | 0 | 0 | p5/p6 | n6 | B | B = 0 |

| 2. | 0 | 1 | n5/n6 | p5 | B | B = 1 |

| 3. | 1 | 0 | ---- | p6 | A | A = 1 |

| 4. | 1 | 1 | ---- | n5和 n7 | Gnd | 地 = 0 |

| XNOR 信号 | ||||||

| 1. | 0 | 0 | ---- | p7和 p8 | Vdd | Vdd= 1 |

| 2. | 0 | 1 | ---- | n9 | A | A = 0 |

| 3. | 1 | 0 | p8 /p9 | n8 | B | B = 0 |

| 4. | 1 | 1 | n8 /n9 | p9 | B | B = 1 |

接通。此处,p8和p9提供弱逻辑0,n8提供强逻辑0。因此,条件3的最终结果强逻辑0由n8获得。最后,对于条件4,n8和n9被接通,提供弱逻辑1。为解决此问题并提供强逻辑1,增加了p9。在条件4的情况下,n7导通(因为A = 1)。结果,中间节点I变为逻辑0。该I的逻辑0通过p9导通,从而将强逻辑1传递到XNOR节点。

表1总结了XOR‐XNOR模块在不同逻辑条件下全摆幅和非全摆幅的晶体管路径。通过仔细分析表1可以看出,对于XOR‐XNOR模块的每种逻辑条件,均存在一条全摆幅晶体管路径。因此,所提出的XOR‐XNOR模块能够提供全摆幅输出,且不会产生任何电压损失。

3.2 | 和生成电路

分析根据1位全加器的逻辑表(表2),和生成满足以下条件。

条件1:如果 Cin= 0,则 和 = XOR (A XOR B)。

条件2:如果 Cin= 1,则 和 = XNOR (A XNOR B)。

为了实现上述和生成的条件,使用了基于传输门的2:1多路复用器。在图2中,传感器1实现条件1,传感器2实现条件2。由于传感器可以传递强0和强逻辑1,因此和生成电路实现了全摆幅逻辑。

3.3 | 进位生成电路

分析表2,所提出的进位生成电路满足以下条件:

条件1:如果Cin= 0,AB = 01或AB = 10,则Cout=接地。

条件2:如果Cin= 1,AB = 01或AB = 10,则Cout= Vdd。

条件3:如果AB = 00,则Cout= A。

条件4:如果AB = 11,则Cout= B。

在这种情况下,n3,n4通过提供强逻辑0来实现条件1。晶体管p3,p4通过提供强逻辑1来实现条件2。在条件3的情况下,n2提供强逻辑0。最后,p2通过提供强逻辑1来实现条件4。对于进位生成电路,分析全加器真值表可知,Cout在条件3和4下不依赖于Cin。所有晶体管路径用于

| 表2 输入–提出的和与进位生成电路的输出逻辑和晶体管路径 | ||||||

|---|---|---|---|---|---|---|

| 输入信号 | 和生成 | 进位生成 | ||||

| Cin | A | B | 全摆幅路径 | 输出逻辑 | 全摆幅路径 | 输出逻辑 |

| 0 | 0 | 0 | TG 1 | XOR=0 | n2 | A = 0 |

| 0 | 0 | 1 | TG 1 | XOR=1 | n3 ,n4 | 地 = 0 |

| 0 | 1 | 0 | TG 1 | XOR=1 | n3 ,n4 | 地 = 0 |

| 0 | 1 | 1 | TG 1 | XOR=0 | p2 | B = 1 |

| 1 | 0 | 0 | TG 2 | XNOR=1 | n2 | A = 0 |

| 1 | 0 | 1 | TG 2 | XNOR=0 | p3 , p4 | Vdd = 1 |

| 1 | 1 | 0 | TG 2 | XNOR=0 | p3 ,p4 | Vdd = 1 |

| 1 | 1 | 1 | TG 2 | XNOR=1 | p2 | B = 1 |

| ## 4 | 仿真结果与讨论 |

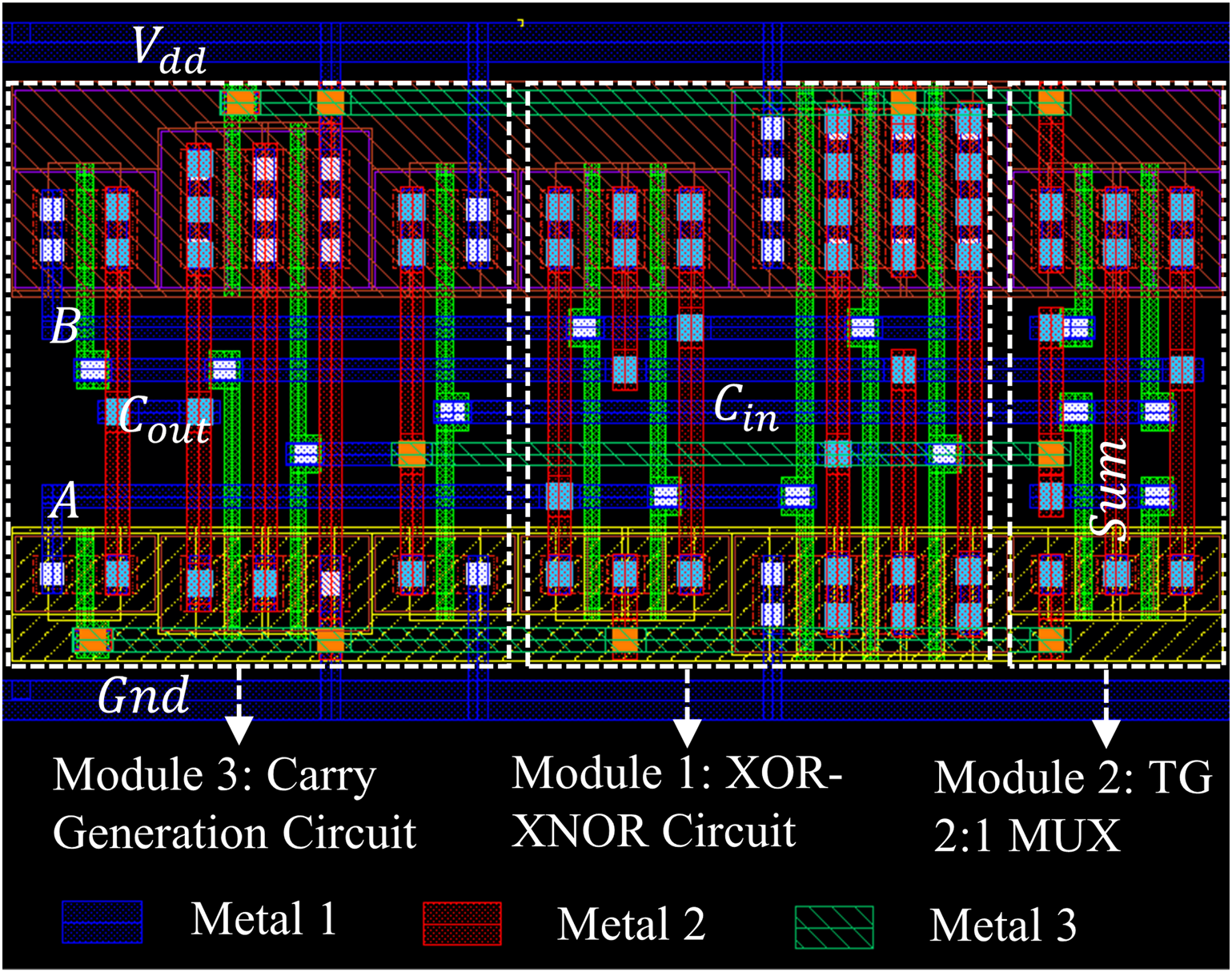

采用标准45纳米CMOS技术的Cadence仿真工具已用于全加器的性能检测。仿真测试平台的输入端包含缓冲器,输出端则使用4单元尺寸反相器的扇出(FO4)作为负载。输入端的缓冲器用于对生成的方波信号引入失真。全加器单元在传播延迟(PD)、平均功率(AP)和功耗延迟积(PDP)方面进行了比较。对于AP,将所有可能的A、B和Cin信号组合施加到一个全加器单元上,并计算相应的功耗,然后取这些功耗的平均值作为AP。在计算AP时,仅考虑全加器组件本身的功耗,而不包括输入端缓冲器和输出端负载反相器的功耗。对于PD,采用最坏情况下的延迟(关键路径延迟)。PDP是AP与PD的乘积。实现提出的基于XOR‐XNOR的全加器所使用的晶体管尺寸见表3。现有设计也采用了合适的晶体管尺寸以优化速度。为了比较全加器单元,所有全加器设计均进行了后布局仿真。所提出的1位全加器的布局如图3所示。

| 表3 提出的全加器的晶体管尺寸 | ||

|---|---|---|

| 晶体管标签 | 沟道长度 (nm) | 沟道宽度 (nm) |

| n1,n2,n8,n9,n10,n11 | 45 | 120 |

| n3,n4 | 45 | 180 |

| n5,n6,n7 | 45 | 240 |

| p1,p2,p5,p6,p10,p11 | 45 | 240 |

| p3,p4 | 45 | 360 |

| p7,p8,p9 | 45 | 480 |

4.1 | 基于仿真的提出全加器输入‐输出逻辑验证

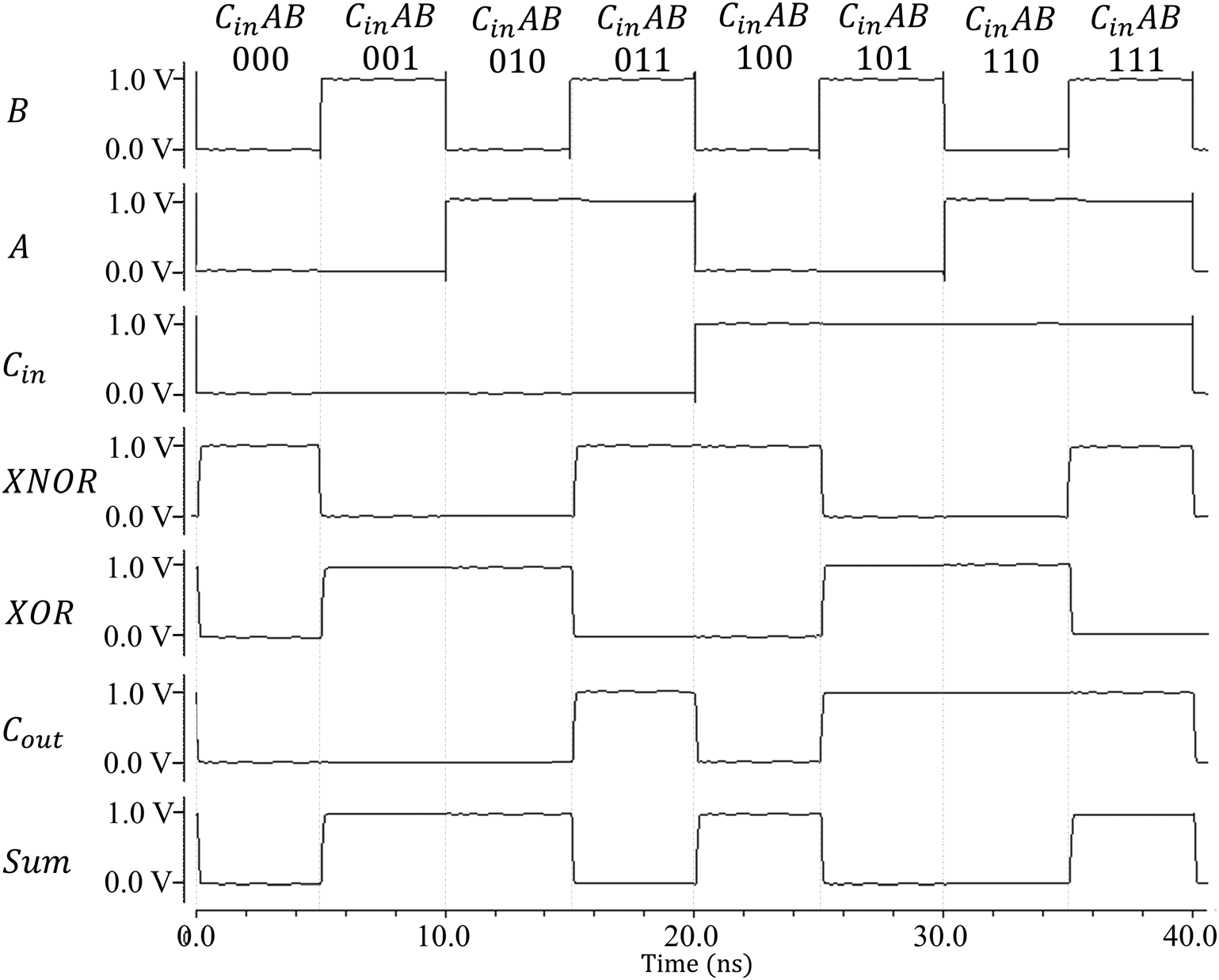

为了验证所提出的全加器设计的工作情况,使用Cadence工具绘制了包含所有可能逻辑信号组合的输入‐输出图。所得的仿真图如图4所示。仔细分析图4可以发现,所提出的全加器设计的输入‐输出组合符合全加器的逻辑原理。此外,可以看出输出信号(Cout和Vdd)的电压电平等于电源电压(1伏特)。因此,图4中的仿真结果证明了所提出的全加器电路提供了全摆幅输出。

| 表4 1位全加器性能分析 | ||||

|---|---|---|---|---|

| FA | 参考编号 | TC | 平均功率 (μW) | 传播延迟 (皮秒) |

| CCMOS | 7 | 28 | 1.28 | 60.3 |

| 巴塔查里亚 | 10 | 16 | 0.62 | 98.7 |

| Tung | 11 | 15 | 0.83 | 87.34 |

| 帕拉梅斯瓦拉 | 12 | 16 | 0.7 | 51.2 |

| 哈苏内 | 14 | 26 | 1.48 | 79.15 |

| 米尔扎伊 | 15 | 24 | 1.15 | 66 |

| 瓦拉沙尼 | 16 | 18 | 0.79 | 74.8 |

| 蒂鲁马拉塞蒂 | 17 | 16 | 0.65 | 83.34 |

| 萨纳帕拉 | 20 | 14 | 0.75 | 56.7 |

| 肖巴 | 21 | 22 | 1.06 | 42.8 |

| 提出 | ---- | 22 | 0.95 | 35.6 |

缩写:AP,平均功率;PD,传播延迟;PDP,功耗延迟积;TC,晶体管数量。

4.2 | 1位全加器单元的性能分析

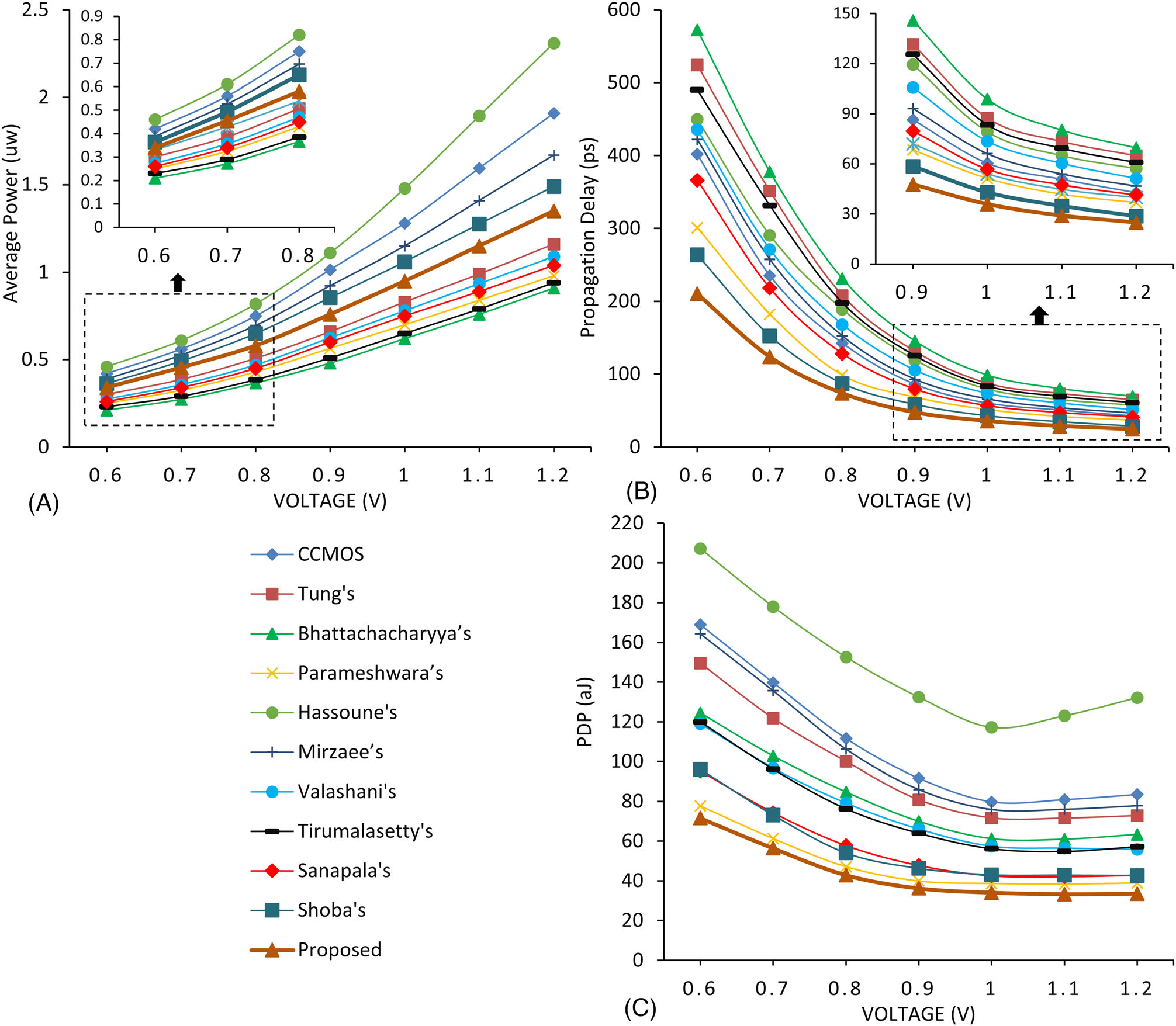

为了研究1位全加器单元的性能,首先将电源电压设置为1伏特。后布局仿真的结果记录在表4中。然后,通过将电源电压从0.6至1.2伏特变化,观察电源电压变化对全加器单元的影响。结果如图5所示。从表4和图5可以看出,所提出的基于异或‐同或的全加器单元在传播延迟和功耗延迟积方面表现出显著更好的性能。对于平均功率,与现有设计相比,所提出设计的性能可以认为是令人满意的。

实现所提出设计的卓越速度的主要因素是故意使用Cin信号作为p4和n4的栅极控制。p4, p3晶体管位于上升时间关键路径上,而n3, n4位于下降时间关键路径上。由于Cin是输入信号,Cin的计算完成时间远早于XOR‐XNOR电路计算其输出。因此,Cin将远早于XNOR和XOR信号出现在p3和n3的栅极之前导通p{v14}或n{v15}。因此,p3和n3能够提前获得其输入(在源极/漏极),一旦XNOR和XOR信号导通p3和n3,这些输入便可立即传递至输出端Cout。

4.3 | 全加器性能在宽字长结构中的表现

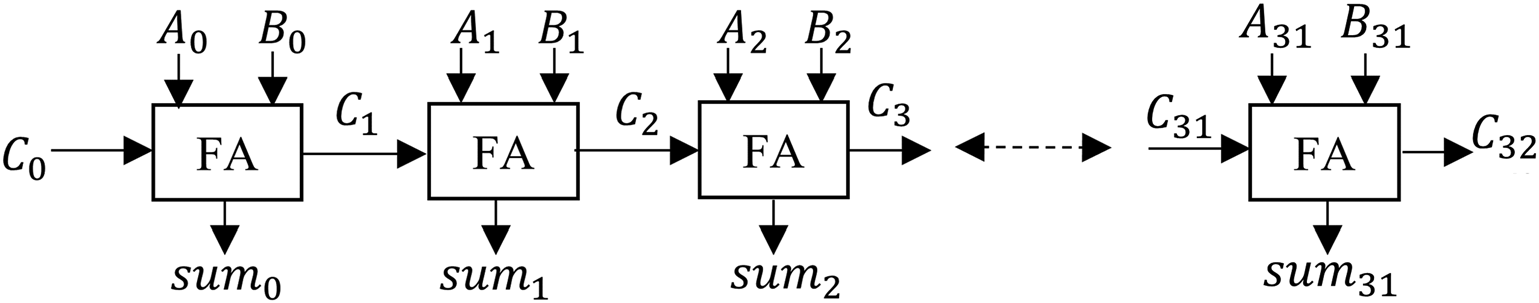

通过使用简单的行波进位加法器(RCA)方法将全加器扩展至32位,研究了全加器单元的可扩展性(图6)。在扩展全加器时,未使用任何中间电平恢复缓冲器。每个全加器在宽加法器结构中的性能如表5所示。研究发现,现有的10种全加器中仅有4种可以扩展到32位,其余7种只能扩展到8位。这归因于进位信号在经过多个全加器级联传播时出现的电压下降现象。CCMOS、哈苏内、和米尔扎伊的全加器在其进位生成电路的外部端子上附加了基于互补CMOS逻辑的单元。因此,进位电压在每一级全加器之后都能恢复至Vdd或地电平。out尽管所提出的全加器的Cout端子并非基于互补CMOS逻辑,但该设计仍表现出良好的可扩展性。从图6可以看出,在宽字长结构中,前一级的Cout信号作为后一级的Cin信号使用,而An和Bn信号在每一级都是以新鲜输入的形式加入。因此,如果同一进位信号需经过多级传递,则会经历电压下降,最终可能低于可识别为逻辑1的最低电压阈值。然而,从图2可以看出,在所提出的全加器中,Cin仅用作晶体管的栅极控制信号,无需在各级之间传递。出现在Cout端子上的信号仅为A、B、Vdd或Gnd。而在每一级中,A和B均为新的输入信号,Vdd和Gnd则不会发生电压衰减。由于相同的信号不会在多个全加器级中持续传播,因此所提出的全加器可扩展至32位宽字长加法器。肖巴的全加器的可扩展性也基于相同原理。

| 表5 全加器在宽字长结构中的性能 | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | | |......(内容过长,已省略部分表格内容)

| 全加器 | 参考编号 | 位数 | 4 | 8 | 16 | 32 | AP:平均功率 (μW) | PD:传播延迟(纳秒) | PDP:功耗延迟积(飞焦) | |||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| CCMOS | 7 | 4 | 4.84 | 9.41 | 18.59 | 36.94 | 0.245 | 0.501 | 1.009 | 2.203 | 1.185 | 4.714 | 18.767 | 74.951 | ||||

| 巴塔查里亚 | 10 | 4 | 2.62 | 4.77 | UTO | UTO | 0.718 | 3.411 | UTO | UTO | 1.881 | 16.27 | UTO | UTO | ||||

| Tung | 11 | 4 | 3.74 | 7.94 | UTO | UTO | 0.448 | 3.121 | UTO | UTO | 1.676 | 24.78 | UTO | UTO | ||||

| 帕拉梅斯瓦拉 | 12 | 4 | 2.88 | 5.93 | UTO | UTO | 0.298 | 1.58 | UTO | UTO | 0.858 | 9.369 | UTO | UTO | ||||

| 哈苏内 | 14 | 4 | 5.5 | 10.59 | 20.61 | 40.56 | 0.322 | 0.651 | 1.349 | 2.817 | 1.771 | 6.894 | 27.802 | 114.25 | ||||

| 米尔扎伊 | 15 | 4 | 4.81 | 9.73 | 19.58 | 40.48 | 0.269 | 0.562 | 1.129 | 2.264 | 1.294 | 5.468 | 22.106 | 91.646 | ||||

| 瓦拉沙尼 | 16 | 4 | 3.28 | 7.04 | UTO | UTO | 0.241 | 1.318 | UTO | UTO | 0.79 | 9.279 | UTO | UTO | ||||

| 蒂鲁马拉塞蒂 | 17 | 4 | 2.57 | 5.18 | UTO | UTO | 0.442 | 3.051 | UTO | UTO | 1.316 | 15.83 | UTO | UTO | ||||

| 萨纳帕拉 | 20 | 4 | 3.04 | 6.11 | UTO | UTO | 0.421 | 3.04 | UTO | UTO | 1.28 | 18.57 | UTO | UTO | ||||

| 肖巴 | 21 | 4 | 4.33 | 8.92 | 18.64 | 39.07 | 0.175 | 0.366 | 0.768 | 1.55 | 0.758 | 3.265 | 13.932 | 62.968 | ||||

| 提出 | —— | 4 | 3.72 | 7.15 | 14.03 | 30.84 | 0.147 | 0.319 | 0.661 | 1.333 | 0.547 | 2.281 | 9.274 | 41.109 |

缩写:UTO,无法操作。

表5中的结果证实,本文提出的全加器在平均功率、传播延迟和功耗延迟积方面取得了更好的结果,证明了其在字长加法器中的有效性。根据分析可以看出,尽管CCMOS全加器是最古老的全加器设计之一,但在32位扩展形式下表现相当出色。CCMOS全加器这种一致的性能使其成为应用最广泛的设计方法。

现有文献中的许多全加器使用电平恢复缓冲器来表明其全加器设计可扩展至多位。例如,巴塔查里亚等人在每4位运算后插入一个缓冲器,以应对电平下降问题。然而,这会增加额外的硬件和布局面积。此外,在进位路径中加入缓冲器会使电路变慢,因为这些缓冲器本身具有延迟。因此,在本研究中,我们未在中间阶段添加电平恢复缓冲器,以明确区分那些无需缓冲器即可扩展的设计与必须依赖缓冲器才能运行的设计。

5 | 结论

提出了一种基于XOR‐XNOR模块的混合全加器单元,采用PT、CCMOS和TG逻辑实现。通过对该1位全加器设计与10个现有全加器单元进行基于仿真的比较,验证并测试了其性能。为了测试可扩展性,所有全加器设计均扩展至32位。使用Cadence工具进行的仿真表明,在10个现有全加器设计中,仅有四个具备可扩展性。在单单元操作情况下,所提出的基于XOR‐XNOR的1位加法器在速度和功耗延迟积方面表现出更优的结果。在宽加法器中,所提设计在平均功率、传播延迟和功耗延迟积方面表现良好。本研究结果证明了所提出设计的有效性,是现有全加器单元的一个非常合适的替代方案。

基于XOR-XNOR的高速低功耗全加器

基于XOR-XNOR的高速低功耗全加器

1289

1289

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?