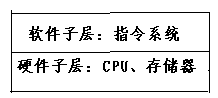

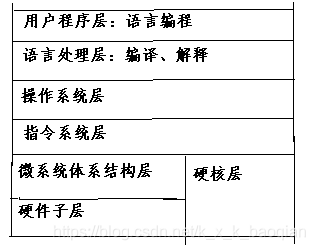

计算机分层模型:

最初阶段:两层

1.硬件层:逻辑电路:cpu、存储器

2.软件层:指令系统

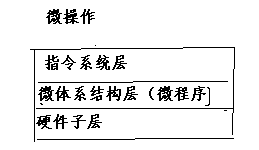

第二阶段:微程序设计 & RISC

1.微程序设计:三层 =》简化控制器,可实现复杂指令

一条指令可分解为多个微操作

微操作用微指令实现

多条微指令组成微程序实现指令

微程序存储在ROM中,逐条读出完成微操作、

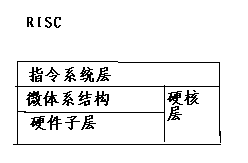

2.RISC:两层

二八定律:80%时间运行的是不到20%的简单指令;80%的任务是不到20%的电路完成的

所以为了提高性能

1.减少指令数量:一条复杂指令用多个简单指令替代

2.取消微程序,指令功能用硬核实现

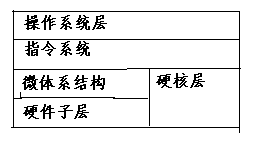

第三阶段:操作系统出现

操作系统负责管理硬件资源和用户作业,提供人机交互、多条用户命令和多种子程序调用接口,极大简化操作、管理的复杂性

第四阶段:编程语言(目前)

编程语言发展:

1.与硬件关联的机器指令:开关

2.基于符号的汇编、

3.面向过程的算法

4.面向对象的可视化编程语言

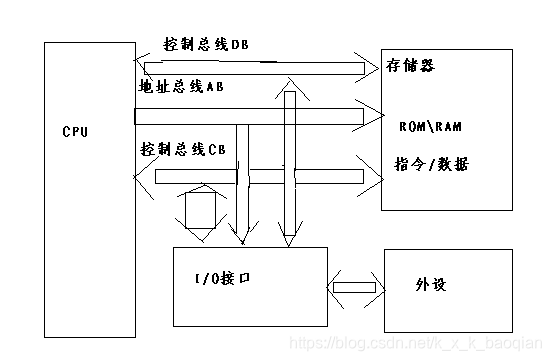

基于冯诺依曼架构的模型机:

cpu=运算器+控制器

存储器

1.以CPU为核心(现代逐渐以存储器为核心)

2.单总线系统:类似快慢车道不分,只有一条车道,所以慢

快:存储器;慢:外设

3.指令和数据使用一条总线(冯诺依曼架构的主要缺陷)

模型机存储器子系统

存储器的组织和地址:

计算机可访问最小存储单元:字节

每个字节有独一无二的地址

字节寻址存储器:按照字节组织存储器,连续地址对应连续字节单元

例如一个字有4字节,则连续字被给到n、n+4、n+8

每个字节一个地址

总线8位,存储器也是8位,则cpu访问存储器时总线一次可以传送一个字节数据

若总线宽度16/32/64位。cpu访问存储器时,希望一次可以传送一个完整的字或一部分,存储器应该如何连接,最大效率提高速度,不造成浪费

:分层

对准存放

一个字平分到各个存储器,到时候一起出

1.八位没有该问题

2.16位起始地址是2的倍数

3.32位起始地址是4的倍数

4.64位是8的倍数

对准存放不是必须的,但若是采用,存取一个字只需要一次总线操作

所以,有些计算机指令系统专门提供了对准存放指令

小端格式和大端格式

假设W由B3B2B1B0组成,B3最高字节,B0是最低字节,则存储W需要四个连续

内存单元

从上往下四个地址:m,m+1,m+2,m+3,m最小是尾部,m+3最大是头部

小端格式:高位高地址,B0123从上往下

大端格式:B3210从上往下

若采用对等存放,则m是整个字的地址

存储器操作

读入(read)和写入(write)

读:

将一个指定存储单元的内容读出并传输到cpu中,之后存储单元的内容保持不变

过程:CPU发送地址信号和读命令,被选中单元中的数据被读出到DB上,CPU采样数据并存入内部寄存器

写:

cpu向指定单元传输数据,并覆盖目的单元原有内容

过程:CPU通过AB,DB和CB分别发送地址、数据和写命令,DB上的数据被写入到选中单元

连续数据读写:只需要在第一次读写时发送地址

存储器的分级:

对存储器的要求:速度快、容量大、成本低

解决办法:分级存储结构

1.外存满足大容量、低成本、非易失

2.DRAM

3.高速缓存:速度快

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?