描述

题目描述:

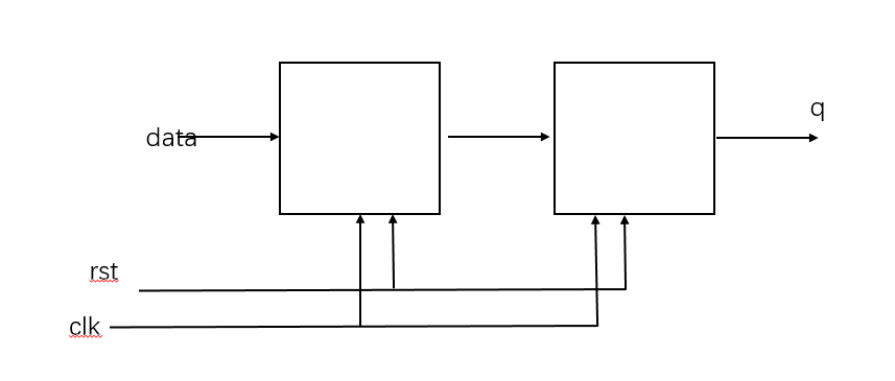

用verilog实现两个串联的异步复位的T触发器的逻辑,结构如图:

信号示意图:

波形示意图:

输入描述:

输入信号 data, clk, rst

类型 wire

在testbench中,clk为周期5ns的时钟,rst为低电平复位

输出描述:

输出信号 q

类型 reg

解题分析:

·T触发器是进入的值为1的时候,寄存的值发生翻转;

·注意异步复位

·需要注意寄存器翻转的逻辑,第二寄存器是否翻转取决于第一个寄存器是否为1,前者输出情况有三种:在data输入控制为1下从0到1到0不断翻转,data为0锁在1,data为0锁在0

T触发器的特性方程

Qn+1 = T Qn ' +T ' Qn = T⊕Qn

(其中Qn为现态,Qn+1为次态)

T触发器的特性表

T触发器的结构为:

代码如下:

`timescale 1ns/1ns

module Tff_2 (

input wire data, clk, rst,

output reg q

);

//*************code***********//

reg q1;

always @(posedge clk or negedge rst)

begin

if(!rst)

q1 <= 0;

else

begin

if(data)

q1 <= ~q1;

else

q1 <= q1;

end

end

always @(posedge clk or negedge rst)

begin

if(!rst)

q <= 0;

else

begin

if(q1)

q <= ~q;

else

q <= q;

end

end

//*************code***********//

endmodule波形图如图所示:

本文详细描述了如何使用Verilog语言设计并实现一个由两个串联的异步复位T触发器构成的电路,包括输入信号、输出逻辑分析和代码实现,同时提供了波形图以展示工作状态。

本文详细描述了如何使用Verilog语言设计并实现一个由两个串联的异步复位T触发器构成的电路,包括输入信号、输出逻辑分析和代码实现,同时提供了波形图以展示工作状态。

481

481

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?