问题: 板子的网卡在PL侧,需要使用GMII - TO - RGMII接口的IP做转换。导致开发自己的bit文件,会出现timing 差,编译时间长,甚至GMII timing fail,从而网络连接异常。

解决思路: 把PHY 降低频率到百兆网络 去掉 GMII - TO - RGMII接口的IP 。

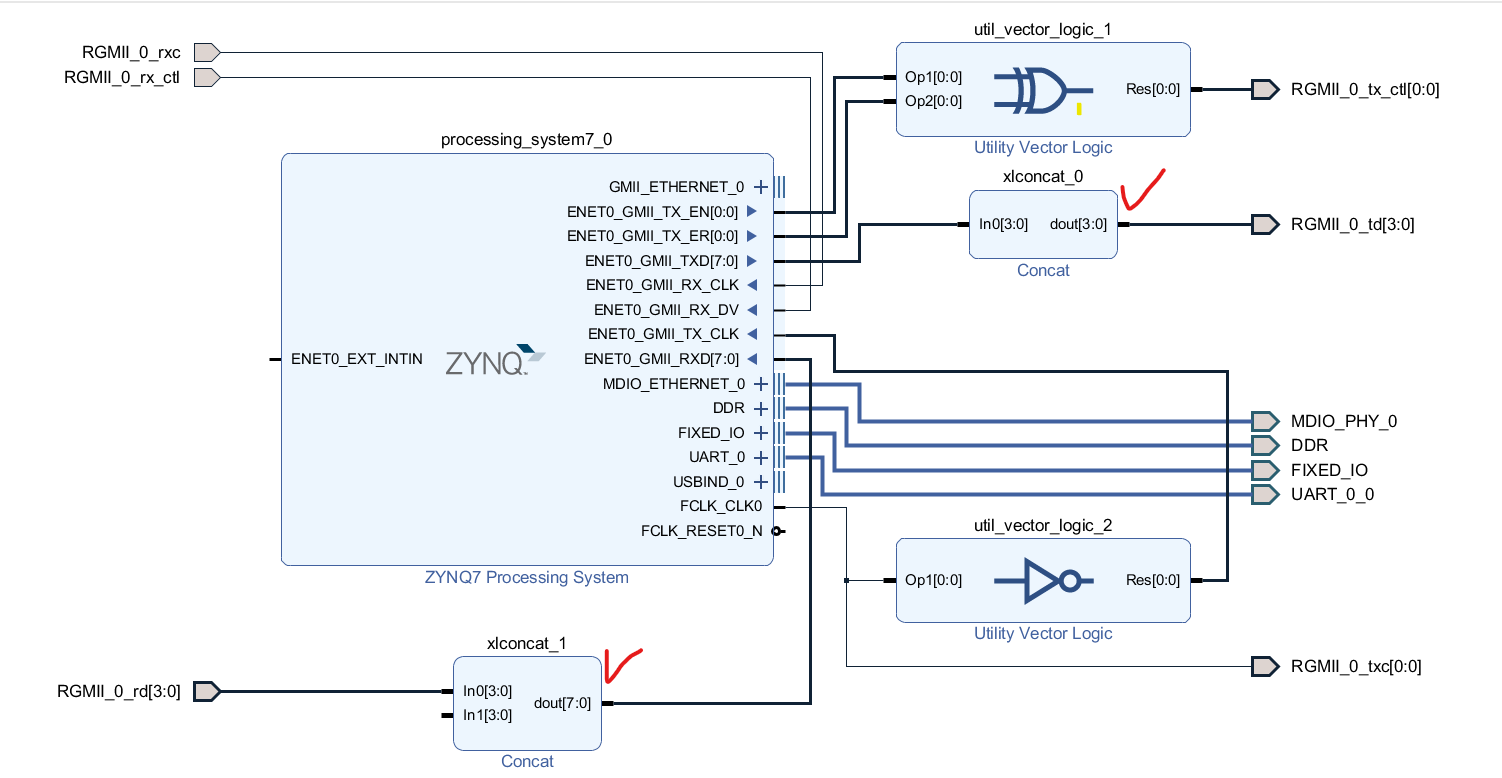

具体实现: 注意图中打勾必选,另外两个时钟反向已经tx_ctl 可能没啥用。

FCLK_CLK0 需要配置成25Mhz

如图连接,完成综合即可解决此问题。

1. 串口输入: sudo ethtool -s eth0 speed 100 duplex full autoneg off

2. jnotebook 里面就可以正常使用ol = Overlay('./try6.bit')

project 可以 PYNQ 开发 章节二 Vivado 硬件工程搭建 (Smart Zynq SP & SL版) – Hello FPGA

原始版本上改。

3352

3352

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?