在PCB设计中,信号传输的稳定性至关重要。然而,不同信号线之间可能会因为电磁场的相互作用而产生干扰,这种现象被称为串扰。串扰不仅影响信号质量,还可能导致数据传输错误,是高速传输中不可忽视的问题。

串扰的成因

串扰通常发生在两个信号路径过于接近时,它们的电磁场相互干扰。这种现象在高速数据传输中尤为明显,因为高速信号的电磁场更强,更容易相互干扰。

串扰的影响因素

- 元件封装:随着电子设备向小型化发展,PCB上的元件封装越来越小,引脚间距也随之减小,增加了电容耦合的可能性。

- 布线设计:布线过于密集或不当,特别是在焊盘附近或不同层之间的布线,都可能增加串扰的风险。

Altium Designer中的串扰抑制技术

虽然串扰是一个挑战,但Altium Designer提供了多种工具和技术来帮助设计师减少串扰的影响。

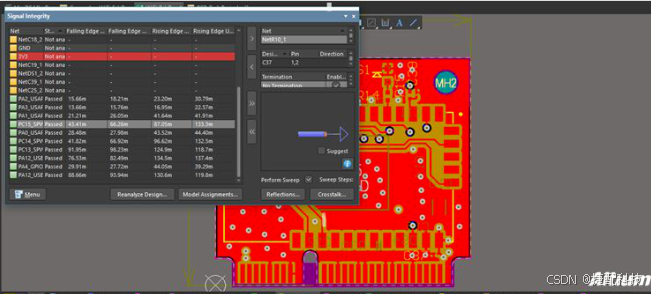

- 信号完整性分析:Altium Designer的信号完整性分析工具可以帮助设计师识别潜在的串扰问题,包括信号的上升时间和下降时间,以及终端匹配方案。

- 布线间距:增加不同网络布线之间的间距是减少串扰的有效方法。Altium Designer的高亮显示功能可以帮助设计师轻松调整布线间距。

- 并行走线长度:对于需要匹配的信号路径,如差分对,应确保铜重量、走线宽度和长度一致。对于不同信号的并行走线,应尽量减少它们的并行长度或使它们垂直。

- 地平面隔离:在信号层之间插入接地平面可以提高隔离度,减少不同层之间的串扰。

串扰是PCB设计中一个不可避免的问题,但通过合理的设计和Altium Designer提供的工具,可以有效地抑制串扰。关键在于识别串扰的来源,并采取适当的措施来减少其影响。通过信号完整性分析,设计师可以诊断电路板的信号问题,并选择最佳的消除技术来保证信号传输的稳定性。

590

590

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?