文章目录

1.同步时钟

数字设计中,一般认为,频率相同或频率比为整数倍、且相位相同或相位差固定的两个时钟为同步时钟。

或者理解为,时钟同源且频率比为整数倍的两个时钟为同步时钟。

同源同频同相位

同源同频不同相位

同源不同频但存在整数倍分频比

2.异步时钟

工作在异步时钟下的两个模块进行数据交互时,由于时钟相位关系不可控制,很容易导致建立时间和保持时间 violation。以下 3 种情况下的时钟可以认为是异步的。

不同源

同源但频率比不是整数倍

同源虽频率比为整数倍但不满足时序要求

当信号从快时钟域传递到慢时钟域时,但如果信号在快时钟域翻转速率过快,慢时钟域可能不会安全的采集到从快时钟域传来的信号,这也可以认为是异步问题。

3.跨时钟域传输:慢到快

延迟打拍法

最常用的同步方法是双级触发器缓存法,俗称延迟打拍法。异步信号从一个时钟域进入另一个时钟域之前,将该信号用两级触发器连续缓存两次,可有效降低因为时序不满足而导致的亚稳态问题。电路示意图如下。

一般设计中使用两级触发器进行缓存即可满足设计时序需求。大量实验表明,三级触发器缓存可解决 99% 以上的此类异步时序问题。

双寄存器并不能消除亚稳态,它只是减少了出现亚稳态的概率,将其减小到了一个几乎可以忽略不计的程度。触发器进入亚稳态的时间可以用参数 MTBF(Mean Time Between Failures,平均故障间隔时间)来描述,MTBF 即触发器采样失败的时间间隔,其计算公式为:

延迟采样法

此方法主要针对多位宽的数据传输。

例如当两个异步时钟频率比为 5 时,可以先用延迟打拍的方法对数据使能信号进行 2 级打拍缓存,然后再在快时钟域对慢时钟域的数据信号进行采集。

该方法的基本思想是保证信号被安全采集的时刻,而不用同步多位宽的数据信号,可节省部分硬件资源。

4.跨时钟域传输:快到慢

https://www.runoob.com/w3cnote/verilog-sync.html

电平信号同步

同步逻辑设计中,电平信号是指长时间保持不变的信号。保持不变的时间限定是相对于慢时钟而言的。只要快时钟的信号保持高电平或低电平的时间足够长,以至于能被慢时钟在满足时序约束的条件下采集到,就可以认为该信号为电平信号。

既然电平信号能够被安全的采集到,所以从快时钟域到慢时钟域的电平信号也采用延迟打拍的方法做同步。

脉冲信号同步

同步逻辑设计中,脉冲信号是指从快时钟域输出的有效宽度小于慢时钟周期的信号。如果慢时钟域直接去采集这种窄脉冲信号,有可能会漏掉。

可通过"握手传输"的方法进行同步。

多位宽数据同步

解决此类异步问题的常用方法是采用异步 FIFO (First In First Out)。

FIFO

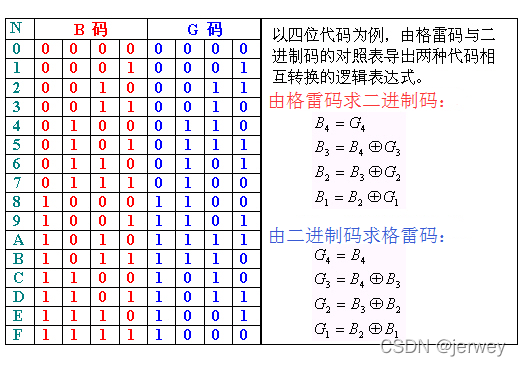

grey码

竞争冒险

组合逻辑电路中,同一信号经不同的路径传输后,到达电路中某一会合点的时间有先有后,这种现象称为逻辑竞争,而因此产生输出干扰脉冲的现象称为冒险。

如果一个组合逻辑电路中有"毛刺"出现,就说明该电路存在冒险。

单bit和多bit传输

CDC(Clock Domain Conversion)跨时钟域分单bit和多bit传输,其中:

1. 单bit(慢时钟域到快时钟域)

目标时钟频率必须是源时钟频率1.5倍或者以上,才能算慢时钟到快时钟的CDC.

用快时钟打两拍(同步器),直接采一拍大概率也是没问题的,两拍的主要目的是消除亚稳态;

其中:

(1)为了更长的平均无故障时间 MTBF( Mean Time Between Failures),需要配合一个 ASYNC_REG 的约束,把用作简单同步器的多个寄存器放入同一个 SLICE,以降低走线延时的不一致和不确定性。

(* ASYNC_REG = "TRUE" *) reg rst_reg_0;

(* ASYNC_REG = "TRUE" *) reg rst_reg_1;

(2)或者:直接在约束文件里进行约束

set_property ASYNC_REG TRUE [get_cells [list rst_reg_0 rst_reg_1]]

2. 单bit(快时钟域到慢时钟域)

握手(脉冲展宽)、异步FIFO、异步双口RAM;快时钟域的信号脉宽较窄,慢时钟域不一定能采到,可以通过握手机制让窄脉冲展宽,慢时钟域采集到信号后再“告诉”快时钟域已经采集到信号,确保能采集到;

3. 多bit跨时钟域

在两个时钟域之间传递多个信号,简单的同步器已经不能满足要求。

异步FIFO(or异步双口RAM)、握手、格雷码、简单的两级寄存器同步器;

将这4种设计方案的应用场景总结如下:

- 异步FIFO

源时钟域每个cycle都要传输新的数据

源时钟域的数据被buffer起来了 - 格雷码

数据是一个counter,而且是2^N循环周期 - 握手

目标时钟域要求必须在同一cycle内采样所有的数据 - 多个信号合并

- 两级寄存器同步器

~~ 目标时钟域不要求必须在同一cycle内采样所有的数据 ~~

(1)使用异步FIFO的IP

实际上是用 FPGA 内部的 BRAM 来搭建,所有的控制逻辑都在 BRAM 内部,是推荐的 FIFO 实现方式。

时序约束简单,进行时序例外约束,只需要 set_clock_groups 将读写时钟约束为异步时钟组即可,简单高效。

set_property -asynchronous -group [get_clocks write_clock] \

-group [get_clocks read_clock]

(2)自己写外部控制逻辑的FIFO

格雷码做异步 FIFO 的跨时钟域处理,计数器和读写控制逻辑在 BRAM 或者 RAM 的外部,除了代码的合理设计以外,还需要进行额外的时序例外约束,不能简单使用 set_clock_groups 约束异步时钟组,还需要考虑外部的读写逻辑的约束。

Xilinx建议这里设置 set_max_delay 来约束跨时钟域路径,约束的原则是:最大路径延时等于或者略小于目的时钟的一个周期。

写逻辑从cell1到cell2的约束中,cell2的驱动时钟周期为5,如下所示,读逻辑约束进行相应约束。

set_max_delay 5 –from [get_cells cell1] –to [get_cells cell2] –datapath_only

方法

. 异步FIFO

https://zhuanlan.zhihu.com/p/151407399

. 握手

握手指的是两个设备之间通信的一种方式,用来通信的信号就是握手信号。最简单的握手信号是 valid 和 ready,也可以叫 request 和 grant。

握手控制,可以确保数据的正确传输,不会丢失。跨时钟域的握手设计就是利用握手控制这种优势,从而避免因为跨时钟域引起的数据传输错误。

单比特跨时钟域握手

多比特跨时钟域握手

https://zhuanlan.zhihu.com/p/157887580

grey码

https://zhuanlan.zhihu.com/p/149861619

电平信号 (XPM_CDC_SINGLE)

脉冲信号 (XPM_CDC_PULSE)

过采样

https://zhuanlan.zhihu.com/p/168760544

弹性Buffer

应用需求是数据必须不断流入然后流出FIFO呢?这意味着既不能反压前级也不能通知后级。

弹性Buffer便是应用在这种需求下的一种跨时钟域的设计方法。

背景

在起初的PCI总线设计中,采用的是同步时序结构,即发送端和接收端使用同步时钟,发送端只需要发送数据,接收端正常采样即可。这种同步结构要求时钟到达发送端和接收端的时间精确相同,特别是对总线接口pin-to-pin的skew要求极高。随着总线频率的提升,对skew的要求也越来越高,使得时钟网络布线越来越困难。

因此,当前的很多高速接口设计,如PCIe,Ethernet都是采用了源同步(source-synchronous)时序结构,即发送端同时发送时钟和数据,接收端需要从接收到的数据中恢复出数据的采样时钟,用该时钟来采样收到的数据。这种设计方式虽然避免了上述的问题,但是也带来了新的问题,即跨时钟域的问题,因为这种设计结构下一般会有两个时钟域,即Recovered Clock Domain 和 Local Clock Domain。一般来说,Recovered Clock 和 Local Clock 之间频率只有些微的差别,弹性Buffer便是用来解决这种情况下的跨时钟域数据传输问题的。如图1所示:

https://zhuanlan.zhihu.com/p/159452714

总结

CDC(Clock Domain Conversion)跨时钟域分单bit和多bit传输,其中:

- 单bit(慢时钟域到快时钟域):用快时钟打两拍,直接采一拍大概率也是没问题的,两拍的主要目的是消除亚稳态;

- 单bit(快时钟域到慢时钟域):握手、异步FIFO、异步双口RAM;快时钟域的信号脉宽较窄,慢时钟域不一定能采到,可以通过握手机制让窄脉冲展宽,慢时钟域采集到信号后再“告诉”快时钟域已经采集到信号,确保能采集到;

- 多bit:异步FIFO、异步双口RAM、握手、格雷码;

跨时钟域同步,为什么两级寄存器结构能够降低亚稳态?

https://www.zhihu.com/question/43571892/answer/95991243

FPGA中亚稳态——让你无处可逃

https://www.cnblogs.com/linjie-swust/archive/2012/01/07/ywt.html

《Clock Domain Crossing》 翻译与理解(5)多信号跨时钟域传输

https://zhuanlan.zhihu.com/p/359329393

芯片设计进阶之路—亚稳态和同步器

https://zhuanlan.zhihu.com/p/111549994

CDC跨时钟域处理及相应的时序约束【set_clock_groups】【set_max_delay】

https://zhuanlan.zhihu.com/p/354965131

《Clock Domain Crossing (CDC) Design & Verification Techniques Using SystemVerilog》

Clock Domain Crossing (CDC) Design & Verification Techniques Using SystemVerilog》进行翻译和基于自我理解的分析阐述,本文介绍多信号跨时钟域传输。

https://zhuanlan.zhihu.com/p/359329393

本文详细探讨了同步时钟与异步时钟的概念,并重点讲述了跨时钟域传输的策略,包括慢到快和快到慢的数据同步方法,如延迟打拍、延迟采样和电平信号同步等。同时,介绍了竞争冒险和如何处理多位宽数据同步,以及各种跨时钟域设计中的关键技术,如异步FIFO、握手协议和格雷码。

本文详细探讨了同步时钟与异步时钟的概念,并重点讲述了跨时钟域传输的策略,包括慢到快和快到慢的数据同步方法,如延迟打拍、延迟采样和电平信号同步等。同时,介绍了竞争冒险和如何处理多位宽数据同步,以及各种跨时钟域设计中的关键技术,如异步FIFO、握手协议和格雷码。

3789

3789

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?