本文主要目的是从数字IC设计的角度来了解DFT设计。

1. 基本概念

DFT测试的目的:把生产制造过程中有问题的芯片筛选出来。

Aotumatic Test Equipment(ATE)是芯片测试仪器,可以存储pattern并将其加载到芯片中,并且可以检测芯片输出,判断是否有故障。

基于测试对象的不同,芯片测试分为CP(chip probing)和FT(final test)。CP是对未封装的芯片,也就是晶圆进行测试;FT是对已经封装好的芯片进行测试。

一般而言,DFT设计在前端产生gate level netlist之后进行DFT insertion。

2. 错误模型

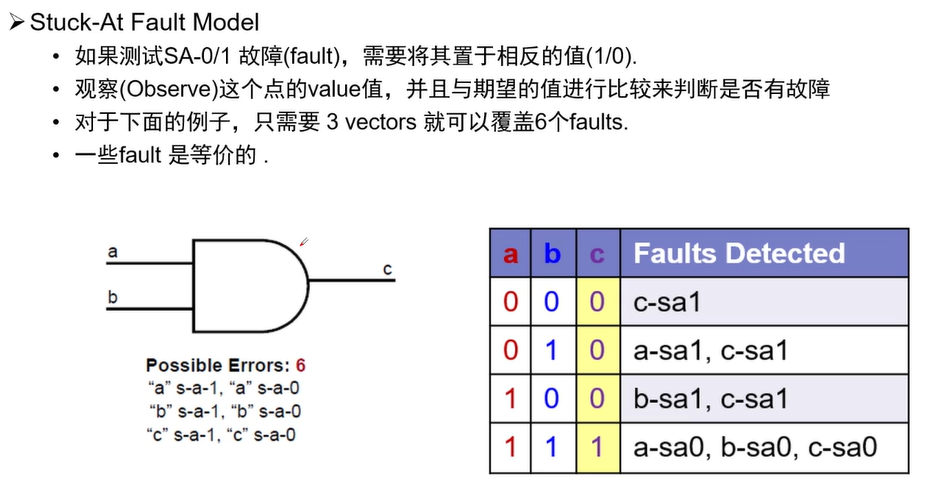

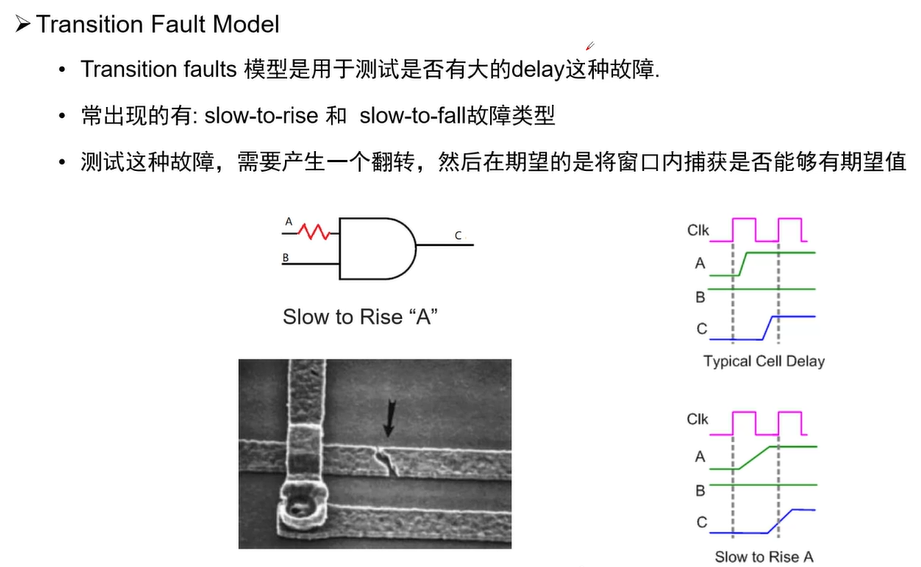

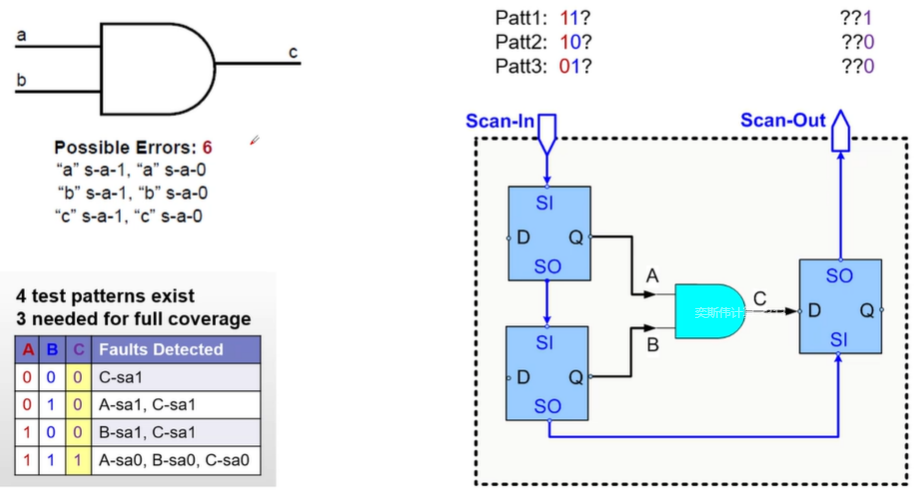

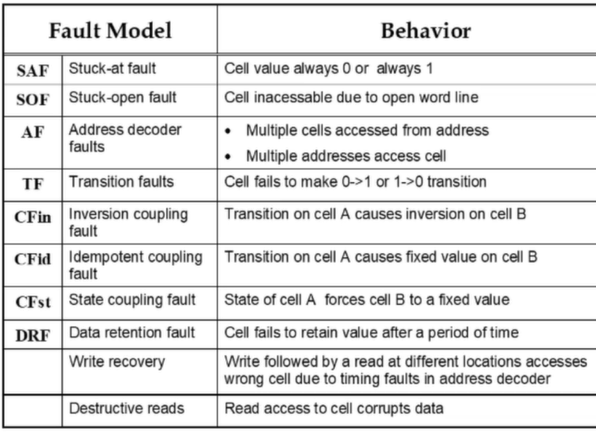

绝大多数问题都是stuck-at和transition fault。

2. SCAN chain

用于测试数字逻辑,包括时序逻辑和组合逻辑。

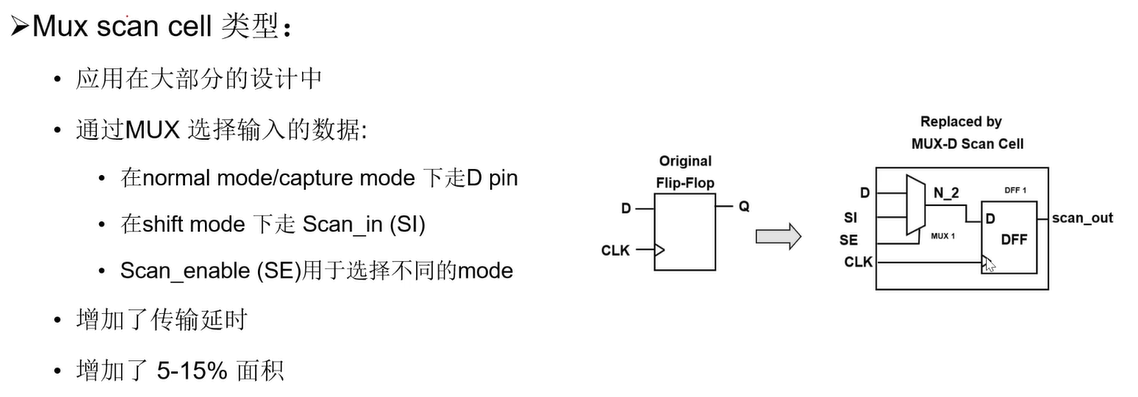

使用带mux的cell替换触发器(工艺单元库里会自带),这个在综合阶段选择对应的cell就可以了。

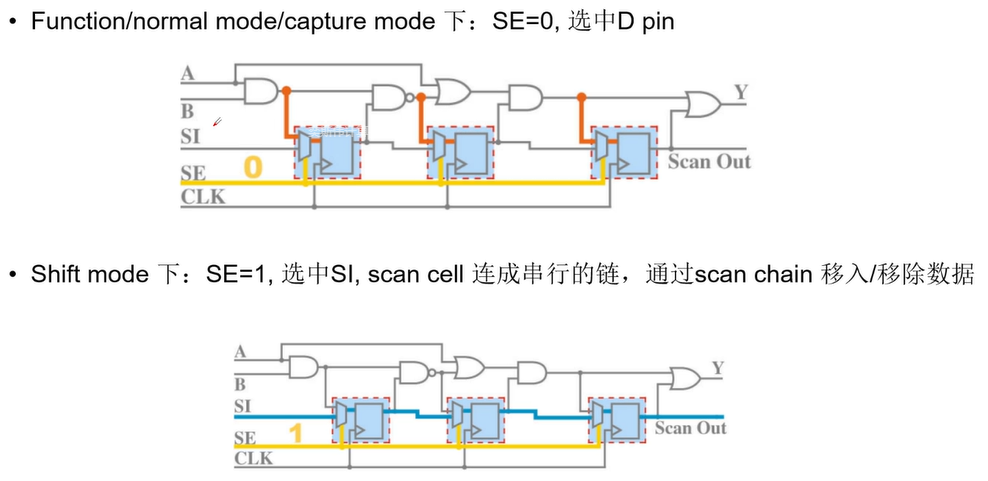

scan chain电路示例:(chain具体怎么连接由DFT完成,数字设计无需关心)

单个模块的输出信号用寄存器打拍有利于提升组合逻辑覆盖率。

2.1 DC测试

DC测试用于测试stuck-at故障。

在patt1测试中,在SE为1时,给scan chain中第1个和第2个寄存器加载的值为1、1,分别给到与门的A和B。期望的测试结果:在SE为0时,下一个clock上升沿,SO的输出为1。同理,patt2测试中加载值为10,期望输出为0。

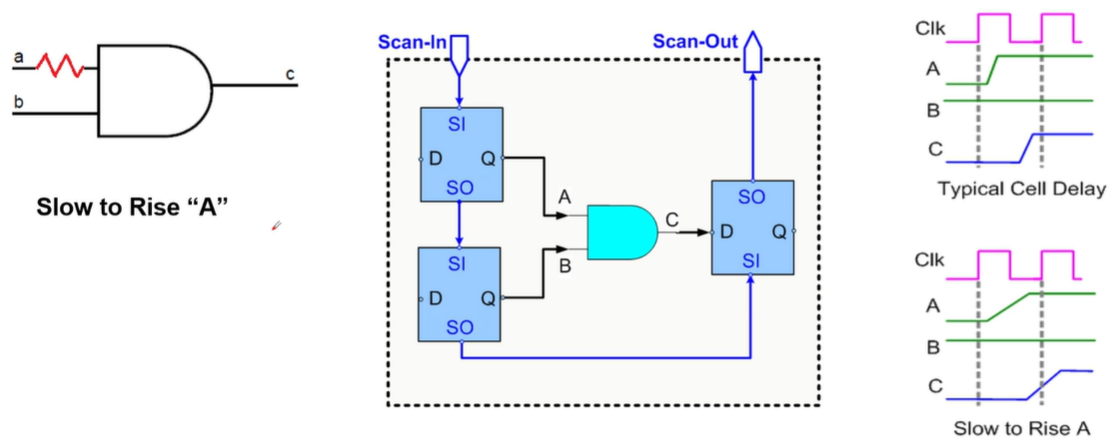

2.2 AC测试

AC测试用于测试transition故障。

用下图的slow to rise A举例:在SE为1时,给delay chain第1、2、3个寄存器加载的值为0、1、0;将第一个寄存器的D端加载为1(可能来自别的寄存器或者组合逻辑)。然后将SE配置为0,在接下来的第1个时钟上升沿,A由0跳变成1;第2个上升沿,与门的C端被第3个寄存器采样。如果SO在第2个上升沿之后可以输出1,则说明C的值在1个clock周期之内发生了变化且被成功采样,没有transition故障。

2.3 ATPG

Automatic Test Pattern Generation,自动化产生测试向量。指由EDA工具自动生成test pattern。

ATPG的目的是产生获得一个test coverage的test pattern,需要已经完成scan insertion的工作。

3. 边界扫描(Boundary Scan Design)

用于测试管脚PAD。

可以简单理解为通过boundary-scan cell把芯片需要测试的PAD的输入输出做成一个chain,然后通过JTAG进行boundary scan测试。

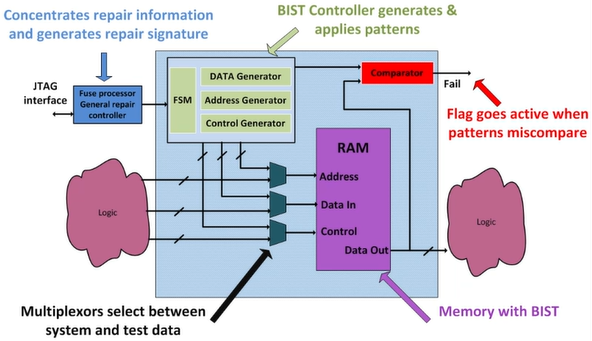

4. MBIST

用于测试存储器。

片上存储包括SRAM和ROM。Foundary/EDA工具厂商会提供compiler工具。

Memory的故障模型:

MBIST的过程:通过JTAG控制BIST控制的FSM来实现算法(不同的算法会覆盖不同的错误类型,复杂度也不一样),对RAM进行测试。

5. Hard macro Testing

测试模拟IP。

6. 数字设计可以做什么?

在RTL设计阶段,这些工作可以提前加入到RTL中:(具体需要和DFT工程师沟通,不同的人需求可能不一样)

6.1 IO

1. 增加DFT_PAD:芯片上电复位之后,该PAD需要定义为输入,实现ATE对测试模式的外部可控。测试模式锁定后,可以释放该端口为function IO。

2. IO的控制信号(如DS/PU/PD)以bus的类型拉到TCU。

6.2 时钟

1. PLL:在DFT模式下,所有PLL信号可由DFT控制。

2. OCC(On-chip Clock Controller):用于在ATE对芯片做ATPG测试时切换ate clock和function clock。对于大型SOC,在数字设计时,可以在CGU内每个时钟输出前都插入一个名为occ的buffer,方便DFT工程师后期进行替换。OCC要避免级联。

3. Hard IP的输出时钟,需要加mux来bypass时钟,需要额外添加测试的DIV等。

6.3 复位

1. 异步复位/置位信号需要被DFT控制信号接管。

2. 时钟生成部分电路(div、clock_mux等)的resetn用dft_crg_rst_n可控,并拉到TCU。

3. 逻辑部分的resetn用dft_lgc_rst_n可控,并拉到TCU。

6.4 模拟IP

模拟IP的所有输入在DFT模式下都应该tie成固定值,防止IP在DFT测试时工作,影响IDDQ测试结果。也可能影响IP硬件寿命。

6.6 dont touch cell list

需要提供dont touch cell list给DFT,避免这些cell在DFT阶段被优化。

3023

3023

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?