这个系列主要用来记录DDR相关的特性,timing,interface,device。

坚持持续更新,作为一个工作学习过程中的输出渠道。可能会有不完整甚至不正确的地方,还请各位指出

SDRAM

- SDRAM 全称为 Synchronous Dynamic Random Access Memory, 即同步动态随机存储器。与之类似的还有SRAM(Static Random Access Memory),DRAM。相较于SRAM,SDRAM成本更低,速度稍慢,而且需要不断的refresh来保持cell中的状态,但是成本以及封装面积的优势让它能够在实际生产中得到广泛的应用。

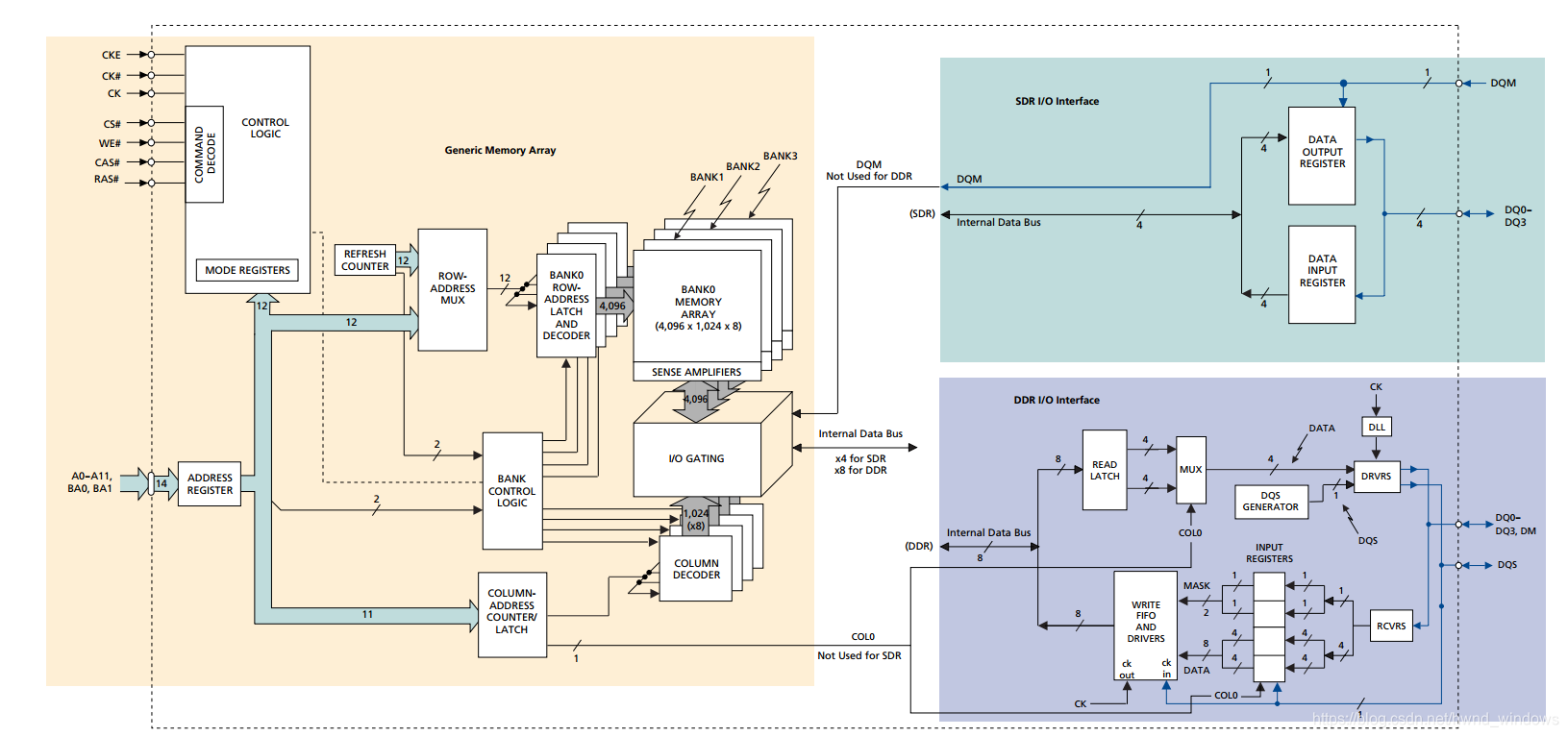

- SDRAM的组成(这是一个大概的示意图,来源比较老了,TN4605)

左侧接口:CKE CK CS等都是传输command, 片选,时钟使能等信号,A0-A11是传输地址的信号,BA0则是bank选择的信号

右侧接口:DQ, DQS则是数据传输信号和数据传输时钟信号。

control logic: 主要用来解析command,对于不同的command(refresh,activate,read/write)执行不同的后续操作。

address:地址解析,row/bank/column地址分别输入到对于的解析器,进行active。

refresh counter:刷新计数器,sdram需要维持一定的刷新率才能够保住数据不丢失,这个计数器便是用来控制内部刷新逻辑的,上次刷到了哪一行,这次接着往下刷。

Bank control logic:BANK控制逻辑,BANK是precharge和act

本文档记录了DDR相关特性,包括SDRAM的工作原理、组成及接口信号。SDRAM作为成本较低且广泛应用的内存类型,其需要不断刷新以保持数据。内容涵盖clock信号、command解析、地址总线、bank控制逻辑以及内存阵列等核心概念。

本文档记录了DDR相关特性,包括SDRAM的工作原理、组成及接口信号。SDRAM作为成本较低且广泛应用的内存类型,其需要不断刷新以保持数据。内容涵盖clock信号、command解析、地址总线、bank控制逻辑以及内存阵列等核心概念。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1852

1852

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?