本篇主要分享起源与笔者在项目中,生成了CRC模型后,出现了CRC实际值和参考值不一致的情况。笔者查找了一些相关资料后,对其解决过程进行了一点记录。

关于CRC的原理,个人在学习的过程中讲的通俗易懂的如下:

https://mp.weixin.qq.com/s/RNHLZGPD9Ysbxb1FNDn6EA

另外通过查找表讲解CRC的实现方式,也比较通俗。

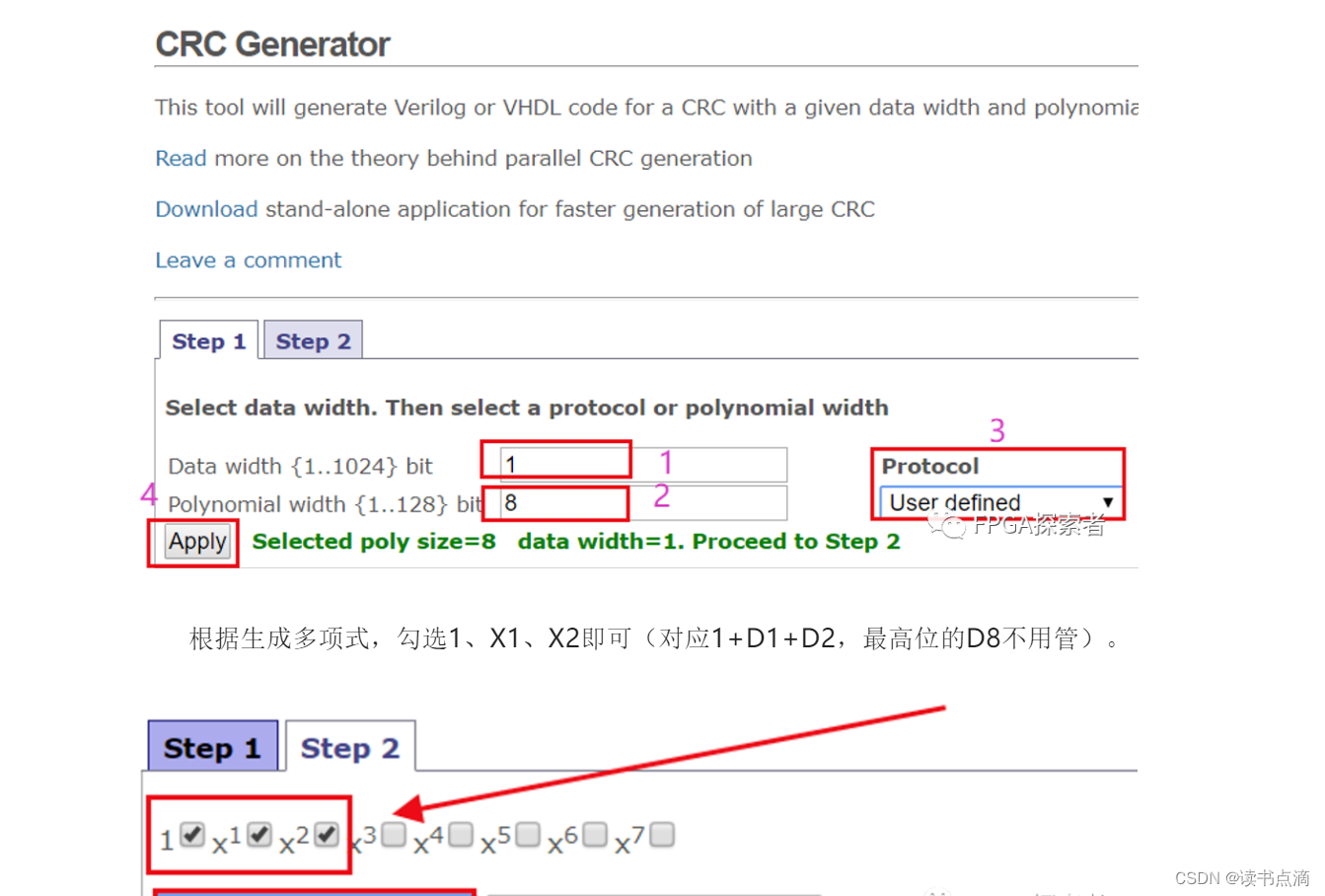

关于如何生成CRC的verilog 模型可以通过网站生成,也可以通过脚本来进行生成。

1、网站可以通过以下网站:

http://outputlogic.com/?page_id=321

具体使用参考以下博文:FPGA手撕代码——CRC校验码的多种Verilog实现方式

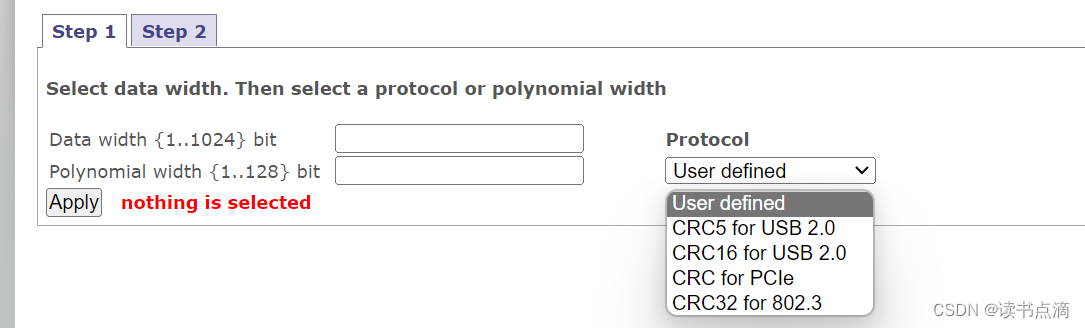

其中想说一点的是,下图Protocol下拉不同选项为CRC的类型,选User Define(用户定义)最通用,其他的类型含义,参考以下博文:Verilog数字系统基础设计-CRC

另外一种通过脚本生成CRC的模型可以参考以下链接:任意多项式,任意位宽crc verilog代码自动生成perl脚本 - 腾讯云开发者社区-腾讯云 (tencent.com)

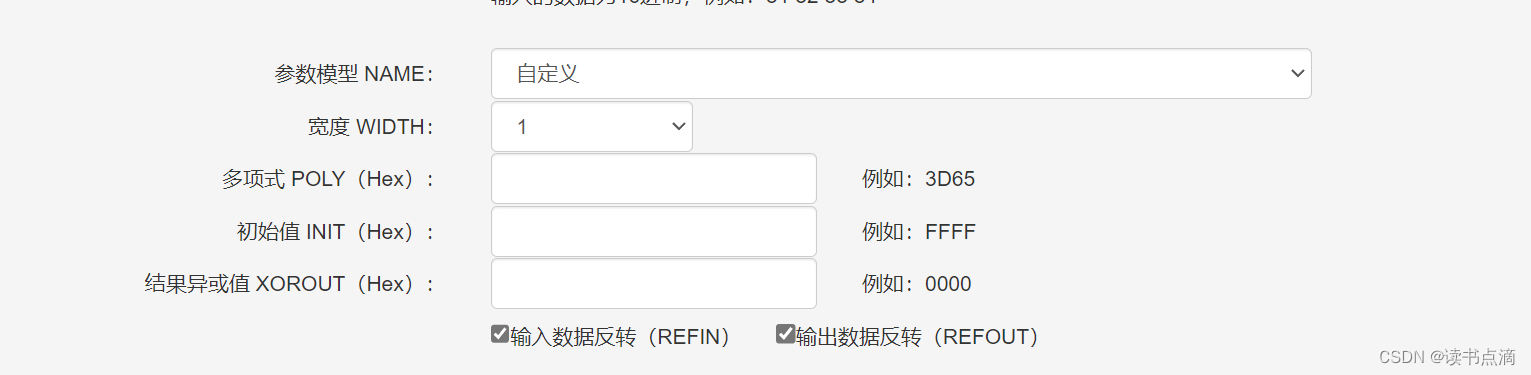

笔者在实际项目中发现了,选取同样的多项式和同样的输入数据,实际项目中计算的值,与通过生成的verilog仿真模型计算出来的值是不一样的,但是下面网站中在线计算CRC的计算值是一样的。

这个到底是什么原因呢?我在下面博客中找到了答案。

CRC的计算过程你真的搞明白了吗??_EmbededCoder的博客-优快云博客_crc计算

CRC校验值的差异关键在于输入数据和输出数据是否反转,输入数据反转和输出数据反转具体解释参考上述博文。通过CRC模型生成的verilog仿真代码对其输入和输出值是不会经过反转处理的,而我实际项目中代码是经过输入和输出值反转处理的。所以我们在测试激励中输入数据在输入CRC仿真模型的之前要人为额外的对输入输出进行处理,同时也要额外对CRC仿真模型的输出结果进行额外处理。

412

412

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?