提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

前言

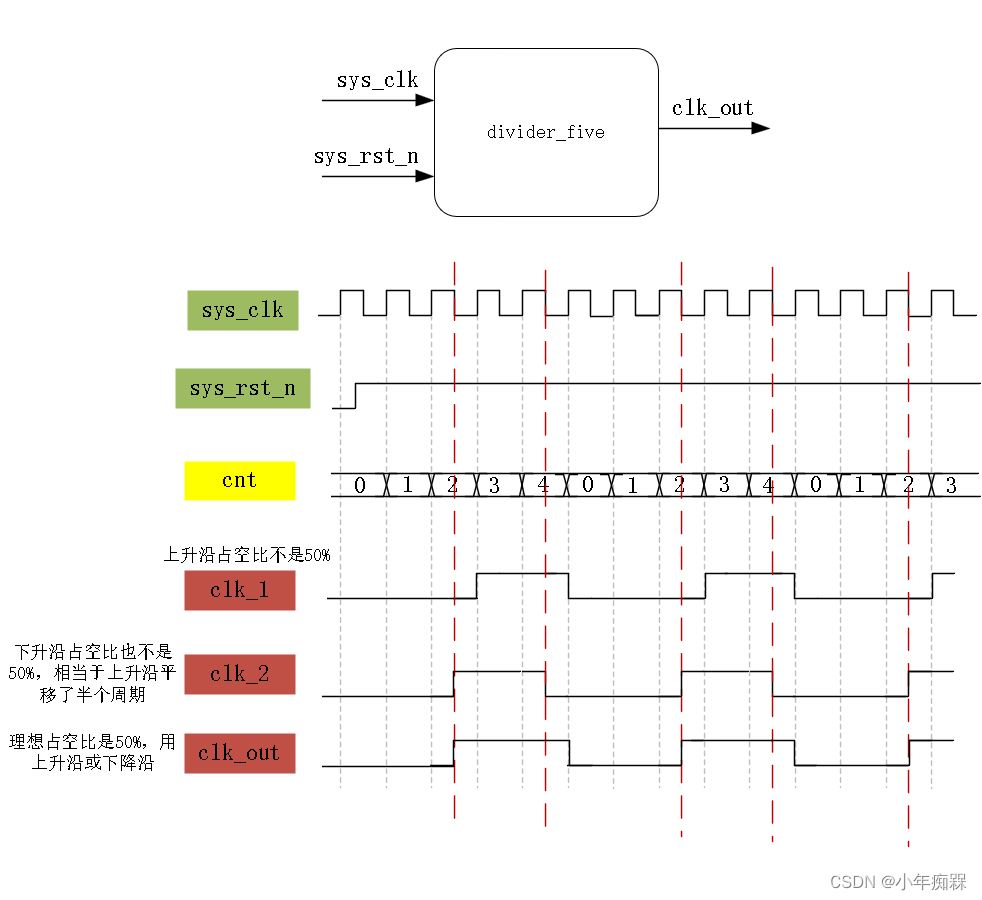

奇分频与偶分频不同,比偶分频更复杂。

上升沿和下降沿都满足不了50%占空比,故采用上升沿逻辑或下降沿,就可以得到50%占空比。

一、代码

1.rtl代码

代码如下(示例):

module divider_five

(

input wire sys_clk,

input wire sys_rst_n,

output wire clk_out

);

reg [2:0] cnt;

reg clk_1;

reg clk_2;

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n==1'b0)

cnt<=3'd0;

文章介绍了奇分频的概念,其复杂性高于偶分频,通过确保上升沿或下降沿产生50%占空比。提供了一段Verilog代码实现,包括rtl代码、RTLViewer视图及测试代码,并验证了仿真结果与预期波形一致。

文章介绍了奇分频的概念,其复杂性高于偶分频,通过确保上升沿或下降沿产生50%占空比。提供了一段Verilog代码实现,包括rtl代码、RTLViewer视图及测试代码,并验证了仿真结果与预期波形一致。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2078

2078

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?