目录

1.算法仿真效果

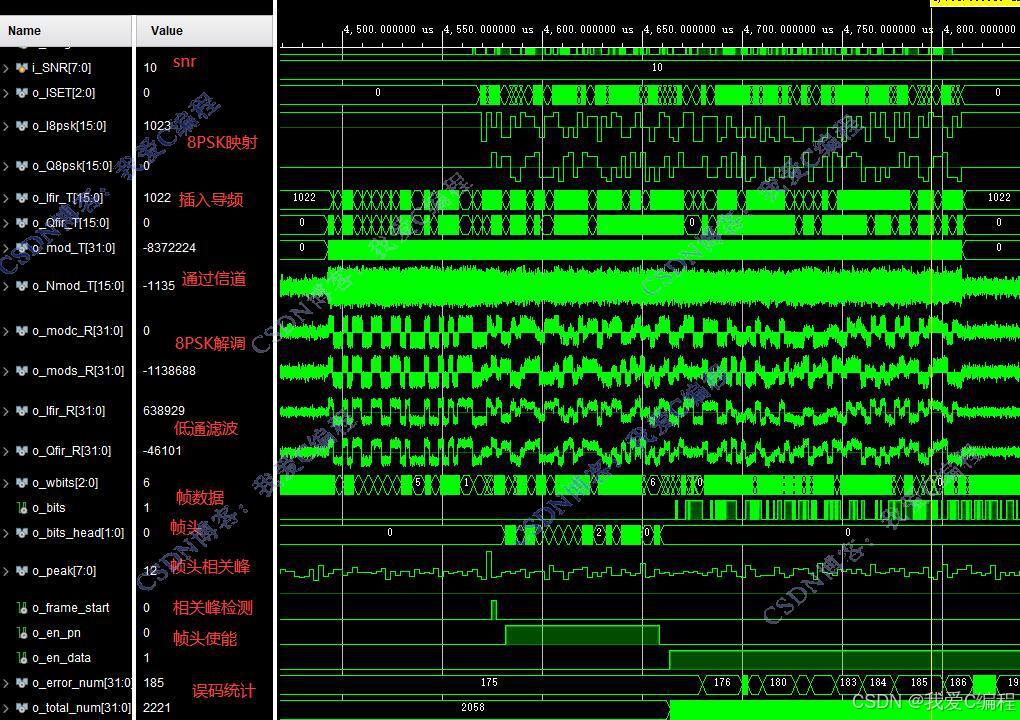

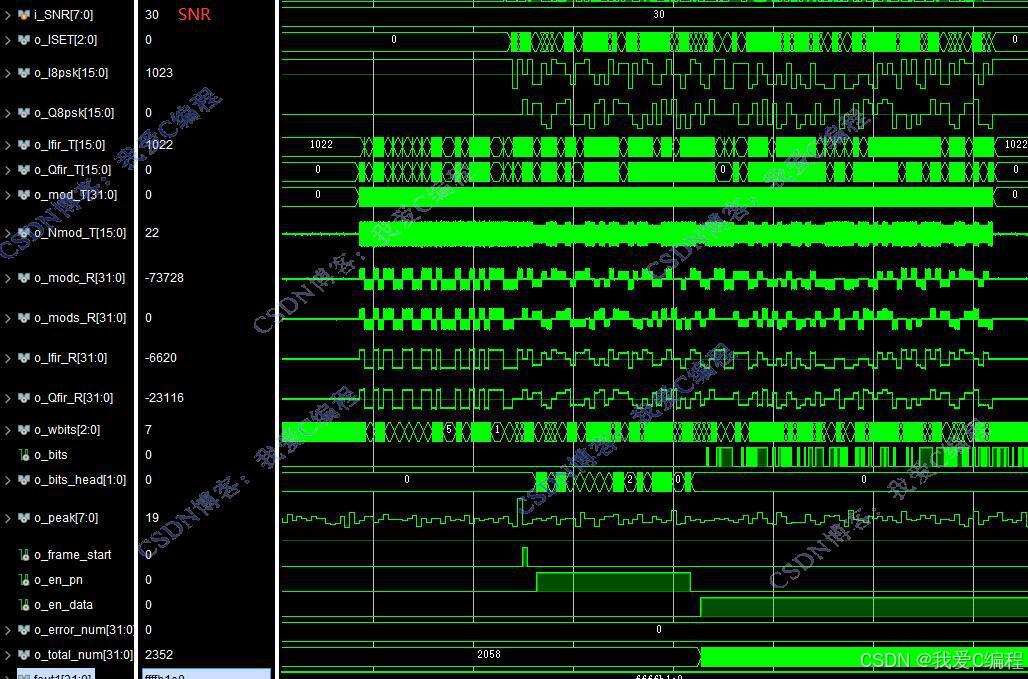

vivado2019.2仿真结果如下(完整代码运行后无水印):

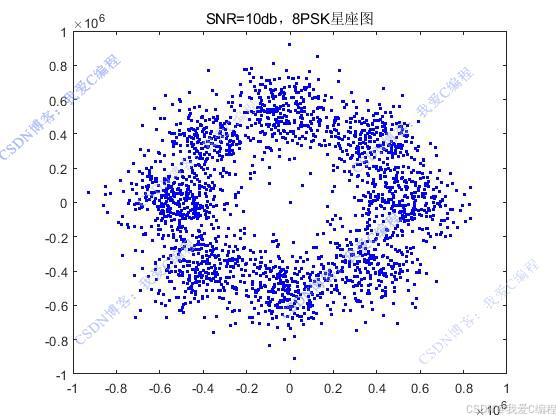

设置SNR=10db

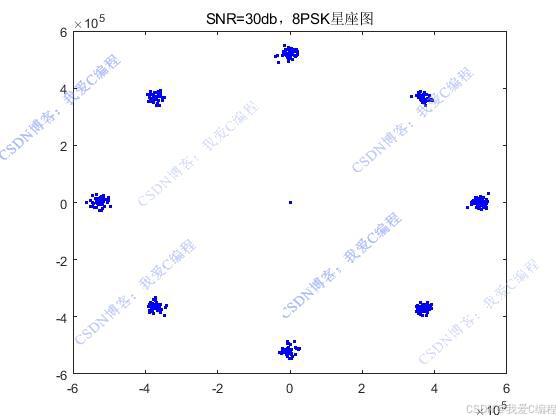

设置SNR=30db

仿真操作步骤可参考程序配套的操作视频。

2.算法涉及理论知识概要

随着通信技术的不断发展,相位调制技术因其高频谱效率和抗干扰能力而广泛应用于无线通信系统中。其中,8PSK(8相位相移键控)作为一种高阶调制方式,具有更高的频谱效率和更强的抗干扰能力,因此备受关注。然而,8PSK调制解调的实现复杂度较高,需要高效的数字信号处理技术。现场可编程门阵列(FPGA)作为一种可编程逻辑器件,具有高度的灵活性和并行处理能力,非常适合实现复杂的数字信号处理算法。

2.1 8PSK调制原理

8PSK调制是一种相位调制方式,其基本原理是通过改变载波的相位来传递信息。在8PSK中,一个符号周期内的相位变化有8种可能的状态,分别对应3个比特的信息。因此,8PSK调制可以看作是一种将3个比特映射到一个符号的映射方式。具体地,假设输入的比特序列为b2b1b0,则对应的8PSK符号可以表示为:

S(t)=Acos(2πfct+θk) (1)

其中,A是载波的振幅,fc是载波的频率,θk是第k个符号的相位,k=0,1,...,7。θk的取值由输入的比特序列b2b1b0决定,具体的映射关系如表1所示。

表1:8PSK映射关系

其星座图如下所示:

2.2 帧同步

在数字通信中,信息通常是以帧为单位进行组织和传输的。帧同步的目的是确定每一帧的起始位置,以便接收端能够正确地解调出每帧中的数据。

设发送的帧结构为:帧同步码 + 信息码元序列 。帧同步码是具有特定规律的码序列,用于接收端识别帧的起始。

帧同步的过程就是在接收序列中寻找与帧同步码匹配的位置,一旦找到匹配位置,就确定了帧的起始位置,后续的码元就可以按照帧结构进行正确的划分和处理。

3.Verilog核心程序

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2024/08/05 03:30:02

// Design Name:

// Module Name: TOPS_8PSK

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module TOPS_8PSK(

input i_clk,

input i_rst,

input signed[7:0]i_SNR,

input[1:0]i_en,

input i_dat,

output [2:0]o_ISET,

output signed[15:0]o_I8psk,

output signed[15:0]o_Q8psk,

output signed[15:0]o_Ifir_T,

output signed[15:0]o_Qfir_T,

output signed[31:0]o_mod_T,

output signed[15:0]o_Nmod_T,

output signed[31:0]o_modc_R,

output signed[31:0]o_mods_R,

output signed[31:0]o_Ifir_R,

output signed[31:0]o_Qfir_R,

output [2:0]o_wbits,

output o_bits,

output [1:0]o_bits_head,

output [7:0]o_peak,

output o_en_data,

output o_en_pn,

output o_frame_start,

output signed[31:0]o_error_num,

output signed[31:0]o_total_num

);

reg[9:0]cnt;

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

cnt <= 10'd0;

end

else begin

if(cnt == 79)

cnt <= 10'd0;

else

cnt <= cnt+10'd1;

end

end

reg dat_clk;

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

dat_clk <= 1'd0;

end

else begin

if(cnt == 39)

dat_clk <= 1'd1;

else

dat_clk <= 1'd0;

end

end

T8PSK T8PSKU(

.i_clk (dat_clk),

.i_clksample(i_clk),

.i_rst (i_rst),

.i_en (i_en),

.i_dat (i_dat),

.o_ISET (o_ISET),

.o_clk_3div(),

.o_I8psk(o_I8psk),

.o_Q8psk(o_Q8psk),

.o_Ifir (o_Ifir_T),

.o_Qfir (o_Qfir_T),

.o_cos (),

.o_sin (),

.o_modc (),

.o_mods (),

.o_mod (o_mod_T)

);

//加入信道

awgns awgns_u(

.i_clk(i_clk),

.i_rst(i_rst),

.i_SNR(i_SNR), //这个地方可以设置信噪比,数值大小从-10~50,

.i_din(o_mod_T[28:13]),

.o_noise(),

.o_dout(o_Nmod_T)

);

//8PSK解调

R8PSK R8SKU(

.i_clk (dat_clk),

.i_clksample(i_clk),

.i_rst (i_rst),

.o_clk_3div(),

.i_med (o_Nmod_T),

.o_cos (),

.o_sin (),

.o_modc (o_modc_R),

.o_mods (o_mods_R),

.o_Ifir (o_Ifir_R),

.o_Qfir (o_Qfir_R),

.o_wbits(o_wbits),

.o_bits (o_bits),

.o_bits_head(o_bits_head),

.o_peak(o_peak),

.o_en_data(o_en_data),

.o_en_pn(o_en_pn),

.o_frame_start(o_frame_start)

);

Error_Chech Error_Chech_u1(

.i_clk(dat_clk),

.i_rst(i_rst),

.i_trans({~i_dat,1'b1}),

.i_en_data(o_en_data),

.i_rec({~o_bits,1'b1}),

.o_error_num(o_error_num),

.o_total_num(o_total_num)

);

endmodule

0sj2_064m4.完整算法代码文件获得

V

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?