FPGA至简设计项目实践

目录

前言

发光二极管(Light Emitting Diode,LED)是一种能够将电能转化为可见光的固态半导体器件, 其核心是一个整个被环氧树脂封装起来的半导体晶片。晶片的一端附在一个支架上为负极,另一端连 接电源为正极。

提示:以下是本篇文章正文内容,下面案例可供参考

一、硬件原理

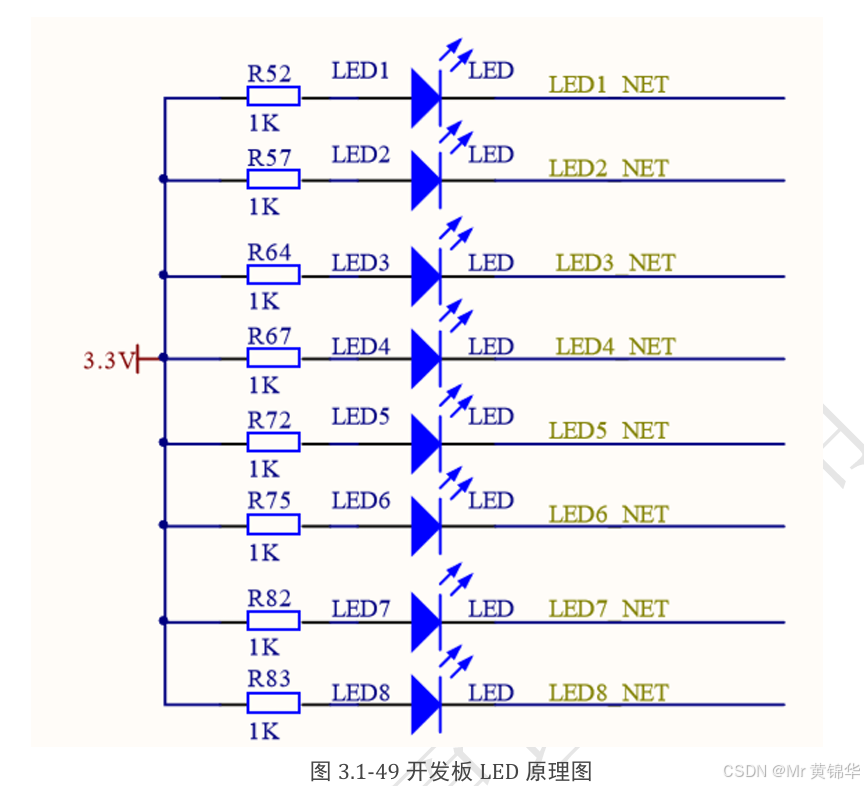

至简设计法的教学板一共有8个可以发出绿光的LE D灯。图中左边的LED1~LED8是教学板上LED灯的丝印,右边的LED1~LED8_NET为信号线名。 此标注是为了更好的理解设计,而在实际的开发板中不显示这些信号线。

LED 灯两端分别连接了3.3V的高电平和LED1~LED8_NET信号线。当LED1~LED8_NET 为 高电平时,电流无法导通,LED灯不发光;反之,当LED1~LED8_NET是低电平时,电流流通,此 时LED灯发光。因此只要控制了信号LED1~LED8_NET的电平情况,就相当于控制了LED灯发光 的情况。

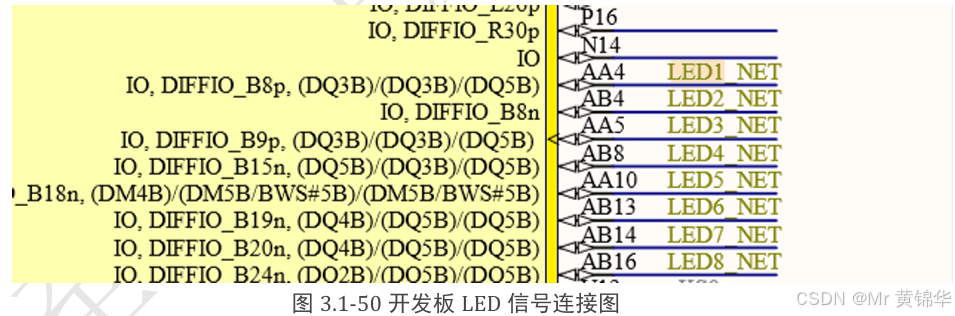

那么信号线LED1~LED8_NET又连到哪里呢?从下图可以发现这些信号都连接到了FPGA的管 脚上。

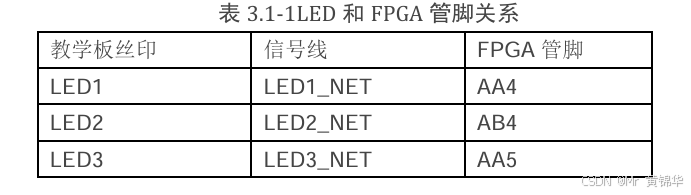

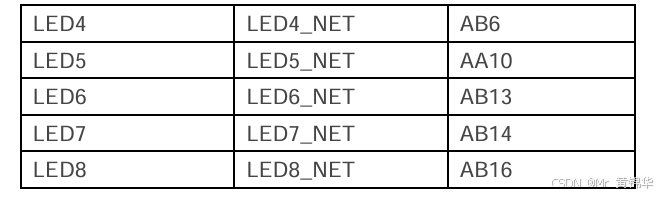

例如信号线LED1连接到 了FPGA的AA4管脚上。从表中可以看到LED1~LED8_NET分别与FPGA的8个管脚相连,因而 LED1~LED8_NET 处于高低电平以及LED灯是否发光最终取决于FPGA管脚的输出。举例说明,如 果想要控制LED7号灯,只需调整LED7连接的FPGA管脚AB14的输出就可以了。当输出为高电平 时LED7灯灭,当输出为低电平,LED7灯亮。8个LED灯各自对应一个管脚,因此这8个LED灯 都是由FPGA独立进行控制。

二、设计目标

本工程使用1个LED灯(LED1)来实现闪烁灯功能。工程的工作时钟为50MHz,即时钟周期 为20ns。当LED1 连接的管脚AA4输出低电平时,LED1灯亮,输出高电平时,LED1灯灭。具体功能要求为:隔1秒,亮N秒。N的变化为:1,2,3,„„,9秒,之后再次进入循环,如图3.1 51 1位闪烁灯功能图。上板后的效果展示可参见图3.1-52 1位闪烁灯的效果图。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?