前言

在RTL仿真过程中,我们有时候会对信号进行force操作,从而实现某些特定的功能。但是在仿真波形中,不能直接从波形上看出,这些信号的驱动,是因为前级电路的驱动,还是因为force的原因的驱动。从而使debug非常地不友好。

本文记录一种通过verdi查看force信号的方法,同时记录一种将波形中所有的force信息dump出来的一种方法。

一、verdi查看force信号

在verdi中,可以直接看到force信号的信息,会方便我们去debug force的信号。要想要verdi中,查看force信号,就需要vcs在仿真时候,生成fsdb波形时,加入force信号的波形信息。只需要在仿真参数中,加入 +fsdb+force 参数即可。当fsdb波形生成后,就可以在verdi中,直接查看到信号的force信息。

./simv +UVM_TESTNAME=test +fsdb+force

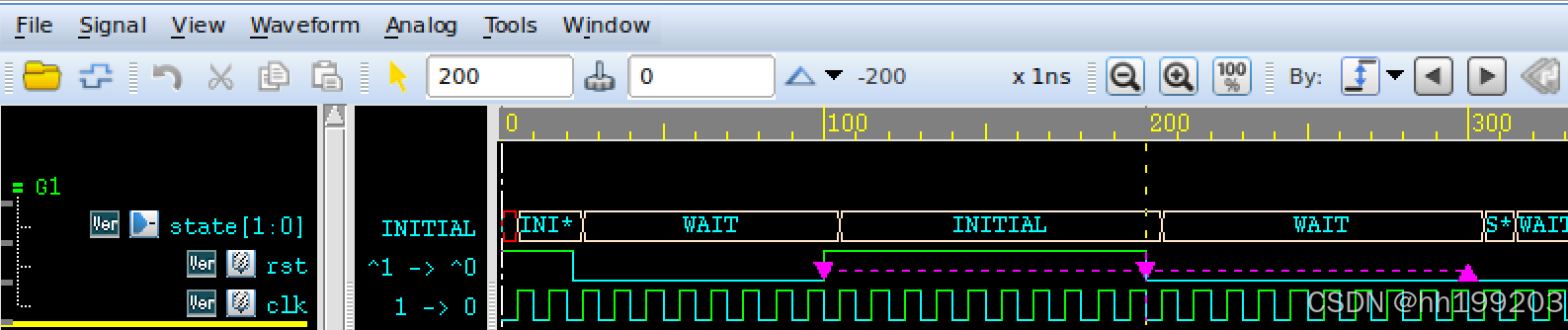

仿真结果如下所示

紫色向下的箭头表示这个时候,有force语句针对该信号有操作。

紫色向上的箭头表示这个时候,有release语句针对该信号操作。

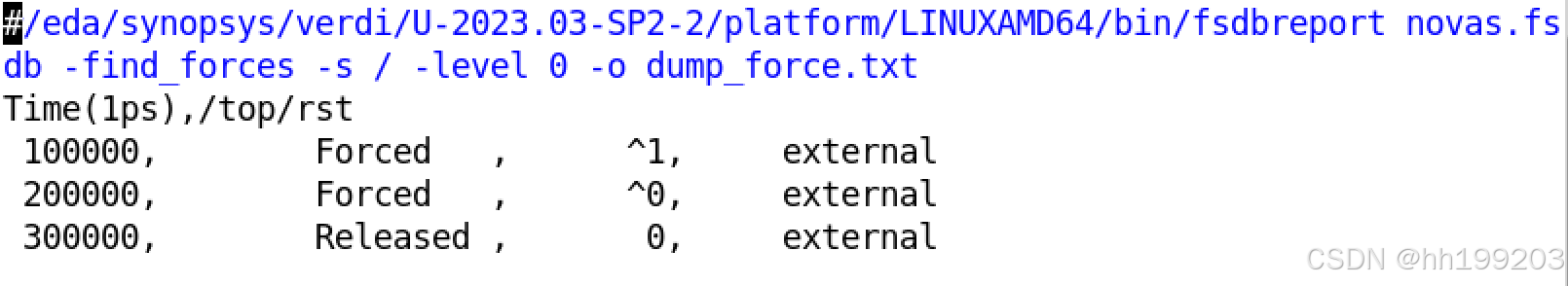

二、dump波形中的force信息

在一个环境中,可能force的信号比较多,通过上面的波形方式,去把每一个信号给拉出来,判断信号是否有force,效率就会比较低了。此时,我们可以使用fsdbreport命令,从波形里面,把所有的信号force的信息,全部给抓出来,保存在一个文件中,这样,我们通过该文件,就可以知道仿真过程中的所有信号force信息。

fsdbreport xxx.fsdb -find_forces -s "/*" -level level_number -o xxx.txt

其中:

xxx.fsdb:是输入的fsdb波形文件

-s:指定查找force信息的层次, /* 表示从最顶层开始

-level:表示从指定的层次,向下查找层次的数目。0表示指定的层次和以下所有的层次。1表示指定的层次,2表示指定的层次和下一层次。之后依次类推,一般都是直接使用0

-o:指定输出文件

总结

本文主要记录通过verdi查看force信号的两种方式。

3583

3583

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?