1 流水线局限性

1)流水线地每一段可以看作是一个组合逻辑F加上一个锁存器L,信号通过F后在L锁存;

T_MAX通过F地最大传输延迟;

T_MIN通过F地最小传输延迟;

T_L正确建立时钟信号所需要地额外时间,包括必要地建立和保持时间。

时钟周期 T > T_MAX - T_MIN + T_L

T_MAX - T_MIN可以趋向于0(延长最小传输路径)

T_L受整个系统内时钟信号分布影响;

性能权衡:流水线深度和价格;

2 指令流水线

指令周期:逻辑概念,处理一条指令地时间延迟;

机器周期:物理概念,流水线的时钟周期;

1)一致的运算分量

量化流水段,将指令周期分解成多个机器周期的过程。

尽量减少内部碎片,对存储器的访问是关键,寻址方式优化;

保持流水线均衡;

2)重复的运算

多功能流水线,处理多种不同的指令,减少每种指令的无效或空闲的机器周期

即减少外部碎片,要对不同指令需要的子运算序列资源进行整合。

统一指令类型;

3)独立的运算

减少流水线停顿,内部机制检测指令间发生的相关,并保证指令相关不会导致错误。

尤其是存储器访问有关,指令相关有可能导致流水线停顿,导致失效。

3 流水线处理器

1)流水线保持均衡;

取指 --> 译码 --> 执行 --> 访存 --> 回写

取值 --> 译码 --> 取操作数 --> 执行 --> 存储

基本的是分为5个分量,但不局限;

量化流水线可以将多个分量合成一个分量,也可以将1个分量进一步分成多个分量;

同时需要考虑硬件能力,一个机器周期内可以处理几次读写请求;

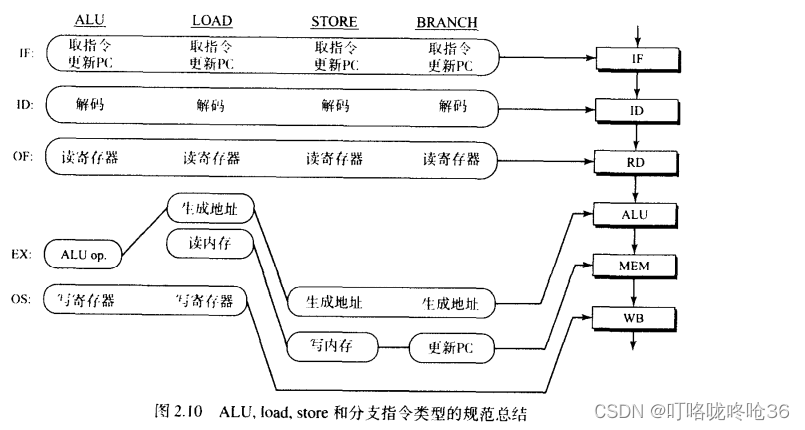

2)指令类型统一

指令分成3种类型:

ALU指令:完成算数和逻辑运算;(寄存器)

ld/st指令:完成数据在寄存器及存储器间的移动;(memory,带偏移的寄存器寻址)

分支指令:控制指令执行的顺序;(PC相对寻址,带偏移的寄存器寻址)

资源整合为6级流水,load使用6级,其他3种指令使用5级;

ALU:一个空闲周期MEM

ST:不需要WB

branch:不需要WB

三个优化目标:

1. 减少所有指令类型需要的资源总量

2. 提高所有流水段的利用率

3. 减少每种指令类型的总延迟(如果某指令的空闲周期不可避免,尝试把它放到流水线末尾)

3)流水线停顿减少

如果有指令相关,化解相关可能会导致流水线停顿;

真相关:RAW,先写后读

反相关:WAR,先读后写

输出相关:WAW,写后写

存储器数据相关/寄存器数据相关/控制相关

1. 停止执行发生相关的指令,并保证对相关寄存器的读写是按正常顺序进行的;

2. 通过定向路径减少开销:新增物理的定向路径 forwarding path输出数据;

3. 流水线互锁机制:检测出所有的流水线相关,并保证所有相关得到满足;

4 流水线处理器

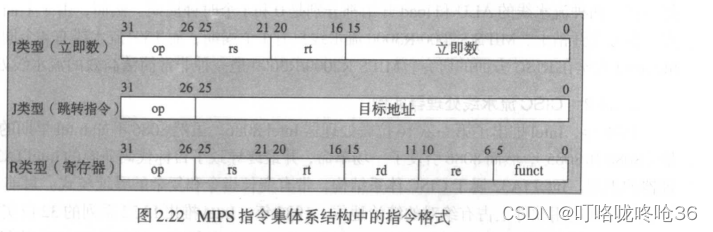

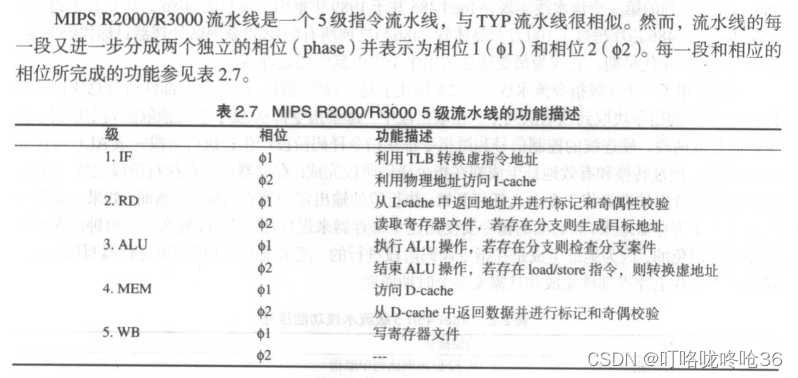

1)RISC

以MIPS 32bit为例

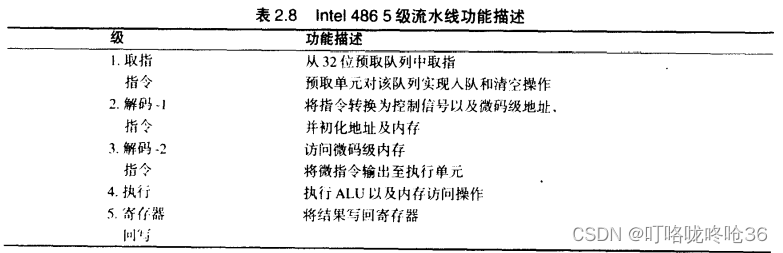

2)CISC

本文探讨了流水线处理器的设计原理与优化方法,包括如何保持流水线各阶段的均衡、统一指令类型减少外部碎片以及减少流水线停顿等。还讨论了RISC与CISC架构的特点。

本文探讨了流水线处理器的设计原理与优化方法,包括如何保持流水线各阶段的均衡、统一指令类型减少外部碎片以及减少流水线停顿等。还讨论了RISC与CISC架构的特点。

1993

1993

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?