点击蓝字

关注我们

编者说

一直想让竹兄给大家写一个经验分享,今天终于约到了稿子,作为路桑的学生,有一些独特的经历和经验分享给大家,本文分为两大部分,第一部分为经验分享,问答,第二部分为竹秋一的秋招面经

问

研究生导师是路桑,找工作是种什么样的体验?

答

有的面试官会问导师是谁,我说是路桑,他们有的会嗷~一下,有的说和他认识,有的会和我细聊在路科实习的日常

找工作就……没有体会到其他人说的那种卷的感觉。感觉一切都很顺利。

教育背景:

本科双非微电子专业,研究生读的211,

研究方向:

数字IC验证。

本科刚入学的时候对微电子集成电路的东西没什么概念(因为高考分数不够被调剂,一志愿是计算机),但是学着学着发现……还是学不懂。一直到大三才慢慢了解IC是个啥东西,有兴趣之后决定考研深造(更好找工作)。

研究生入学后本想往数字IC设计方向发展,但从选修了路桑老师的SV验证课程后(路桑老师在我学校授课),了解到了以后工作中的IC验证岗位,便对验证有了很大的兴趣,加上被路桑的人格魅力吸引,所以打算找实习的时候就跟着他学验证了。

ps:我这个专业研二后有两种选择:跟着校内导师去实验室或者找个公司实习,我选择了后者。

加入了路桑的办公室后,路桑就是我的研究生导师啦。先是学了v2课程,后面被师父(路桑)带着做了一个虚拟项目,便跟着实习的公司做他们的实际项目了。

秋招过程:

由于在公司实习,所以简历上的项目经历比较丰富,简历筛选没有被刷过。后来秋招前期海投,不断地积攒笔试面试经验,秋招后期精准的定位了自己想去的几个大厂,然后就干。顺利拿到了一些大厂的offer后,最终选了一个离家近的、薪资也还不错的公司。

个人经验:

我个人觉得面试官比较喜欢有真实的项目经验和实习经历的学生,不管是设计还是验证。所以有机会一定要找渠道抽时间去完善一下这些经历,比如假期找公司实习(看命,我了解有的导师不放)或者网上做一些开源项目。

秋招之前有一些公司会开放实习岗位,我的建议是去试一试,拿不到offer就当攒经验,拿到offer更好,直接去公司实践一下。如果导师不放也没关系,拿到实习offer在秋招中再投这家公司时帮助很大,比如某鑫会免笔试面试,某哥会安排直通最终面。

可以加一些IC技术讨论群,科研累了摸鱼的时候看一看大家讨论了什么问题,有没有群友解决,看到就是赚,你又学了一个新知识。同样的,提前加一些师兄师姐的秋招群,一方面可以了解他们在笔试面试中都遇到什么问题,怎样回答比较好,另一方面可以通过他们的讨论了解到哪些公司比较坑,哪些公司养鱼,哪些公司诚意足,这对第二年自己的秋招有一个参考。

编者:

此处打广告数字IC打工人交流群(QQ,微信)

公众号底边栏自取

平头哥

一

面

l 自我介绍

l 验证环境结构

l 完整的验证流程

l AMBA总线细节:AXI有哪些信号,AHB有哪些信号,resp为error时ready保持几拍

l Reference model怎么写

l 功能覆盖率怎么定义(手撕代码),采样的信号从哪里来

l Interface怎么写

l Sequence怎么挂载到sequencer上,激励怎么发出来

l (简历)DMA的验证里,功能点有哪些

l 模块级和系统级验证的关注点有什么不一样

l 了解cache吗

l (简历)HVP是什么东西

l UVM各个phase了解吗

l Interface怎么传递到环境里

l 两个task怎么并行执行

l 会不会python

二

面

l 本科和研究生学过哪些课程,有什么样的经历。

l 使用PMOS和NMOS实现一个NAND,写出真值表,再用NAND实现一个XOR,只能用NAND。

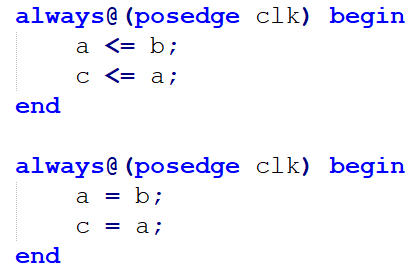

l Verilog阻塞和非阻塞赋值。以下两段代码综合出来的电路有什么不同。

l 用verilog实现:一个1bit输入a,一个1bit输出b,当a为x态时,b为1,否则为0。如果a为2bit,a[0]和a[1]只要有一位是x态,b为1,再写一遍verilog。

l 给一个DUT,怎么搭环境,环境里有哪些元素。覆盖率模型里面应该包括哪些?Scoreboard怎么比较数据?如果数据乱序应该怎么比较?

l 黑盒验证有什么缺点?如果采用黑盒验证,测试全部通过,但是设计里的状态机出错(卡在某一状态、没有正确退回初始态等),应该怎么解决?

l 给一个实际案例,有一个DUT按一种编码规则输入32bit数据,输出1bit判断输入是否符合编码规则,符合输出1,不符合输出0。请搭建一个验证环境,详细描述环境的构成、逻辑、激励、覆盖率等。在回归测试阶段,如何保证该设计100%正确?

三面(HR面)

乐鑫

一

面

l 自我介绍

l (简历)VIP怎么写

l 用verilog写一个I2C接口的pad

l 验证流程

l 验证环境怎么搭

l 写一个driver class基本的结构,手撕代码

l `uvm_component_utils有什么用

l `ifndef,`define,`endif有什么用

l UVM中的factory机制有什么好处

l 有没有用过process

l run_phase和main_phase的区别

l 寄存器模型的方法(write,mirror等)

l TLM怎么用

l 覆盖率分类

l (简历)形式验证有哪些,有没有用过formality

二面(HR面)

三

面

l 自我介绍

l 讲了讲做的项目

l 有没有做过复位测试(在模块运行过程中给一个有效复位),设计会怎么样,driver会不会卡死

l UVM工厂机制的好处

l 仿真中如何指定要跑哪个test,是什么原理

l uvm_config_db的set优先级,test、env和agent哪个优先级更高

l SV写一个寻找1~100以内所有质数的逻辑

l SV写一个判断10000以内的数,该数任意一位有6就打印

字节跳动

一

面

l 自我介绍

l (简历)简单讲一下PSS和infact工具

l(简历)讲一下使用JasperGold工具做过哪些?你认为功能验证和形式验证哪一个更好?

l uvm_object和uvm_component的区别

l uvm factory有什么用?

l 有没有使用过set_factory_override函数

l (手撕代码)给一个同步FIFO,接口:clk、rstn、data_in、data_out、full、empty,写一个检查它的scoreboard,具体体现检查逻辑。

l 声明一个rand int a,可以随机的值有1、4、6、8、12。如何实现每一次随机都是不同的值(之前随机过的不能再出现)。

l Verilog中blocking和non-blocking的区别。

DJI大疆创新

一

面

l 自我介绍

l 讲讲简历上的项目

l (简历)自己写的agent里,item如何传递到driver?

l 如何划分验证功能点

l 在验证环境中如何模拟一个fifo

其他的因为时间比较长,忘了

二

面

l 自我介绍

l 讲一讲学校里社团的经历

l 你认为校外实习的学生和校内实验室科研的学生在就业上有什么优劣和不同

l 由于公司流程不规范的问题导致部门之间或同事之间存在“中间事”,分析一下怎么解决

l 本科或研究生阶段有没有遇到很有挫败感的事情,得到的教训是什么

l 认为在社交或技术方面有没有什么欠缺?讲三个,并讲一下如何弥补

ZEKU(OPPO)

一

面

l 自我介绍

l (简历)VIP怎么写,优秀的VIP是什么样的

l UVM的TLM通信中,analysis port应该连接什么,把数据放入的方法是什么,在哪里实现?(analysis imp)追问imp中实现的方法是function还是task

l UVM寄存器模型的后门访问方法有哪些

l main_phase和run_phase有什么区别

l (简历)使用过哪些形式验证

l 讲一下SVA中的蕴含操作符

l 了解AMBA吗?讲一下AXI协议中的“4K边界”是什么

l I2C协议和UART协议的区别

l (简历)讲讲PSS和Infact

l (简历)讲讲环境自动化生成工具的使用,如果有自定义VIP如何加进去

l (简历)VO是什么意思?(Verification Object)

l 模块验证和系统验证有什么区别?验证的关注点在哪

二

面

l 自我介绍

l 讲一下研究生的实习经历

l 验证过程中怎么和设计人员沟通,如果设计人员脾气不好你会怎样做

l 认为自己哪些地方需要提升

l 认为实习公司的哪些地方需要提升

l 如何保证验证的完备性

l 如果领导安排的项目中有自己的知识盲区,你会怎么办

l 如果工作过程中突然安排了很紧急的事情,你会怎么办

商汤科技

一

面

l 自我介绍

l 讲讲自己做过的项目

l (简历)讲讲在项目里写的agent,自己觉得写的怎么样(复用性)

l UVM的工厂机制好在哪里

l UVM中发送激励的方式有哪些

l 仿真如何停止

l (简历)了解形式验证吗

l 大概讲一下AXI协议

l 了解AXI的乱序访问吗

l AXI协议中假设wdata是128bit,写数据时地址以64bit对齐,此时wdata和wstrb怎么给

紫光展锐

一

面

l 自我介绍

l 问了问简历上的项目,然后根据项目问的比较细,比如怎么搭建的环境、如何保证验证充分没有bug、在做这个项目的过程中有没有遇到什么困难

l SVA的三要素是什么

l UVM中如何在一个sequence中发送两种不同类型的item

l sequencer的仲裁依据

l sequence如和改变优先级

l AHB协议有哪些信号

l AHB发送一个trans最少几个周期

l AHB发送incr4时,每根控制信号的值是多少(htrans、hburst)

l AHB协议中burst有哪些类型?

l AHB协议的wrap操作里,地址边界如何计算

二

面

l 问我是不是掌握了SV和UVM

l 针对某一个接口开发agent的步骤

l AHB和APB的区别

l 如何保证验证的完备性

l 职业规划

l 技术方面和人情世故方面的优缺点

l 想留在哪个城市,原因是什么,该城市你认可的芯片公司有哪些

l 期望薪资是多少

兆易创新

一

面

l 自我介绍

l 介绍简历中的项目里DUT的功能、接口。

l DUT接口有哪些信号,协议是什么样子。

l sequence里描述的场景如何通过driver发送出来。

l monitor将数据交给了谁。

l 讲一下virtual_sequence和virtual_sequencer的内容和用法。

l m_sequencer和p_sequencer之间的关系。

l top_seq一般在哪里挂载到virtual_sequencer。

l top_seq挂载到virtual_sequencer时,每一个sequence如何找到自己的sequencer。

l refmodel和scoreboard何如知道需要拿到多少数据。

l refmodel和scoreboard中使用寄存器模型的坏处是什么。

二面(HR面)

紫光同芯

综

合

一面(技术面)

l 自我介绍

l 聊项目

二面(技术面+HR面)

l 自我介绍

l 聊项目

l 聊研究方向

l 聊人生

关注我们获取更全的数字IC咨讯与知识

本文分享了一名数字IC验证方向研究生的秋招经验及面试经历,包含多个大厂的面试题目,适合准备秋招的同学参考。

本文分享了一名数字IC验证方向研究生的秋招经验及面试经历,包含多个大厂的面试题目,适合准备秋招的同学参考。

927

927

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?