最近在配置一款时钟同步芯片(CDCE72010),具体通过配置内部寄存器来输出不同频率的时钟。这块芯片有一个时钟输入(491.52MHz),它的一路输出时钟是输入时钟的二分频,也就是(245.76MHz)。这一路输出是给FPGA的,所以我打算通过在FPGA内部产生一个491.52MHz的时钟作为ILA的采样时钟来抓取这一路输出时钟,以验证配置寄存器是否成功。

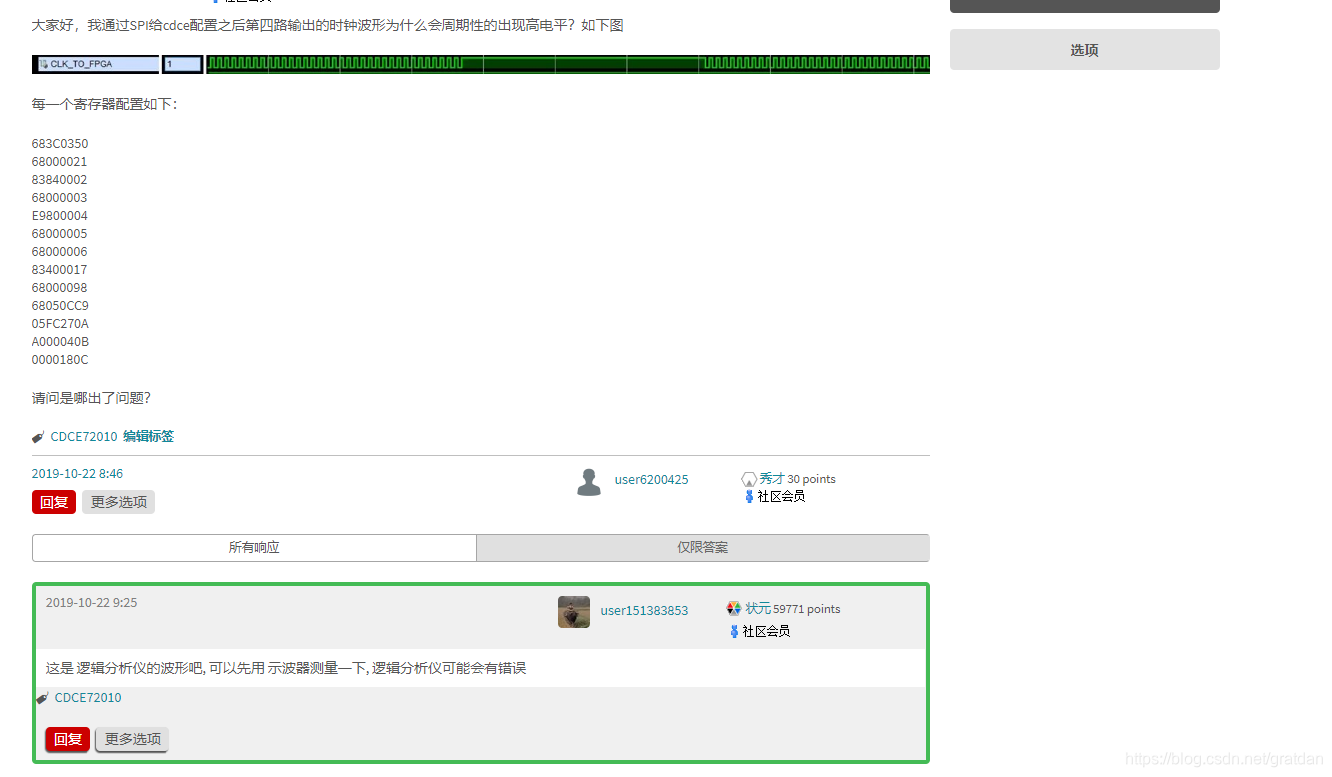

但是万万没想到,在ILA上观察,每次都会出现周期性高电平,于是我去看寄存器说明书,想找到问题的原因,但是怎么试都无济于事,所以我只好去TI论坛求救。

我刚开始觉得这个大哥说的没道理,于是我又是去看说明书又是找老师又是改寄存器,但怎么都没用!!!上火!!!

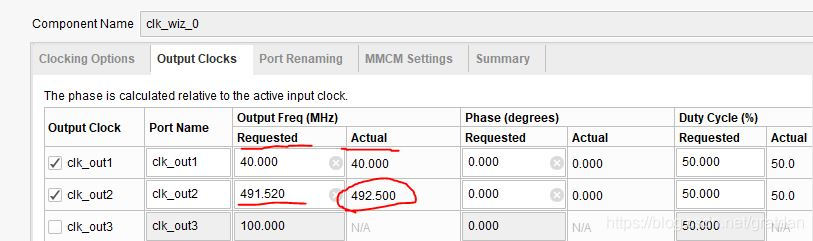

冷静了几天,我发现一个东西!!!

然后我把时钟通过测试引脚接出来拿示波器看了看,根本就没有周期高电平!!!

一点小小的频偏引发的血案!!!感谢那位大哥!!!

ps:就算PLL分出来的时钟是491.52MHz,也不能通过ILA来否定什么,因为输入时钟也不一定稳定。还是得看示波器。

本文分享了一次使用ILA和示波器验证时钟同步芯片CDCE72010输出时钟的实践经历。作者最初尝试通过ILA捕获491.52MHz时钟信号进行验证,却误读了周期性高电平现象。在深入探究后发现,ILA的读数受输入时钟稳定性影响,而示波器则能更准确地反映实际时钟信号,揭示了小频偏导致的问题。

本文分享了一次使用ILA和示波器验证时钟同步芯片CDCE72010输出时钟的实践经历。作者最初尝试通过ILA捕获491.52MHz时钟信号进行验证,却误读了周期性高电平现象。在深入探究后发现,ILA的读数受输入时钟稳定性影响,而示波器则能更准确地反映实际时钟信号,揭示了小频偏导致的问题。

6049

6049