参考正点原子资料

gate.v

module gate(

input A,

input B,

output Y_and,

output Y_or,

output Y_not

);

assign Y_and=A&B;

assign Y_or=A|B;

assign Y_not=~A;

endmodulegate_tb

`timescale 1ns/1ns //仿真的单位和精度

module gate_tb();

reg A;

reg B;

wire Y_and;

wire Y_or;

wire Y_not;

initial begin

A=1'b0;

B=1'b0;

#100

A=1'b0;

B=1'b1;

#100

A=1'b1;

B=1'b0;

#100

A=1'b1;

B=1'b1;

end

gate u_gate(

.A(A),

.B(B),

.Y_and (Y_and),

.Y_or (Y_or),

.Y_not (Y_not)

);

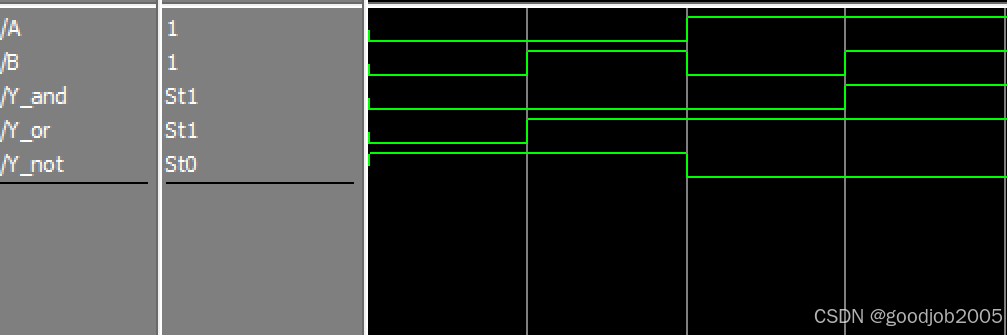

endmodule仿真

| A | 0 | 0 | 1 | 1 |

| B | 0 | 1 | 0 | 1 |

| Y_and | 0 | 0 | 0 | 1 |

| Y_or | 0 | 1 | 1 | 1 |

| Y_not | 1 | 1 | 0 | 0 |

2758

2758

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?