以下所有均基于正点原子的教程

原理说明

周期测量法产生误差的原因:

周期测量法是先测量出被测信号的周期T,然后根据频率f = 1/T求出被测信号的频率。在这个过程中,由于计数器在测量时只能对整数个周期进行计数,因此当实际测量时间结束时,如果最后一个周期尚未完成,则无法计入,导致测量结果偏低;反之,如果多计了一个未完成的周期,则测量结果偏高。这种误差即为±1个被测信号周期的误差。

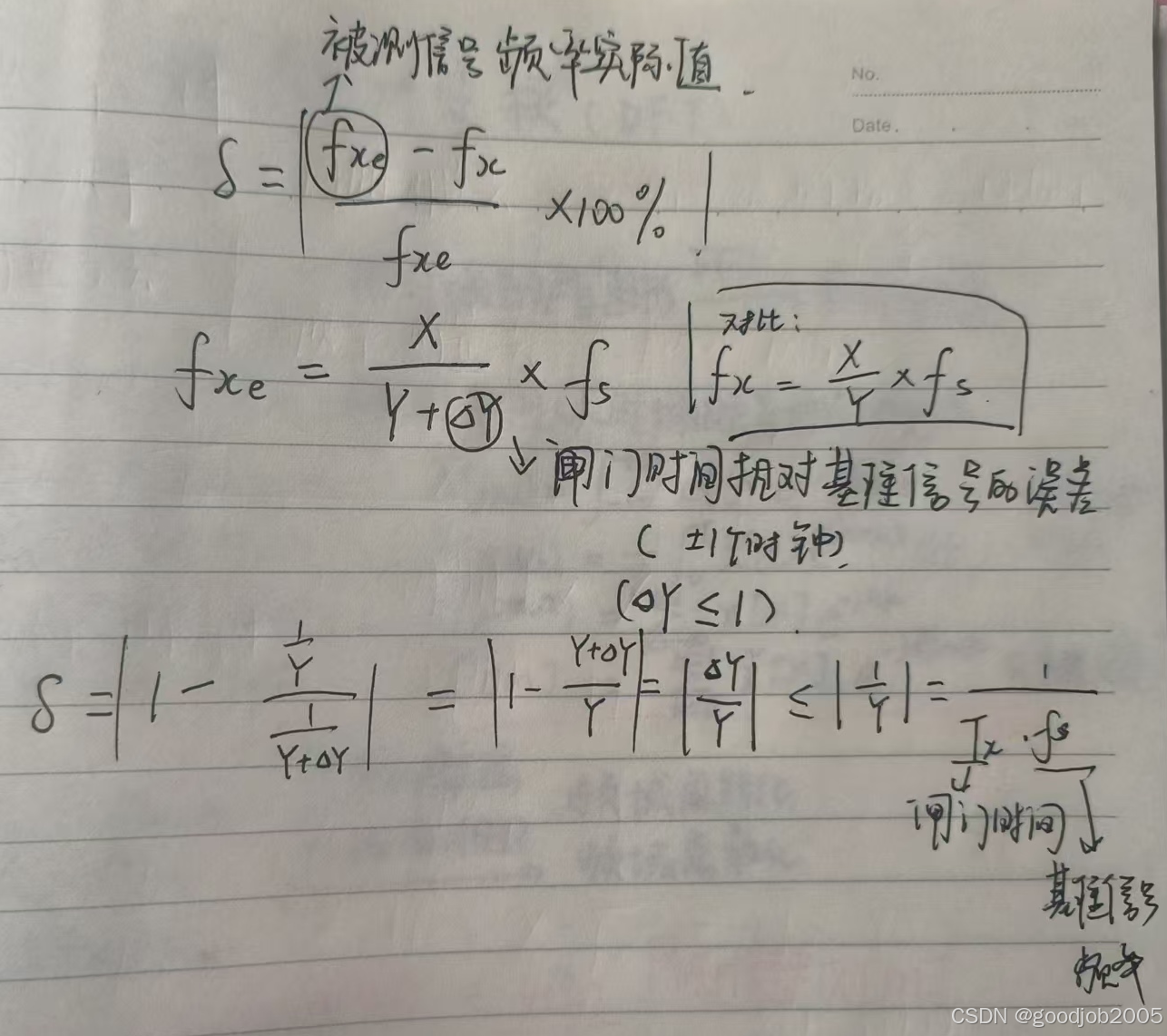

频率测量法产生误差的原因:

频率测量法是在固定时间内对被测信号的脉冲数N进行计数,然后求出单位时间内的脉冲数,即为被测信号的频率。同样地,由于计数器在测量时只能对整数个脉冲进行计数,因此当实际测量时间结束时,如果最后一个脉冲尚未到达,则无法计入,导致测量结果偏低;反之,如果多计了一个未到达的脉冲,则测量结果偏高。这种误差即为±1个被测信号脉冲的误差。

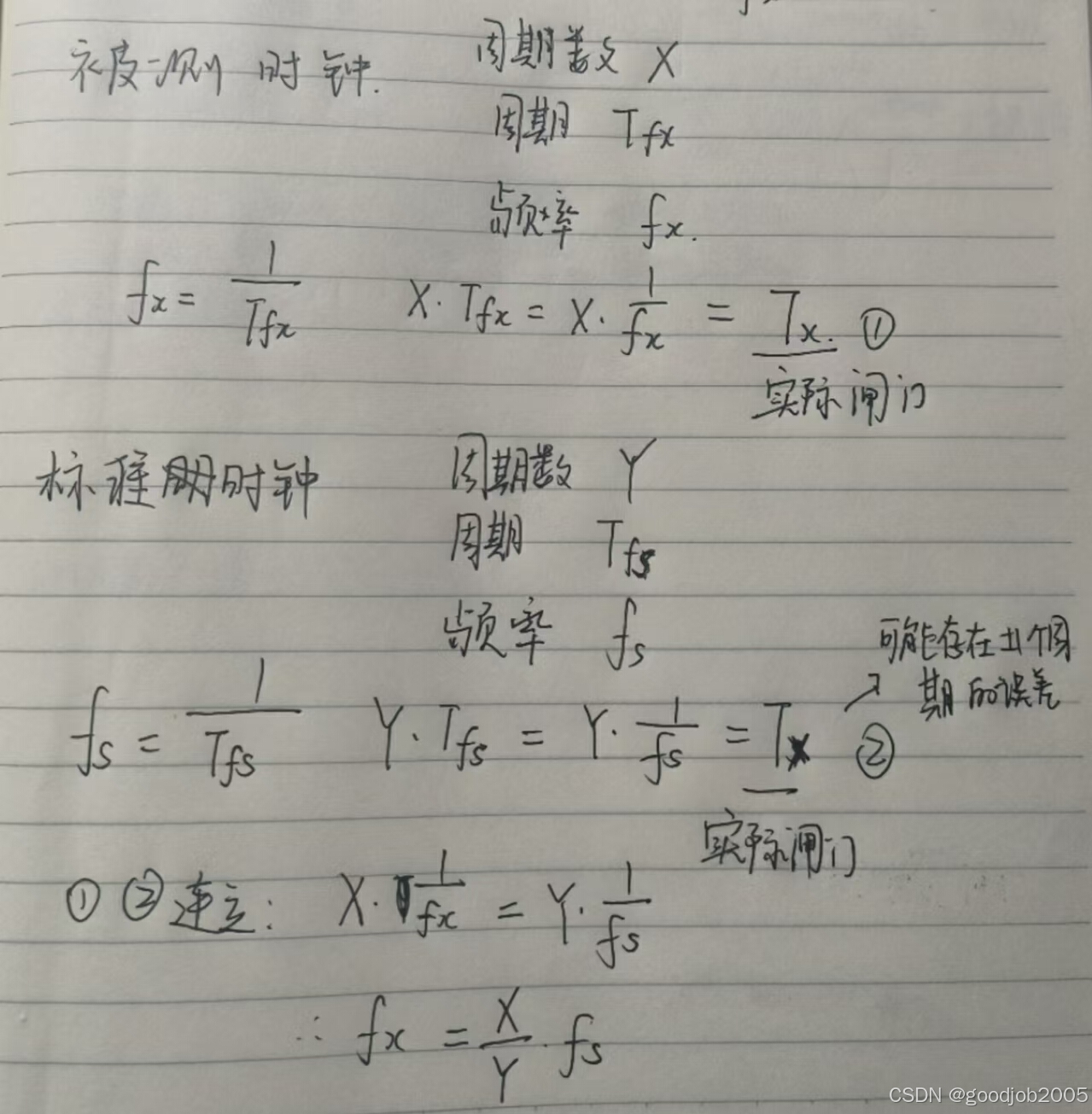

等精度测量法

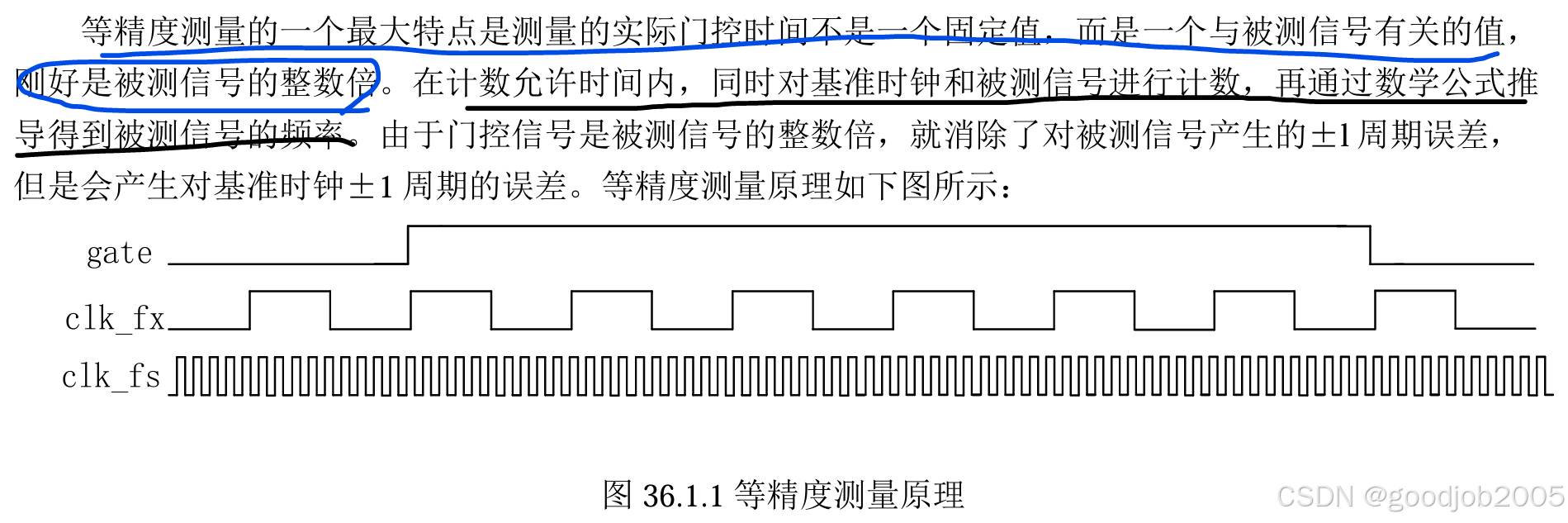

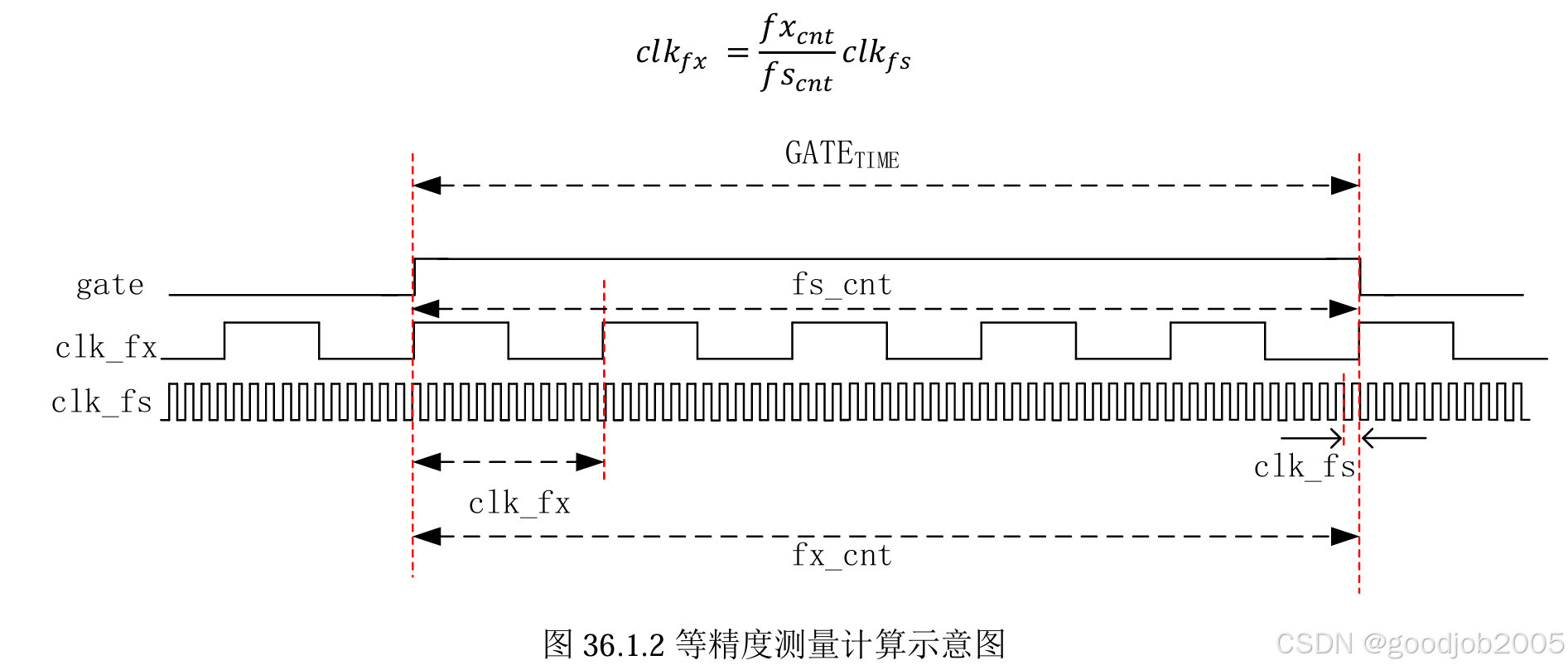

基准时钟(clk_fs)是系统内的一个固定频率的时钟信号,通常由晶体振荡器、时钟发生器或外部时钟源提供。它为系统内的所有操作提供一个统一的时间参考

门控信号(gate)的基本思想是通过逻辑门(如与门)来控制时钟信号的传递。当某个功能模块不需要运行时,可以通过门控信号关闭其时钟,从而减少不必要的功耗。

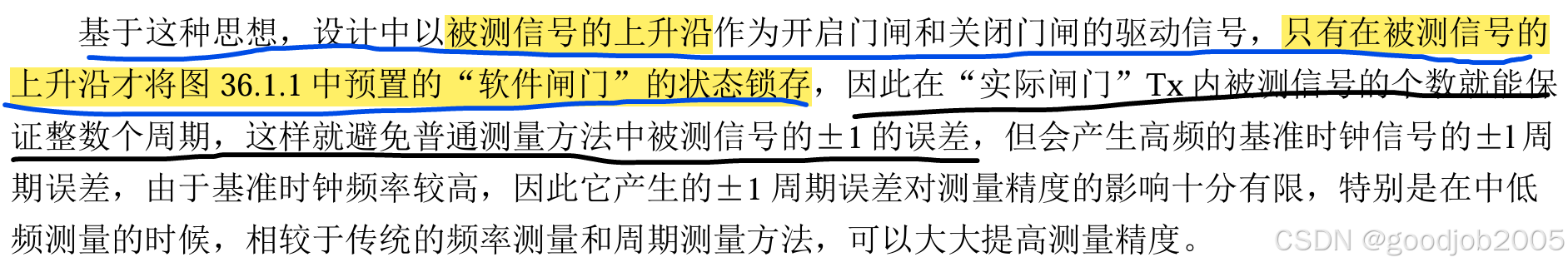

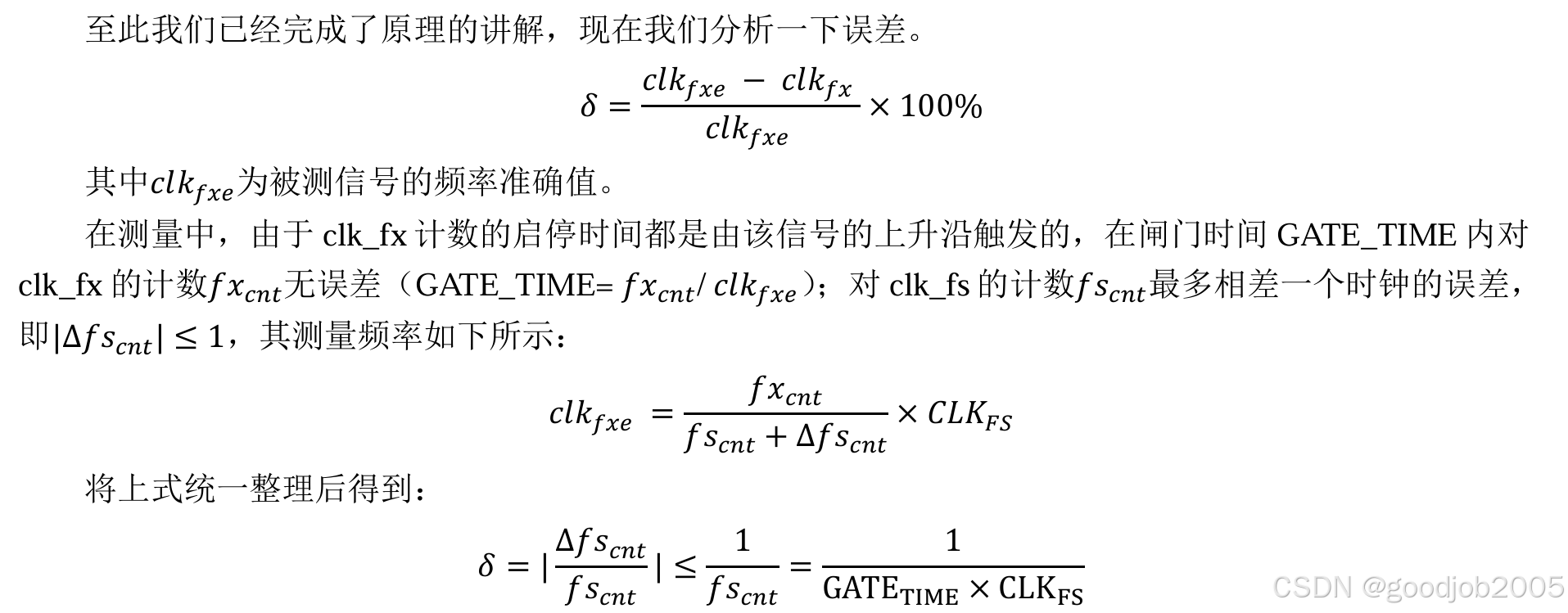

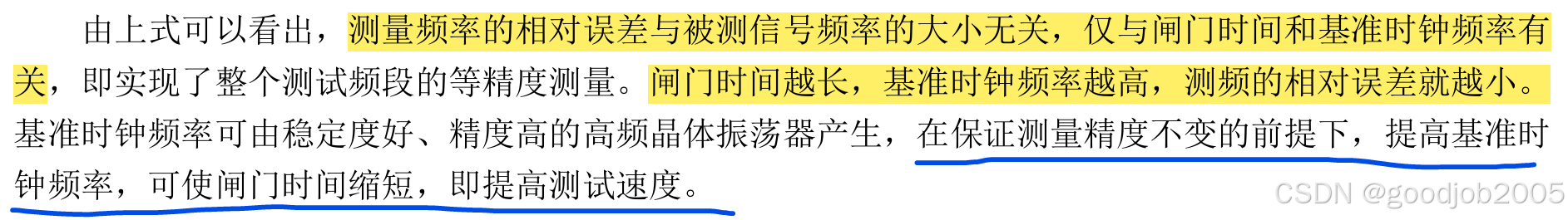

- 首先,被测信号频率clk_fx的相对误差与 被测信号的频率无关;

- 其次,增大测量时间段“软件闸门”或提高“基准频率”clk_fs,可以减小相对误 差,提高测量精度;

- 对于等精度测量法,虽然它通过使实际门控时间(gate)是被测信号周期的整数倍来消除被测信号产生的±1周期误差,但由于基准时钟信号(clk_fs)的频率远高于被测信号(clk_fx),因此在实际门控时间内对基准时钟的计数仍可能产生±1周期的误差。不过,由于一般提供基准时钟clk_fs的石英晶振稳定性很高,所以基准时钟的相对误差很小,可忽略。假设基准时钟的频率为100MHz,只要实际闸门时间大于或等于1s,就可使测量的最大 相对误差小于或等于10^(-8),即精度达到1/100MHz。

等精度测量的核心思想在于如何保证在实际测量门闸内被测信号为整数个周期,这就需要在设计中让实际测量门闸信号与被测信号建立一定的关系。

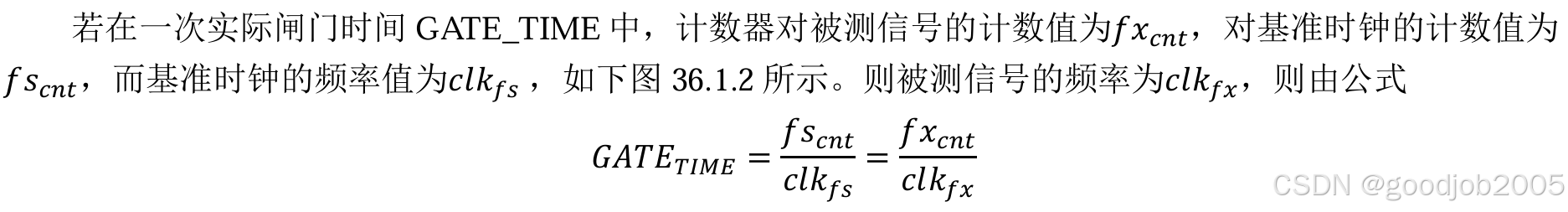

公式推导

大概就是这样:

动态数码管

代码思路:

分为两个模块:

-

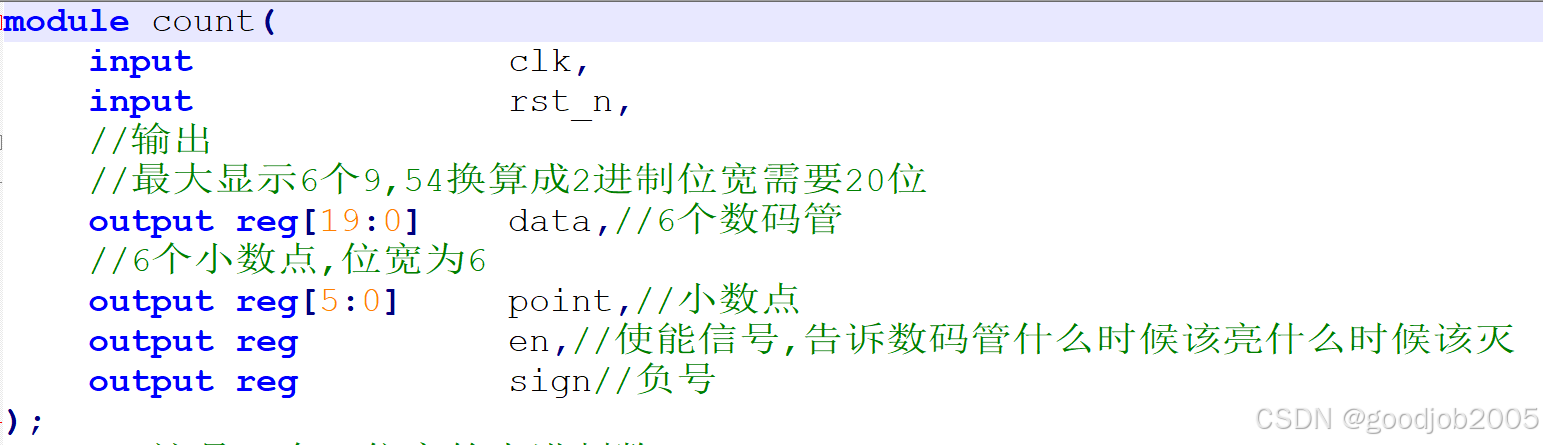

计数模块

功能:因为要做到让数码管每隔100ms的数值加1,所以100ms用这个模块来计数,并且需要把当前数值显示在数码管上,所以也需要把当前数值传递出去

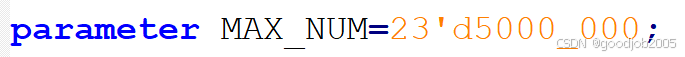

100ms/20ns=5000_000,换算成二进制是23位

因为正点原子的板子频率是50MHZ,换算成时间是20ns

计数器主要部分1,大致意思就是计数到100ms了就反转flag

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

537

537

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?