1、SelectIO逻辑资源描述的是I/O驱动器和接收器背后的逻辑。

2、Xilinx-7系列包括的逻辑资源有:

组合输入/输出

3态输出控制

寄存器输入/输出

寄存器3态输出控制

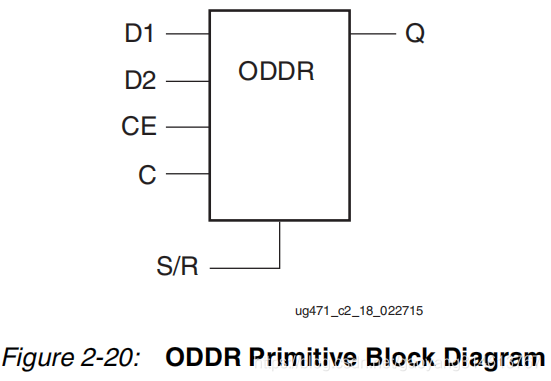

双倍速率输入/输出

双倍速率输出三态控制

IDELAY(输入延时)

ODELAY(输出延时)

SAME_EDGE输出双倍速率模式

SAME_EDGE\SAME_EDGE_PIPELINED输入双倍速率模式

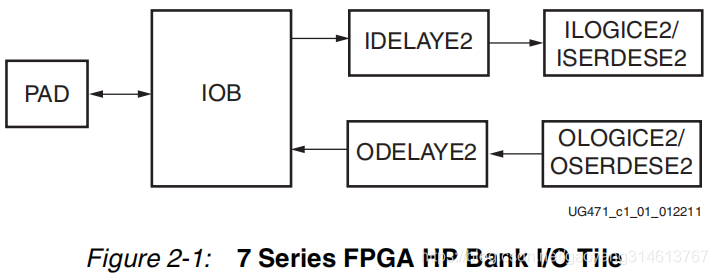

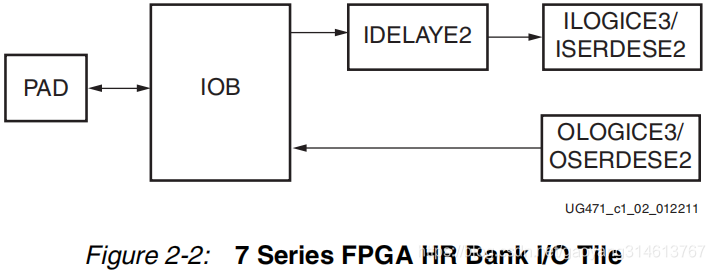

3、I/O tile结构如图所示:

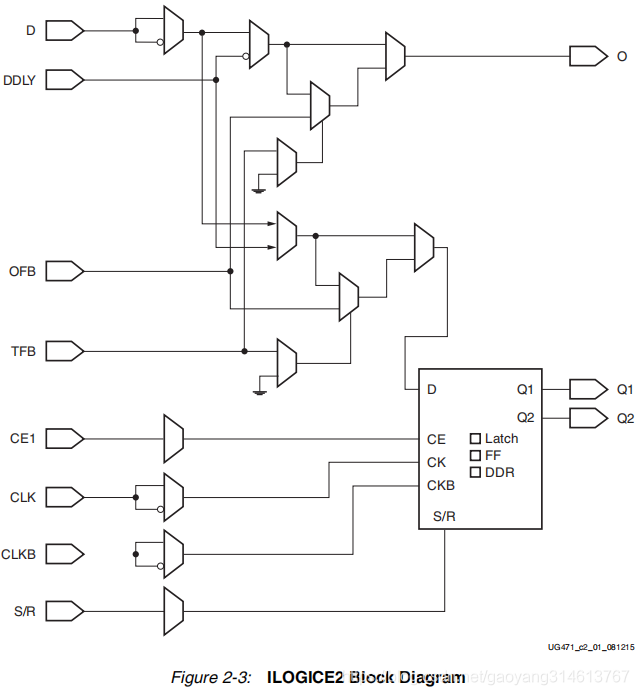

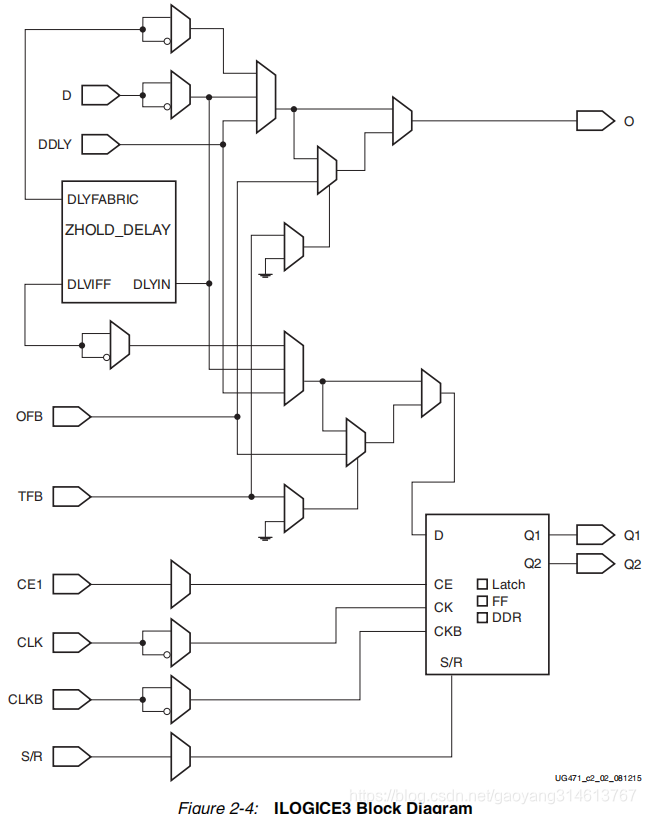

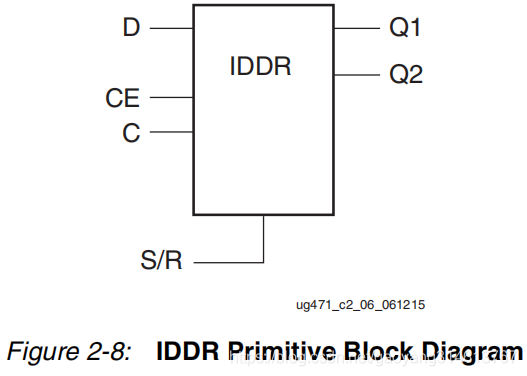

4、ILOGICE2/ILOGICE3(ILOGICE2/ILOGICE3并不是原语,不能例化),支持以下操作:

Edge-triggered D-type flip_flop(边沿触发D类触发器)

IDDR mode(OPPOSITE_EDGE or SAME_EDGE or SAME_EDGE_PIPELINED)

Level sensitive latch(电平敏感锁存器)

Asynchronous/combinatorial(异步输入/组合输入)

在7系列芯片中有专用的IDDR寄存器,可以通过原语来实例化:

| 端口名 | 功能 | 描述 |

| Q1/Q2 | 数据输出 | IDDR寄存器输出 |

| C | 输入时钟 | |

| CE | 时钟使能 | 高电平使能 |

| D | 数据输入(DDR) | IDDR寄存器输入,IOB驱动 |

| S/R | Set/Reset | 高电平有效 |

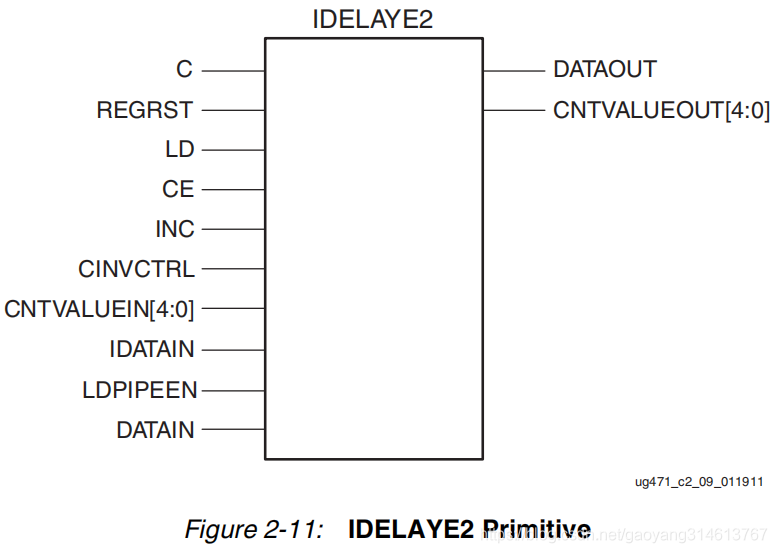

5、IDELAY(输入延时资源)

| 端口名 | 方向 | 位宽 | 描述 |

| C | Input | 1 | VARIABLE,VAR_LOAD,VAR_LOAD_PIPE模式下的时钟输入 |

| REGRST | Input | 1 | VAR_LOAD_PIPE模式下的复位信号 |

| LD | Input | 1 |

VARIABLE mode:加载预编程值 VAR_LOAD mode:加载CNTVALUEIN的值 VAR_LOAD_PIPE mode:加载当前流水线寄存器的值 |

| CE | Input | 1 | 在VARIABLE、VAR_LOAD、VAR_LOAD_PIPE模式下使能INC/DEC功能;高电平有效 |

| INC | Input | 1 | 1:INC; 0:DEC |

| CINVCTRL | Input | 1 | 动态切换时钟引脚(C)的极性 |

| CNTVALUEIN | Input | 5 | 计数器输入 |

| IDATAIN | Input | 1 | 数据输入;来自IBUF |

| DATAIN | Input | 1 | 数据输入;来自FPGA logic |

| LDPIPEEN | Input | 1 | 使能流水线寄存器加载数据 |

| DATAOUT | Output | 1 | 延时数据输出 |

| CNTVALUEOUT | Output | 5 | 计数器输出 |

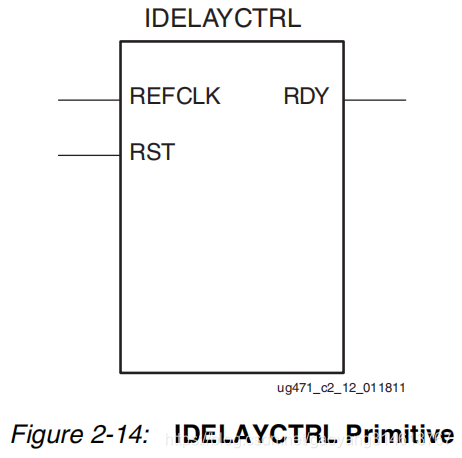

6、IDELAYCTRL(输入延时控制器)

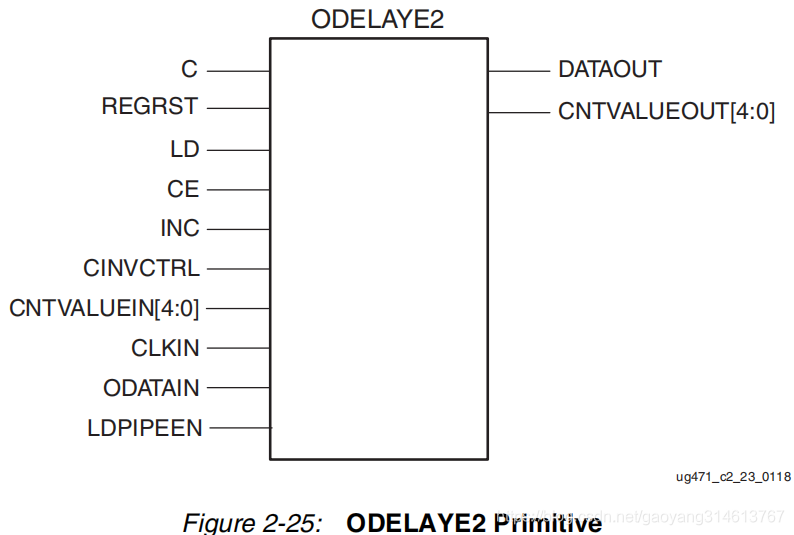

如果例化了IDELAYE2或ODELAYE2,IDELAYCTRL模块也必须例化。IDELAYCTRL模块用于校准延时抽头。

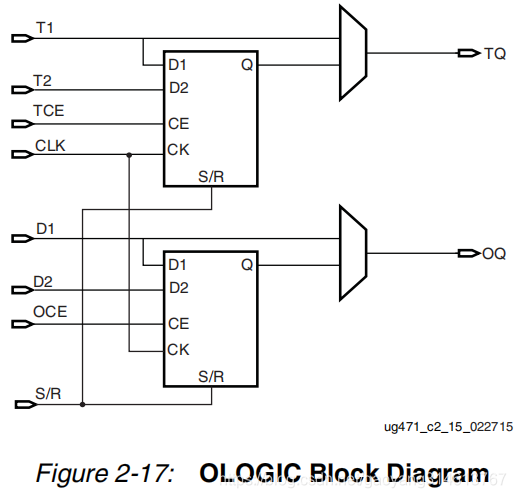

7、OLOGIC(输出逻辑)

8、ODELAY(输出延时)

本文深入解析Xilinx-7系列FPGA中I/O逻辑资源的特性与应用,涵盖组合输入/输出、3态输出控制、IDELAY、ODELAY等关键资源,以及IDDR模式和I/Otile结构,为设计者提供全面的技术指导。

本文深入解析Xilinx-7系列FPGA中I/O逻辑资源的特性与应用,涵盖组合输入/输出、3态输出控制、IDELAY、ODELAY等关键资源,以及IDDR模式和I/Otile结构,为设计者提供全面的技术指导。

2322

2322

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?