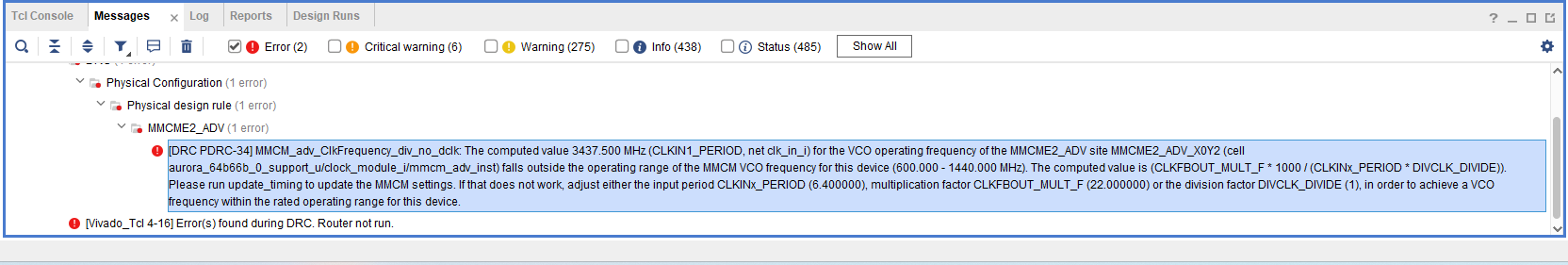

- [DRC PDRC-34] MMCM_adv_ClkFrequency_div_no_dclk: The computed value 3437.500 MHz (CLKIN1_PERIOD, net clk_in_i) for the VCO operating frequency of the MMCME2_ADV site MMCME2_ADV_X0Y2 (cell aurora_64b66b_0_support_u/clock_module_i/mmcm_adv_inst) falls outside the operating range of the MMCM VCO frequency for this device (600.000 - 1440.000 MHz). The computed value is (CLKFBOUT_MULT_F * 1000 / (CLKINx_PERIOD * DIVCLK_DIVIDE)). Please run update_timing to update the MMCM settings. If that does not work, adjust either the input period CLKINx_PERIOD (6.400000), multiplication factor CLKFBOUT_MULT_F (22.000000) or the division factor DIVCLK_DIVIDE (1), in order to achieve a VCO frequency within the rated operating range for this device.

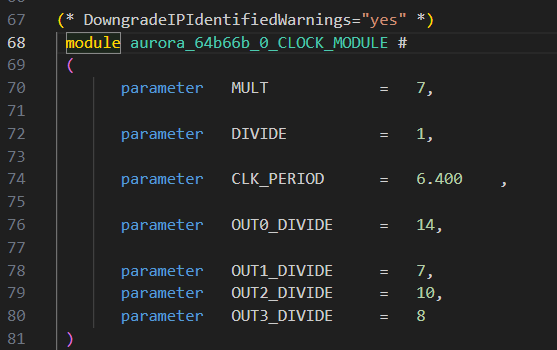

- 根据以上报错提示,找到相应的模块,我的工程对应的是以下模块,(aurora_64b66b_0_support_u/clock_module_i/mmcm_adv_inst),打开例化后的模块发现该模块内部还例化有一个mmcm,于是根据提示去修改参数,问题得以解决!

上图所示的参数会根据aurora IP核配置的线速率以及参考时钟发生变化,可以打开不同配置的IP核对应的示例工程进行修改。

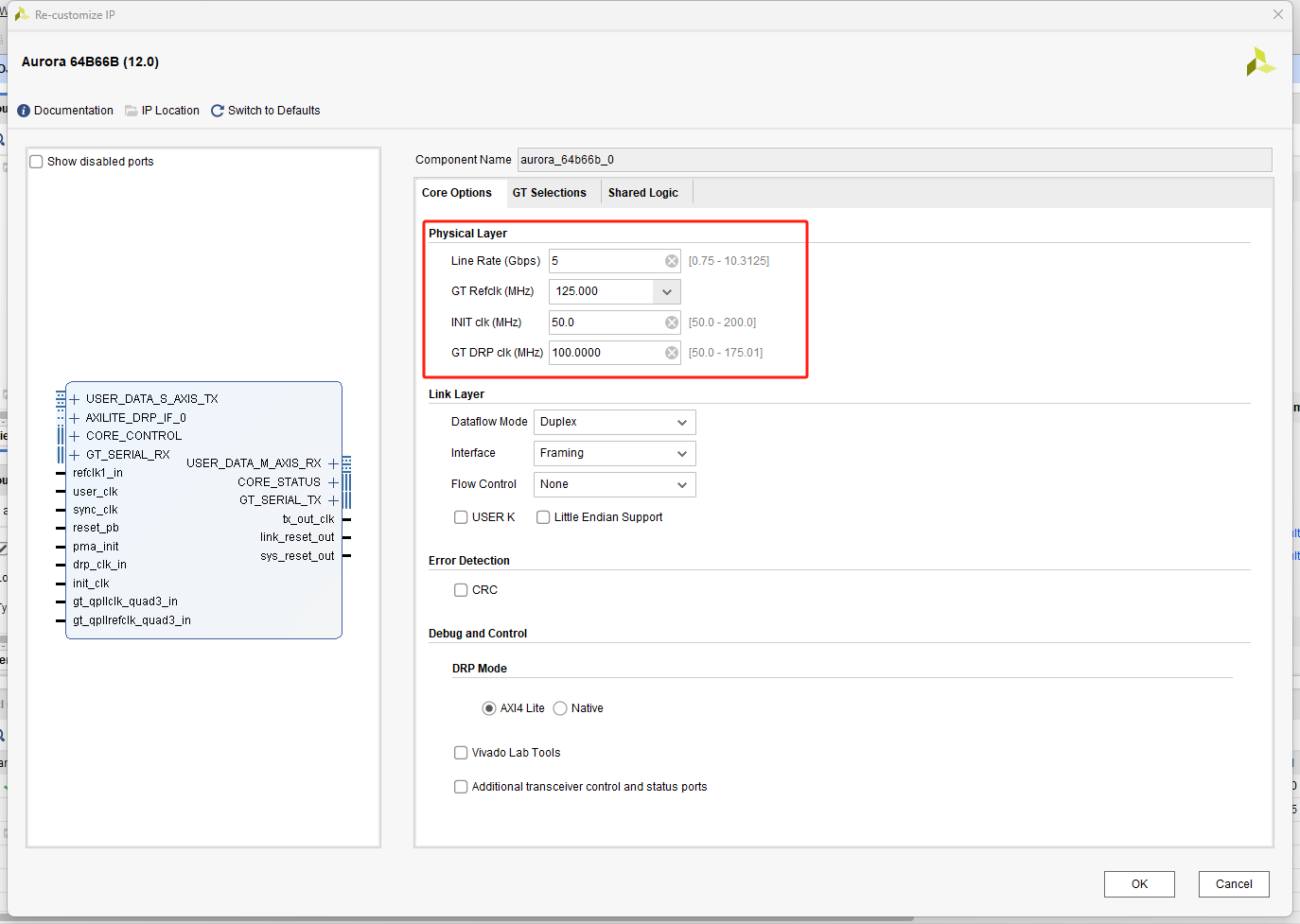

上图所示的参数会根据aurora IP核配置的线速率以及参考时钟发生变化,可以打开不同配置的IP核对应的示例工程进行修改。 - 我的aurora IP核配置如下所示:线速率5Gbps,gt参考时钟125Mhz,只有线速率和参考时钟会影响上面的参数选择,所以只需要注意这两点即可,然后打开对应的示例工程,查看对应的示例工程进行参数修改即可!

赛灵思FPGA开发之aurora64b/66b问题记录,[DRC PDRC-34] 报错!

该文章已生成可运行项目,

本文章已经生成可运行项目

8442

8442

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?