FPGA教程系列-Vivado中乘法器不同模式资源对比

在乘法器的IP核中,有两种实现方式,使用查找表(LUT) 还是专用乘法器原语来实现核心,现在主要进行一个对比。

编写Top文件

直接例化一个乘法器即可。

`timescale 1ns / 1ps

module mult_top(

input clk,

input rst,

input signed [17:0] data_a,

input signed [17:0] data_b,

output signed [35:0] out

);

mult_gen_0 your_instance_name (

.CLK(clk), // input wire CLK

.A(data_a), // input wire [17 : 0] A

.B(data_b), // input wire [17 : 0] B

.P(out), // output wire [35 : 0] P

.SCLR(rst)

);

endmodule

编写Testbench

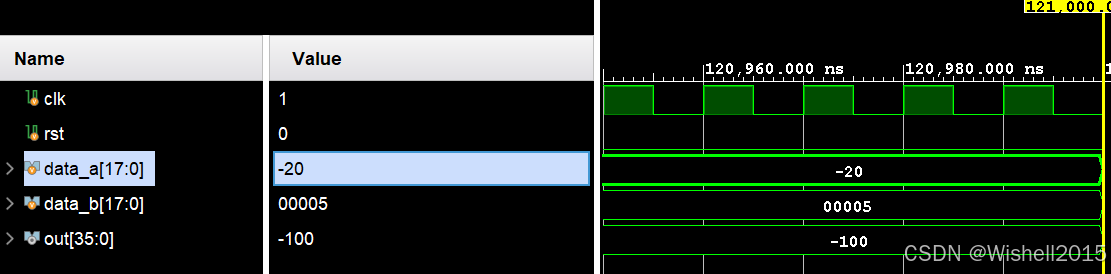

简单的乘法,-20×5=-100.

`timescale 1ns / 1ps

module mult_top_tb;

reg clk;

reg rst;

reg signed[17:0] data_a;

reg signed[17:0] data_b;

wire signed[35:0] out;

mult_top mult_top_u1 (

.clk(clk),

.rst(rst),

.data_a(data_a),

.data_b(data_b),

.out(out)

);

initial

begin

clk = 1'b1;

rst = 1'b1;

data_a = 18'd0;

data_b = 18'd0;

#1000

rst = 1'b0;

data_a = -20;

data_b = 5;

end

always #5 clk=~clk;

endmodule

先看仿真结果

与预期相符。

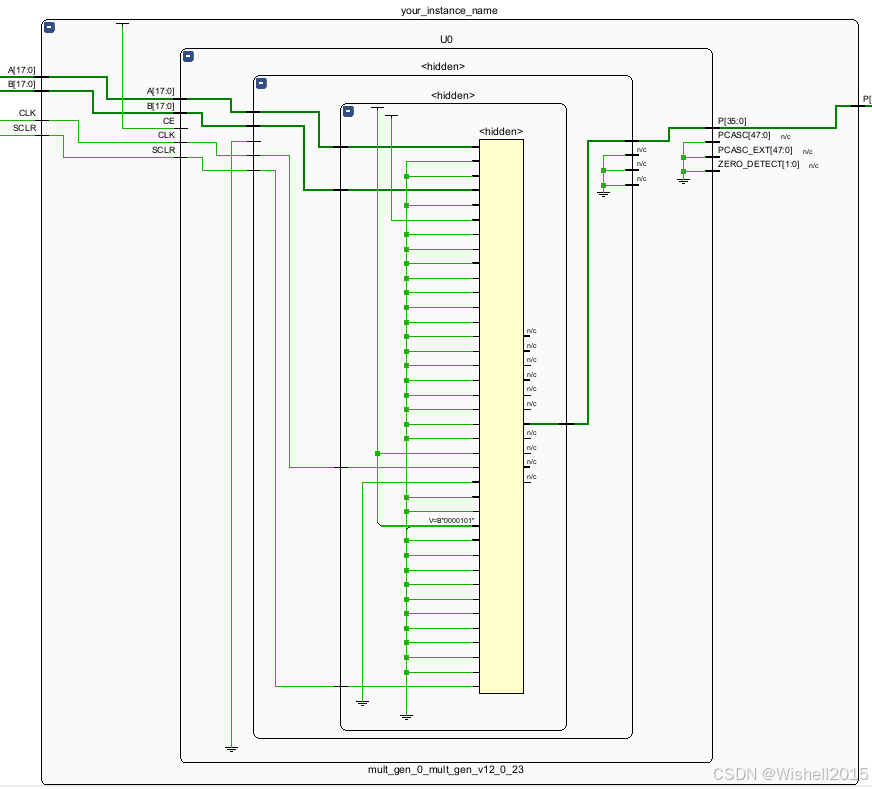

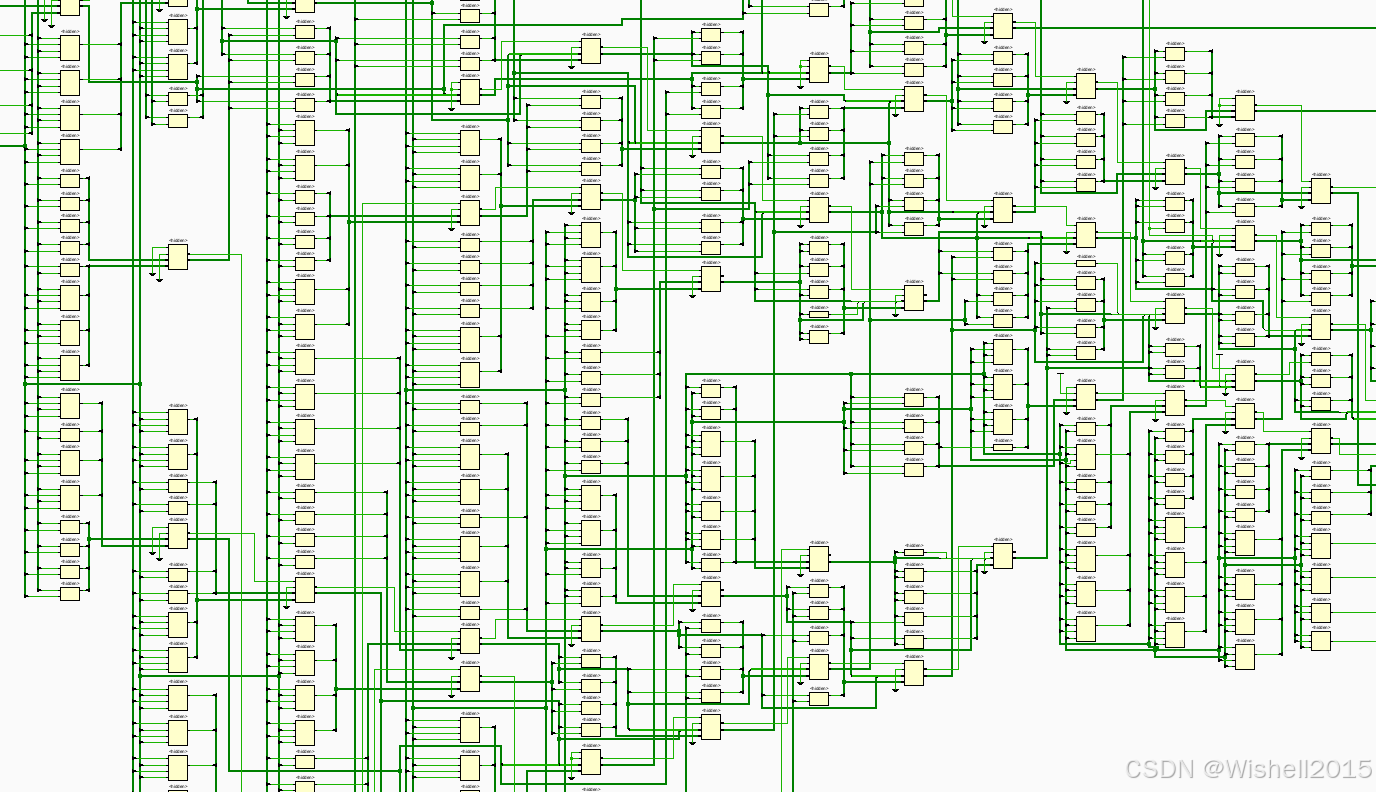

根据IP核的datasheet中的内容,可以知道,两种方式实现的方式不一致,具体的视觉化的内容可以综合以后看到:

专用乘法器原语结果:

查找表(LUT)结果:(密密麻麻)

工程文件:https://download.youkuaiyun.com/download/fantasygwh2015/92261251

3449

3449

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?