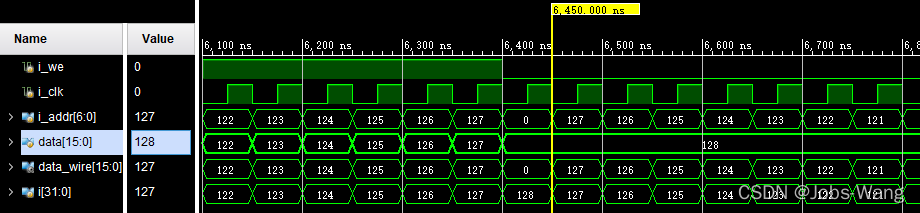

空间为128*16的ram,数据端口为inout端口

模块程序:

`timescale 1ns / 1ps

module ram_tri(

input i_we,i_clk,

input [6:0] i_addr,

inout [15:0] io_data

);

reg [15:0] mem [127:0];

always @ (posedge i_clk)

if(i_we)

mem[i_addr]<=io_data;

assign io_data=(!i_we)? mem[i_addr]:8'hzz;

endmodule

激励文件:

`timescale 1ns / 1ps

module test_ram();

reg i_we;

reg i_clk;

reg [6:0] i_addr;

reg [15:0] data;

wire [15:0] data_wire;

ram_tri test(

.i_we(i_we),

.i_clk(i_clk),

.i_addr(i_addr),

.io_data(data_wire)

);

integer i;

initial begin

i_clk=1'b0;

i_we=1'b1;//写

i_addr=7&#

这篇博客介绍了如何在Verilog中使用inout端口来设计一个128x16位的RAM,并提供了详细的模块程序和激励文件。在模块中,当写使能i_we为高时,数据存入内存;反之,当i_we为低时,从内存读取数据。测试激励文件模拟了数据的写入和读取过程。

这篇博客介绍了如何在Verilog中使用inout端口来设计一个128x16位的RAM,并提供了详细的模块程序和激励文件。在模块中,当写使能i_we为高时,数据存入内存;反之,当i_we为低时,从内存读取数据。测试激励文件模拟了数据的写入和读取过程。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?