PLL生成的时钟输出到普通IO的处理

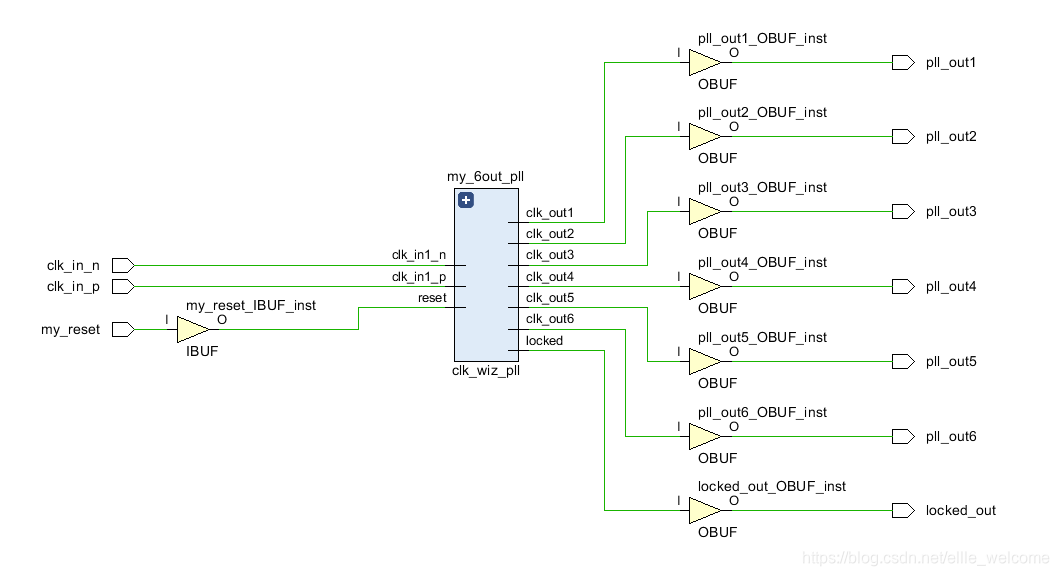

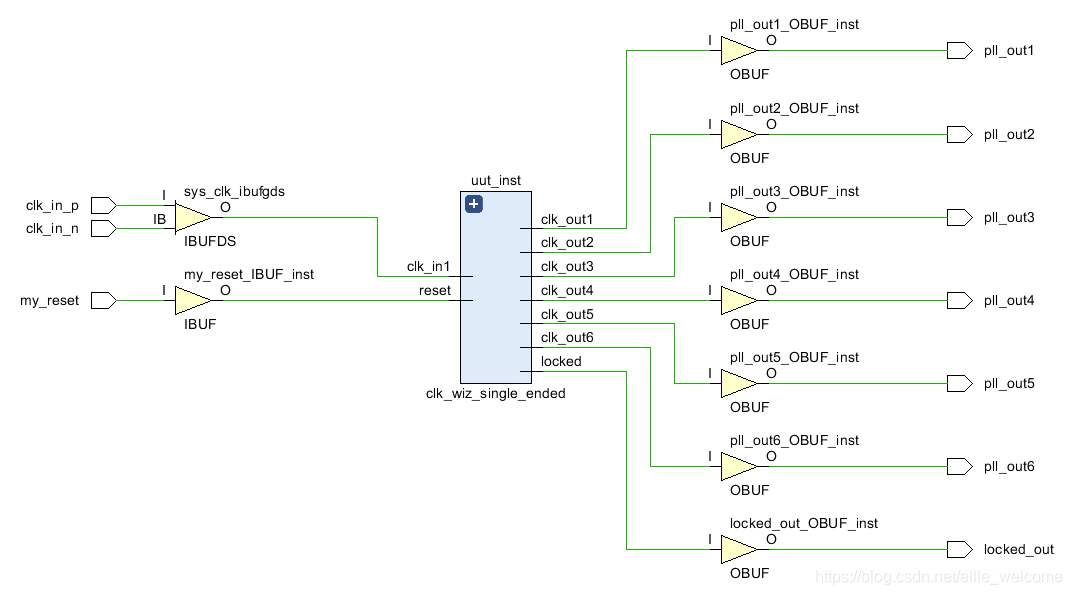

不管是differential clock capable pin(差分) 和single ended clock capable pin(单端)输入PLL产生的时钟输出pll_out1~6都可以直接给FPGA的其它模块使用,但如果要接入普通的IO接口,这需要经ODDR模块稍加处理下。

不管是differential clock capable pin(差分) 和single ended clock capable pin(单端)输入PLL产生的时钟输出pll_out1~6都可以直接给FPGA的其它模块使用,但如果要接入普通的IO接口,这需要经ODDR模块稍加处理下。

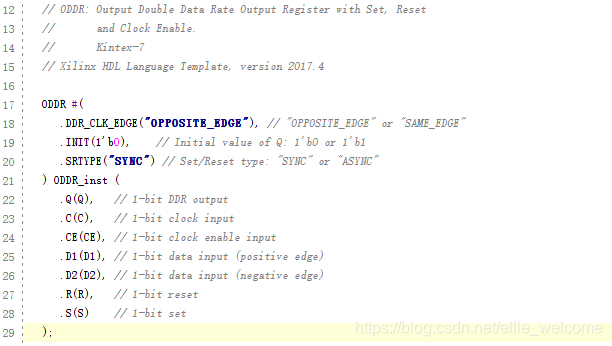

ODDR模块原语如下:

如果需要哪个时钟输出到IO,则将相应的输出时钟如pll_out1输入到 ODDR 原语中,得到IO_clk_out时钟输出,能够输出到FPGA 的普通 IO。

PLL生成的时钟输出,如pll_out1~6,可以直接供FPGA内部模块使用,但若要输出到普通IO,需通过ODDR模块处理。直接从BUFG连接到OBUF会导致编译错误,而使用ODDR可以避免这个问题,虽然会增加时延和抖动。pll_out6经过ODDR处理后可用于普通IO,便于波形测试。

PLL生成的时钟输出,如pll_out1~6,可以直接供FPGA内部模块使用,但若要输出到普通IO,需通过ODDR模块处理。直接从BUFG连接到OBUF会导致编译错误,而使用ODDR可以避免这个问题,虽然会增加时延和抖动。pll_out6经过ODDR处理后可用于普通IO,便于波形测试。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

579

579

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?