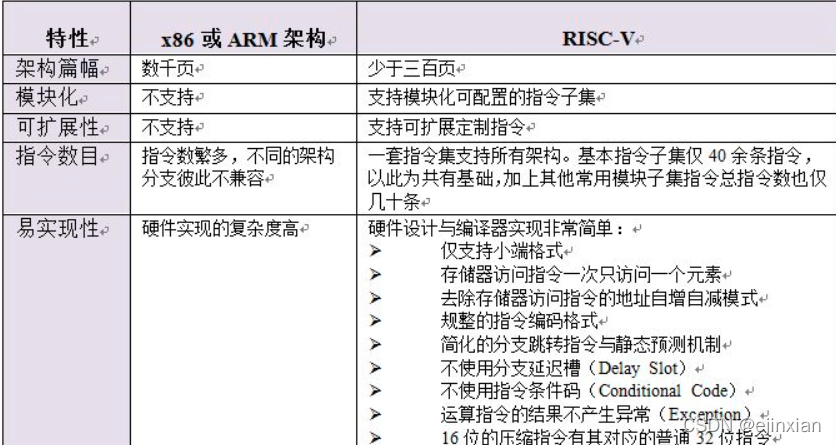

RISC-V(发音为“risk-five”)是一个基于精简指令集(RISC)原则的开源指令集合(ISA)

RISC-V指令集的设计考虑了小型、快速、低功耗的现实情况来实做,但并没有对特定的微架构做过度的设计。

V表示为第五代RISC(精简指令集计算机),表示此前已经四代RISC处理器原型芯片;

采用 Chisel 硬件设计语言开发,支持 RV64GC 指令集,

Chisel是由伯克利大学发布的一种开源硬件构建语言,通过使用高度化的参数生成器和分层的专用硬件设计语言来支持高级硬件设计。

重要特性:

内嵌Scala编程语言

层次化+面向对象+功能构建

使用Scala中的元编程可以高度地参数化

支持专用设计语言的分层

生成低级Verilog设计文件,传递到标准ASIC或FPGA工具

RISC-V是一个开源的指令集架构,专注于精简、高效和低功耗。它不绑定特定的微架构,支持RV64GC指令集,并使用Chisel硬件设计语言进行开发。Chisel是一种内嵌Scala编程语言的硬件构建工具,提供层次化、面向对象和高度参数化的设计能力,最终生成低级Verilog设计文件。RISC-V的开放性和模块化设计使其成为未来处理器设计的重要选择。

RISC-V是一个开源的指令集架构,专注于精简、高效和低功耗。它不绑定特定的微架构,支持RV64GC指令集,并使用Chisel硬件设计语言进行开发。Chisel是一种内嵌Scala编程语言的硬件构建工具,提供层次化、面向对象和高度参数化的设计能力,最终生成低级Verilog设计文件。RISC-V的开放性和模块化设计使其成为未来处理器设计的重要选择。

2033

2033

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?