高速先生成员-- 黄刚

这到底是在描述一种什么样的设计场景呢?其实是我们在高速设计中一个很典型的case。一般来说,芯片到芯片的高速链路中间都会有AC耦合电容,作用说了500多次了,这里就不重复了哈。由于AC耦合电容一般会放在靠近接收端,刚好在这个区域会和另外一个方向来的高速信号进行汇集,所以我们经常会看到下面这样的电容和高速走线交汇的设计。

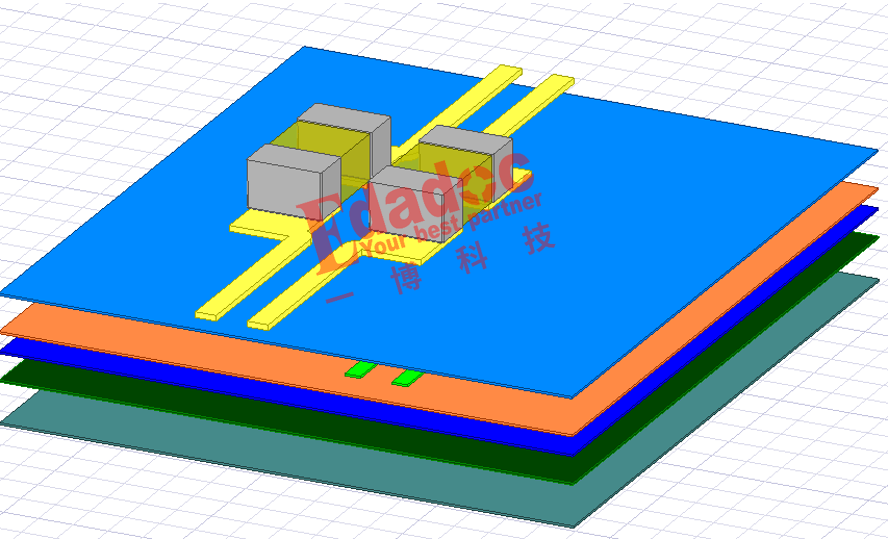

今天要分析的就是它!AC耦合电容在表层,然后高速走线在L3层,中间L2层是地平面的这种情况。那就回到了题目和摘要说的问题了,根据电磁场理论,电容在表层,走线在L3层,如果中间的L2层是个完整的参考平面的话,表层的电容及走线和L3层的走线之间是不存在串扰的,因为电磁场没有交集。

但是凡事都不能往理想的情况去想。理论肯定是对的嘛,关键重点是要L2层是个“完整”的参考平面,什么是完整呢?就像上面那个电容的3D模型图,L2层的平面就是完整了啊,所以电容和走线就是没串扰啊!但是串扰是没了,只不过让电容链路的信号质量承担了所有。

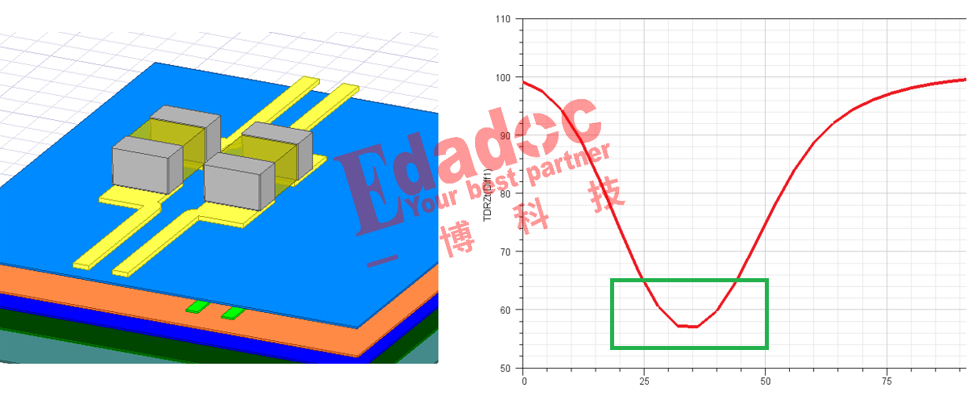

我们知道,电容结构本身的焊盘比较宽,那么阻抗如果参考L2层那么近的话,阻抗肯定是低的,就像上面这个模型一样,如果只参考L2层地平面的话,阻抗只有60欧姆左右。对,你没听错,100欧姆的差分,电容位置的阻抗只有60欧姆!

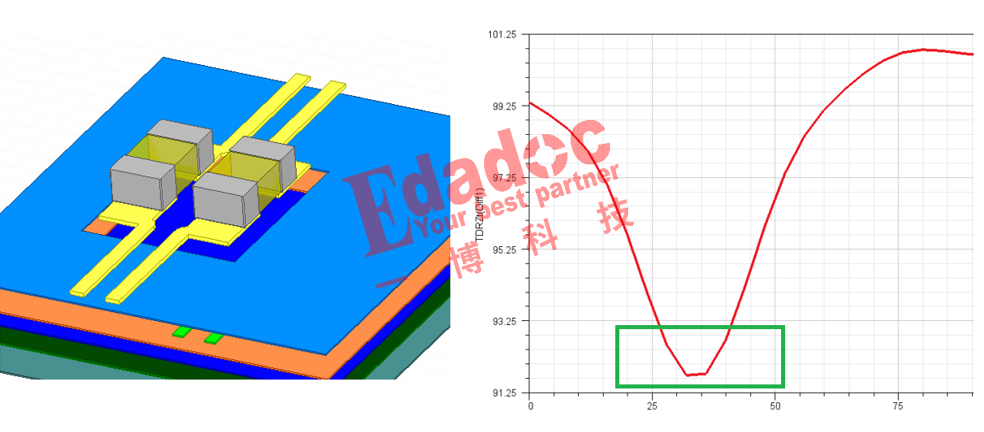

那当然不行啊!这样反射很大,信号质量估计差到没边啦!所以我们针对电容结构去优化的最佳方案就是挖空电容下面的参考层,例如通过仿真给出以下的一个反焊盘挖空方案,这样的话,电容结构的阻抗就能做到90欧姆以上了!

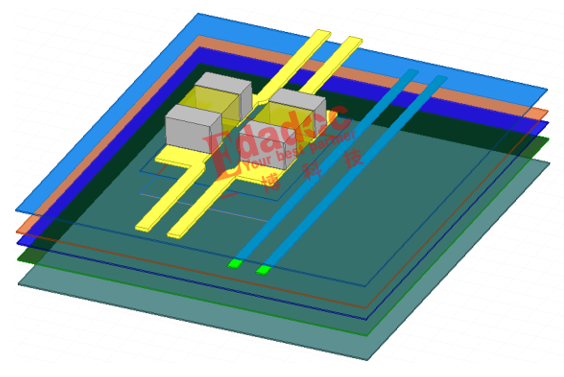

完美!电容结构本身的信号质量优化得杠杠的了!但是问题不就来了嘛,L2层由于挖空了地平面,变成了不完整的平面了,这样的话表层的电容和L3层的走线就不是之前的没串扰的状态了哦。从下图可以发现,表层的电容和L3层的走线就会通过L2层的这个挖空的区域产生电磁场的交集,也就是会有串扰产生了!

但是,在设计中,这是个电容放置的密集区域,可能会有几十对高速链路,也就是并排放着几十对电容,L3层的高速线能挪开的空间肯定也不大。那我们前期去评估这种挖空case下电容和高速走线间的串扰量级就非常的有意义了,可以指导我们走线到底拉开多少距离能满足串扰的要求。

以下动图是走线在垂直方向上从近到远拉开距离的设计过程:

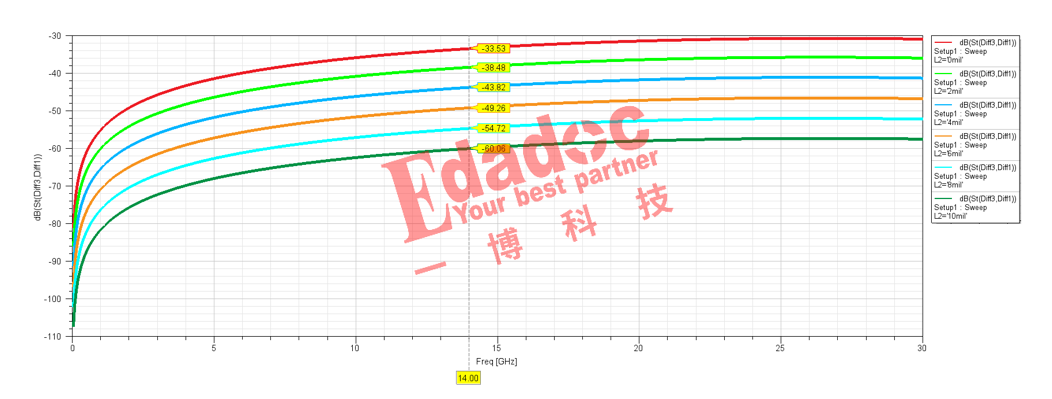

那我们同步也去扫描仿真的结果,从0mil(也就是贴着反焊盘边缘)到拉开10mil垂直距离,串扰的变化如下所示:

可以看到,要是走线贴着反焊盘边缘时,对于25Gbps的高速信号,串扰只有33dB,比较不理想。然后每拉开多2mil,串扰大概能改善5dB,是一个很不错改善幅度。

这里其实有2个问题是值得关注的,从信号质量的角度看,肯定就是拉开的距离越远,串扰的改善越明显,但是到底有没有那么多垂直空间给你拉开,这个要根据这个项目的空间密度来权衡了。另外一个方面,可能大家不一定想到,那就是加工层偏的影响。一般的板厂加工的层偏误差都会有4mil以上,尤其是高多层的情况下,这个值会更大。结合到我们今天讲的这个case,有可能你在设计中是拉开了4mil的距离,但是加工层偏又会导致你回到0mil的串扰状态。更极限的是,如果本身设计就是贴着反焊盘,也就是0mil的设计,那加工出来可能变成了-4mil,也就是走线之间到了反焊盘区域里面了,这样串扰就更恐怖了。So。。。我们千万不要忽视加工误差的影响,选择一个好的板厂,能给大家承诺最小的层偏误差,这样也能给大家的设计留出更多的裕量的哦!

AC耦合电容与高速线串扰解析

AC耦合电容与高速线串扰解析

1920

1920

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?