写在前面

本系列文章主要讲解德州仪器(TI)TDA4VM芯片的相关知识,希望能帮助更多的同学认识和了解德州仪器(TI)TDA4VM芯片。

若有相关问题,欢迎评论沟通,共同进步。(*^▽^*)

错过其他章节的同学可以电梯直达目录↓↓↓

TDA4VM芯片

5. PIN定义

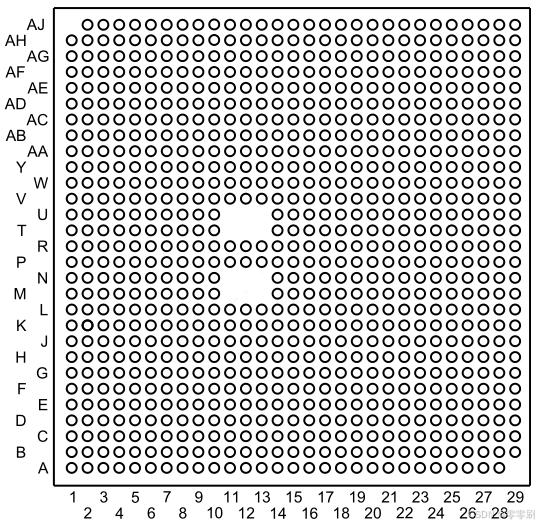

如图2示意了FCBGA-N827封装的PIN脚定义。

图 2 FCBGA-N827封装PIN脚定义(底部视角)

6. 时序和开关特性

6.1 时序参数和信息

表2是时间参数下标说明,如表所示。

| 缩写 |

参数 |

| c |

Cycle time (period) |

| d |

Delay time |

| dis |

Disable time |

| en |

Enable time |

| h |

Hold time |

| su</ |

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1217

1217

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?