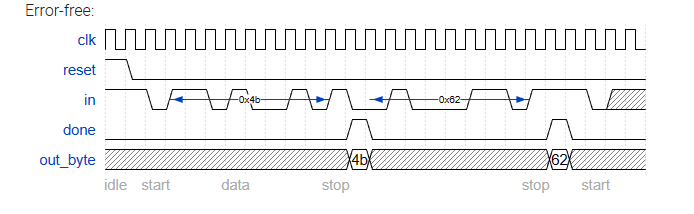

Now that you have a finite state machine that can identify when bytes are correctly received in a serial bitstream, add a datapath that will output the correctly-received data byte. out_byte needs to be valid when done is 1, and is don't-care otherwise.

Note that the serial protocol sends the least significant bit first.

module top_module(

input clk,

input in,

input reset, // Synchronous reset

output [7:0] out_byte,

output done

); //

parameter IDLE = 3'b000,

START = 3'b001,

TRANS = 3'b011,

END = 3'b010,

ERR = 3'b110;

reg [2:0] state, next_state;

reg [3:0] cnt_data;

// Use FSM from Fsm_serial

always@ (*)

case (state)

IDLE:

if(~in)

next_state <= START;

else

next_state <= IDLE;

START:

next_state <= TRANS;

TRANS:

if(cnt_data == 4'd8) begin

if(in)

next_state <= END;

else

next_state <= ERR;

end

else

next_state <= TRANS;

END:

if(in)

next_state <= IDLE;

else

next_state <= START;

ERR:

if(in)

next_state <= IDLE;

else

next_state <= ERR;

default:

next_state <= IDLE;

endcase

always@ (posedge clk)

if(reset)

state <= IDLE;

else

state <= next_state;

always@ (posedge clk)

if(reset)

cnt_data <= 4'b0;

else if(next_state == START)

cnt_data <= 4'b0;

else if(next_state == TRANS)

cnt_data <= cnt_data + 1'd1;

else

cnt_data <= cnt_data;

always@ (posedge clk)

if(reset)

done <= 0;

else if(next_state == END)

done <= 1;

else

done <= 0;

always@ (posedge clk)

if(reset)

out_byte <= 8'd0;

else if(next_state == IDLE)

out_byte <= 8'd0;

else if(next_state == TRANS )

out_byte <= {in,out_byte[7:1]};

else

out_byte <= out_byte;

endmodule

该文章描述了一个使用有限状态机(FSM)来检测串行比特流中正确接收到的数据的模块。模块根据输入和计数器状态,将正确接收到的字节输出并设置`done`标志。FSM处理START,TRANS,END和ERROR状态以确保数据传输的正确性。

该文章描述了一个使用有限状态机(FSM)来检测串行比特流中正确接收到的数据的模块。模块根据输入和计数器状态,将正确接收到的字节输出并设置`done`标志。FSM处理START,TRANS,END和ERROR状态以确保数据传输的正确性。

867

867

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?