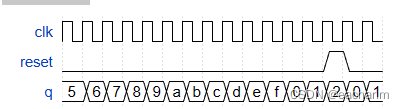

Build a 4-bit binary counter that counts from 0 through 15, inclusive, with a period of 16. The reset input is synchronous, and should reset the counter to 0.

module top_module (

input clk,

input reset, // Synchronous active-high reset

output [3:0] q);

always @ (posedge clk)

if(reset == 1'b1)

q <= 4'b0;

else if(q == 4'd15)

q <= 4'd0;

else

q <= q + 1'd1;

endmodule

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?