Verilog模型可以是实际电路的不同级别的抽象。这些抽象的级别和它们所对应的模型类型共有以下5种:系统级、算法级、RTL级、门级、开关级

‘bz :表示高阻态, ’bx表示不定值(0或1均可)

`include "muxtwo.v" 将文件引进

{$ random} 为系统任务,会产生一个随机数,

in = {$random} % 2; //产生0到2(0或1) 的随机数in = $random % b; //b为十进制整数,in为范围在 -(b-1):(b-1) 中的随机数

而“always”块既可用于描述组合逻辑,也可描述时序逻辑,always块中的语句称为顺序语句,因为他们是顺序执行的

verilog hdl 共有19种数据类型,最基本的4种为reg、wire、integer、parameter

其他的数据类型是:larger, medium,scalared, time, small, tri, trio, tril, triand, trior, trireg、vectored, wand, wor型

利用parameter 来传递参数

//这是子模块//在子模块里面定义了常量width 和height

module decoder(

input wire in,

output wire out)

parameter width = 1;

parameter height = 2;

endmodule

module top (

input wire a,

output wire b

);

//调用子模块并更改里面的常量width 和heigh

decoder

#(

.width (10), //使decoder里面的width = 10

.height (8)

)

decoder_inst(

.in(),

.out()

);

endmodule

用defparam来重定义模块种的值,如defparam module1.module2.module3.a = 0; module1,module2和module3是例化模块的名字

wire型变量通常是用来表示单个门驱动或连续赋值语句驱动的网络型数据,tri型变量则用来表示多驱动器驱动的网络型数据

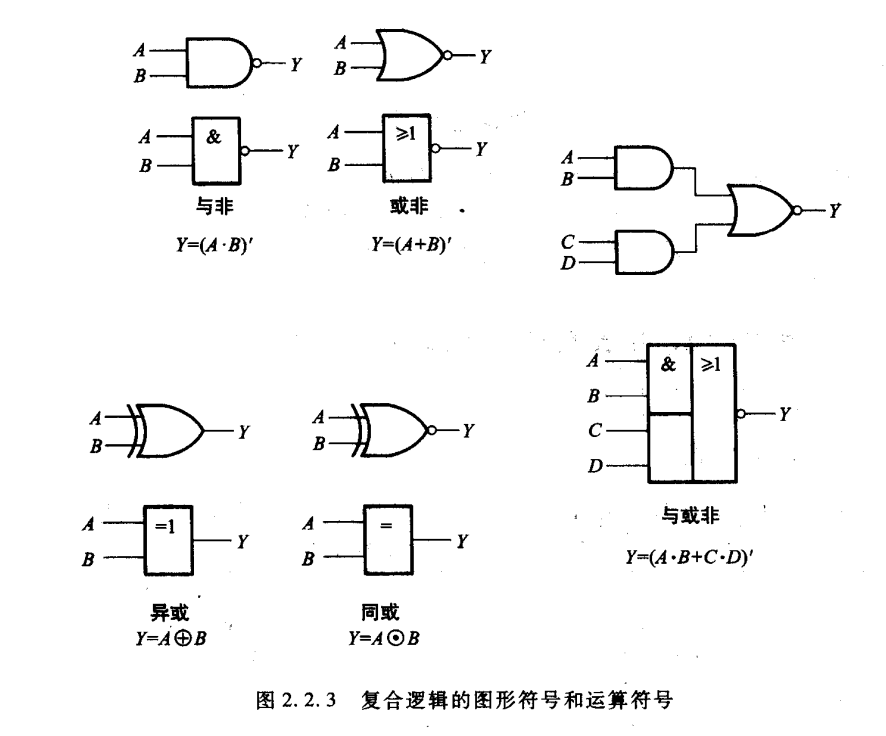

原语:相当于库中的module,直接调用

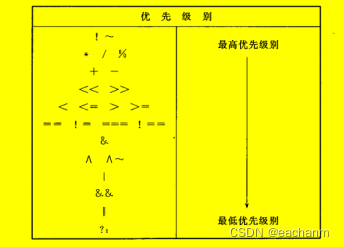

符号优先级:

!是逻辑取反,~是按位取反

时序分析:时序分析的方法主要有两种,一种是静态时序分析,另一种是动态时序分析

静态分析:通过设计好的电路中的已知参数 利用EDA的工具模型分析出时钟和数据的关系。

动态分析: 把设计好的电路中的所有延时都考虑进来,加上EDA中的延时参数,然后观测Ts, Th是否满足要求,需要电路模拟跑起来。

Ts(建立时间:采样时钟的上升沿 到达 数据起始位置的时间)

Th(保持时间:采样时钟的上升沿 到达 数据结束位置的时间)

时序分析需要关心的路径:

1、从输入到输出的路径;

2、从输入到寄存器的路径;

3、从寄存器到输出的路径;

4、从寄存器到寄存器的路径;

5、异步清零信号和时钟存在异步的进入和退出问题。

编辑

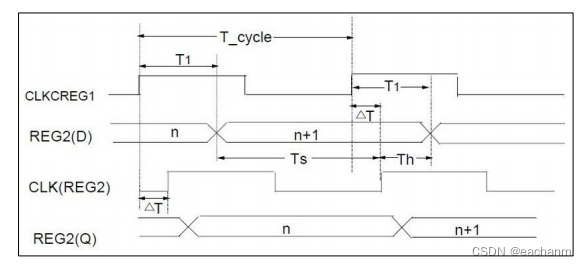

图 中的 T1 为数据路径的延迟,,它包括 寄存器 REG1 时钟端 到 寄存器 REG1 数据输出端 Q 的延迟(Tco) 与 两级寄存器之间的组合逻辑与布线延迟( Tdata) 之和。

图 中的△T 为时钟偏斜,等于时钟到第二级寄存器时钟端的延迟 与 时钟到第一级寄存器的时钟端的延迟 之差。注:△T 的值可以为正值也可以为负 值,一般情况它们之间的差就为一个正值,更容易计算。

另外Ts 为建立时间,Th 为保持时间,T_cycle 为时钟周期

根据波形图所表示的内容可以得出建立保持时间公式的推导,如下所示:

建立时间的公式为:Ts = T_cycle – T1 + △T = T_cycle –(Tco + Tdata)+ △T

保持时间的公式为:T1 – △T = (Tco + Tdata)– △T

第5章:条件语句、循环语句、块语句和生成语句

块语句:

1、顺序块: begin end

(1)块内的语句是按顺序执行的,即只有上面一条语句执行完后下面的语句才能执行。

(2)每条语句的延迟时间是相对于前一条语句的仿真时间而言的。

(3)直到最后一条语句执行完,程序流程控制才跳出该语句块。

2、并行块: fork join

(1)块内语句是同时执行的,即程序流程控制一进入到该并行块,块内语句则开始同时并

行地执行。

(2)块内每条语句的延迟时间是相对于程序流程控制进入到块内的仿真时间的。

(3)延迟时间是用来给赋值语句提供执行时序的。

(4)当按时间时序排序在最后的语句执行完后或一个disable语句执行时,程序流程控制

跳出该程序块。

3、生成块 generate endgenerate

3种生成语句的方法: 循环生成、条件生成、case生成

生成范围内允许声明下列数据类型:

(1)net(线网)、reg(寄存器):

(2)integer(整型数),real(实型数)、time(时间型)、realtime(实数时间型);

(3)event(事件)

不允许出现在生成范围之中的模块项声明包括:

(1)参数、局部参数:

(2)输入、输出和输入/输出声明;

(3)指定块。

生成块的本质是使用循环内的一条语句来代替多条重复的Verilog语句,简化用户的编程。

条件语句

case语句的所有表达式值的位宽必须相等,只有这样,控制表达式和分支表达式才能进

行对应位的比较。一个经常犯的错误是

本文档详尽介绍了Verilog HDL的基础语法、高级特性及应用实践,涵盖从基本语句到复杂数字系统设计的各个方面。内容涉及数据类型、模块定义、时序分析、条件与循环语句、系统任务等,并深入探讨了状态机设计、阻塞与非阻塞赋值的区别、复杂时序逻辑电路的实现等关键主题。

本文档详尽介绍了Verilog HDL的基础语法、高级特性及应用实践,涵盖从基本语句到复杂数字系统设计的各个方面。内容涉及数据类型、模块定义、时序分析、条件与循环语句、系统任务等,并深入探讨了状态机设计、阻塞与非阻塞赋值的区别、复杂时序逻辑电路的实现等关键主题。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

8477

8477

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?