https://aijishu.com/a/1060000000134828

在 AXI3 协议中支持的写数据交织(wirte data interleaving)功能在 AXI4 中不再支持。因此 Interconnect 实现也无需继续支持写交织。

何为写交织

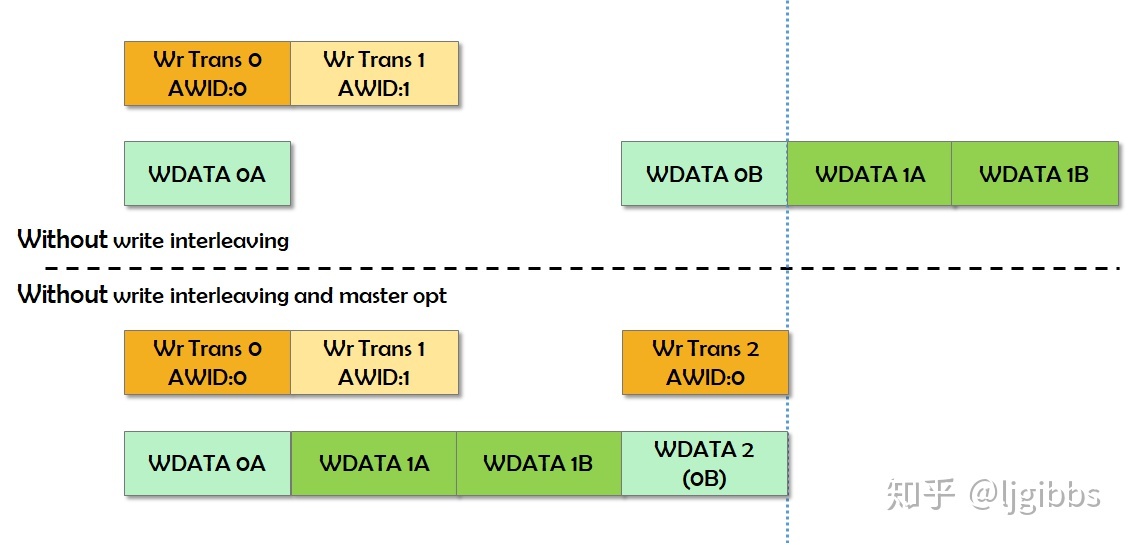

写数据交织指来自不同事务的写数据可以被打散混合排列。如下图中有 2 个写事务,每个写事务共有 2 个写数据 A/B。

当不支持写交织时,写入数据的顺序必须保持为 0A 0B 1A 1B,即一个写事务的数据完成后再传输下一个事务的数据。而交织时顺序可以为 0A 1A 0B 1B 或者 0A 1A 1B 0B,在事务中插入另一事务的数据。

写交织的作用之一在于提高系统的效率,我们对上述场景增加一个假设,事务0 是一个较慢的数据流,每 2 个周期写一个数据。而事务 1 的数据速率更高,每个周期写一个数据。如下图所示,写交织能够减少总线传输中的气泡(空闲时间),提高系统的效率。

为什么不再支持

笔者在网上冲浪了一下,并没有找到直接的解释,个人总结有以下原因:

- 应用场景少

- 设计复杂

- 去除该功能能够简化实现

(1)首先是相较于读交织,写交织仅在多主机场景中有效,应用有限。在单个主机的情况下,可以由主机分拆事务提高效率,而无需应用写交织这一复杂特性。

上图中的场景,假设这 2 个事务来源于同一主机,如下图所示,主机将速度较慢的事务 0 分拆为 2 个事务,每个事务各包括 1 次传输,同样达到了写交织的效率。

由于应用场景有限,因此在 AXI3 实现中,写交织往往也不被支持。ARM 在手册中也承认了这一点:

Most AXI3 masters do not support write interleaving.

(2)写交织设计较为复杂,ARM 在协议中针对写交织做了许多约束,以避免出现死锁等现象。在 A5.3.3 中罗列了一大堆。

(3)既然写交织复杂又不常用,而砍掉该特性能够简化实现,并删去写通道中的 WID 信号,自然是一件喜闻乐见的事。

AXI3协议中的写数据交织功能在AXI4中被移除,主要是因为应用场景有限、设计复杂性和简化实现的需求。写交织在多主机场景下提高效率,但单主机情况下可通过主机分拆事务实现。此外,写交织的设计约束多,可能导致死锁等问题。移除该功能减少了协议复杂性,删除了WID信号。

AXI3协议中的写数据交织功能在AXI4中被移除,主要是因为应用场景有限、设计复杂性和简化实现的需求。写交织在多主机场景下提高效率,但单主机情况下可通过主机分拆事务实现。此外,写交织的设计约束多,可能导致死锁等问题。移除该功能减少了协议复杂性,删除了WID信号。

1万+

1万+