名称:基于FPGA的水卡计价器的设计Verilog代码Quartus仿真(文末获取)

软件:Quartus

语言:Verilog

代码功能:

基于FPGA的水卡计价器的设计

设计基于FPGA水卡计价器的设计,计价分为3、5、10分钟三种费用,3分钟以内10元;5分钟以内,3分钟以外,5元/分钟;10分钟以内,5分钟以外,8元/分钟;要求可以连续计费;用数码管显示当前时间,当前水费和余额。

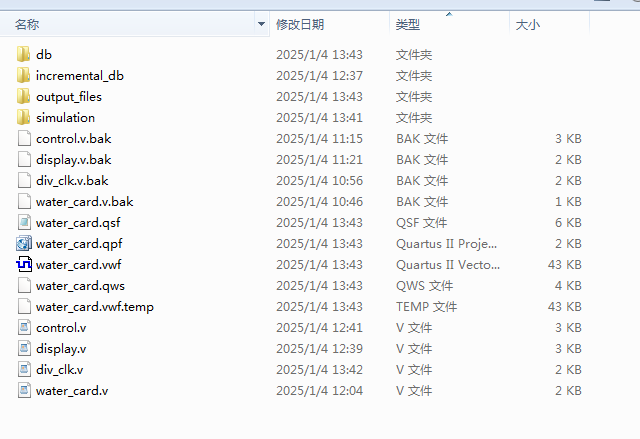

1、工程文件

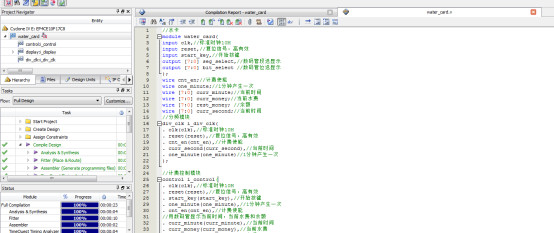

2、程序文件

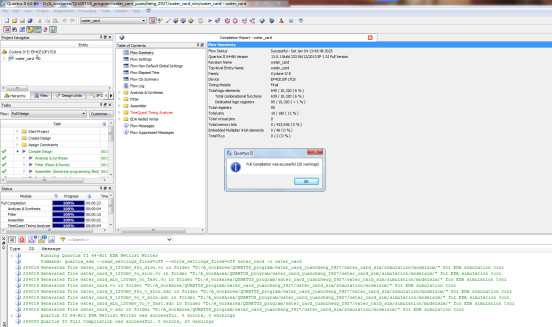

3、程序编译

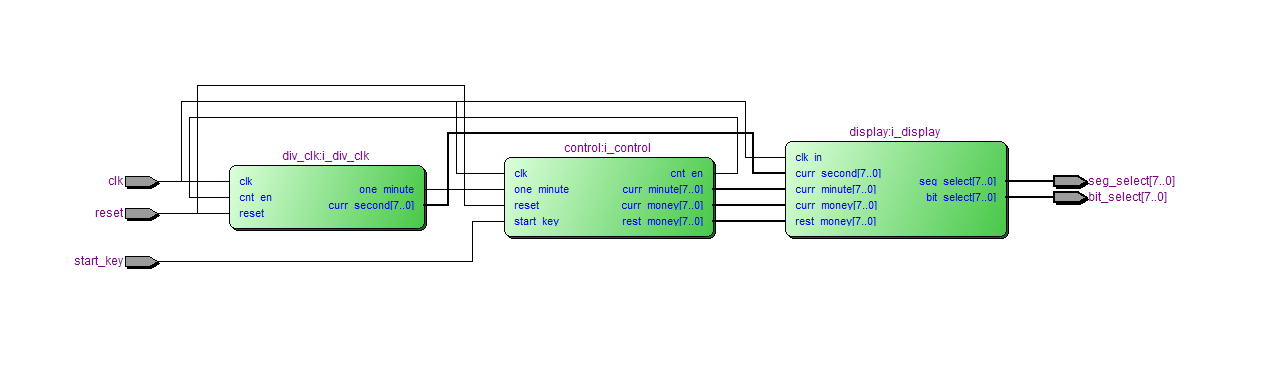

4、RTL图

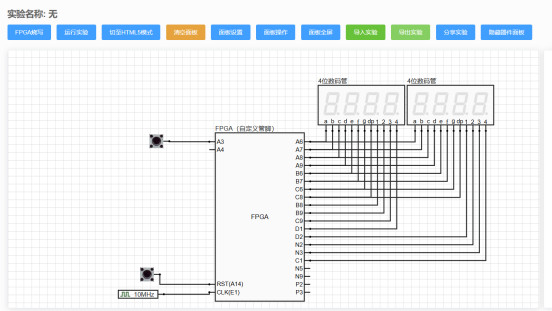

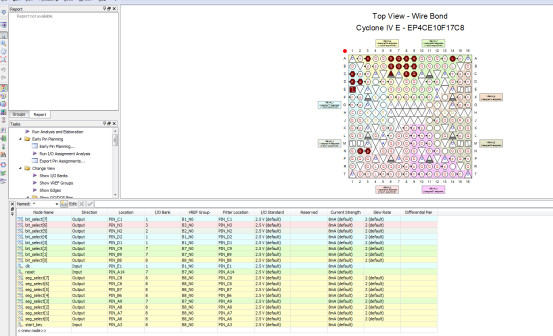

5、管脚分配

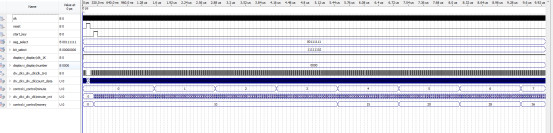

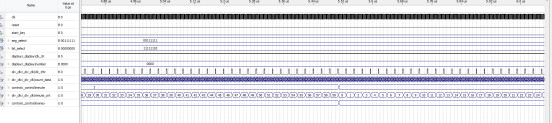

6、仿真图

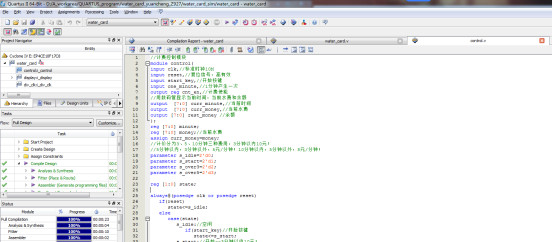

部分代码展示:

//计费控制模块 module control( input clk,//标准时钟10M input reset,//复位信号,高有效 input start_key,//开始按键 input one_minute,//1分钟产生一次 output reg cnt_en,//计费使能 //用数码管显示当前时间,当前水费和余额 output [7:0] curr_minute,//当前时间 output reg [7:0] curr_money,//当前水费 output [7:0] rest_money //余额 ); reg [7:0] minute; //计价分为3、5、10分钟三种费用,3分钟以内10元; //5分钟以内,3分钟以外,5元/分钟;10分钟以内,5分钟以外,8元/分钟; parameter s_idle=2'd0; parameter s_start=2'd1; parameter s_over3=2'd2; parameter s_over5=2'd3; reg [1:0] state;

源代码

点击下方的公众号卡片获取

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?