名称:出租车计费器设计VHDL代码Quartus仿真(文末获取)

软件:Quartus

语言:VHDL

代码功能:

VHDL和Verilog两种语言的出租车计费器

设计与仿真。

2. 程序仿真图

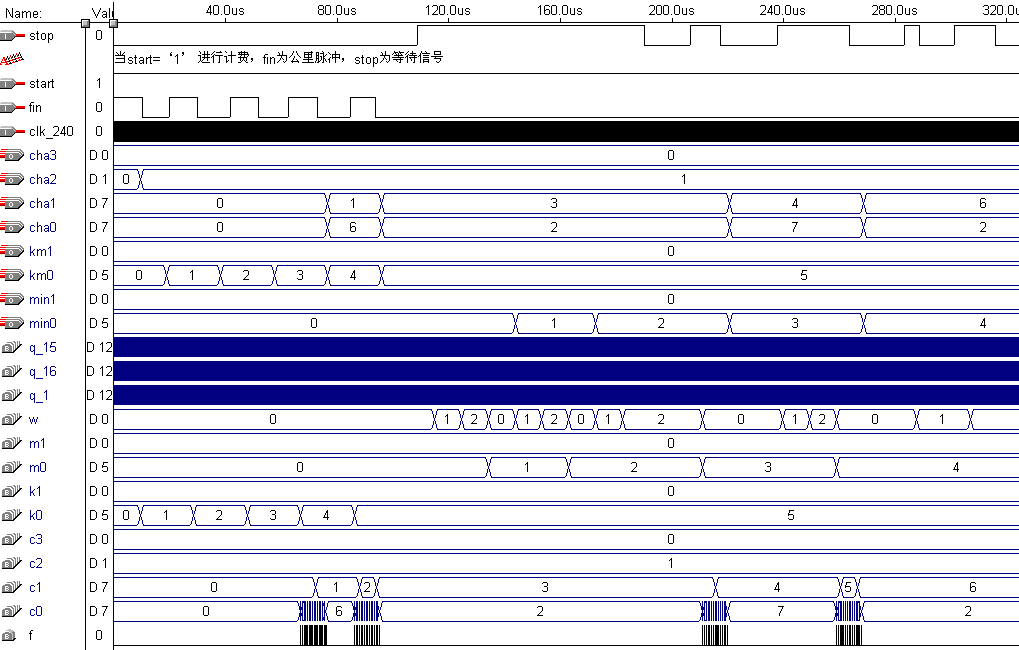

注:1. 仿真图中秒跟分的关系为3进制,即w为2时就归0;

2. 出租车总行驶5公里,等待累计时间为4分钟,总费用为16.2元。

图8.22.3 出租计价器程序仿真全图

部分代码展示:

//功能:出租车计价器 module taxi(clk_240, start, stop, fin, cha3, cha2, cha1, cha0, km1, km0, min1, min0); input clk_240;//频率为240Hz的时钟 input start;//计价使能信号 input stop;//等待信号 input fin;//公里脉冲信号 output [3:0] cha3;//费用数据 output [3:0] cha2;//费用数据 output [3:0] cha1;//费用数据 output [3:0] cha0;//费用数据 output [3:0] km1;//公里数据 output [3:0] km0;//公里数据 output [3:0] min1;//等待时间 output [3:0] min0;//等待时间 reg [3:0] min0; reg f_15;//频率为15Hz,16Hz,1Hz的信号 reg f_16;//频率为15Hz,16Hz,1Hz的信号 reg f_1;//频率为15Hz,16Hz,1Hz的信号 reg [3:0] q_15;//分频器 reg [3:0] q_16;//分频器 reg [7:0] q_1;//分频器 reg [5:0] w;//秒计数器 reg [3:0] c3;//制费用计数器 reg [3:0] c2;//制费用计数器 reg [3:0] c1;//制费用计数器 reg [3:0] c0;//制费用计数器 reg [3:0] k1;//公里计数器 reg [3:0] k0;//公里计数器 reg [2:0] m1;//分的十位计数器 reg [3:0] m0;//分的十位计数器 reg en1;//使能信号 reg en0;//使能信号 reg f;//使能信号 reg [3:0] cha3; reg [3:0] cha2; reg [3:0] cha1; reg [3:0] cha0; reg [3:0] km1; reg [3:0] km0; reg [3:0] min1; always @(posedge clk_240 or negedge start) begin: feipin begin if (start == 1'b0) begin q_15 <= 0; q_16 <= 0; f_15 <= 1'b0; f_16 <= 1'b0; f_1 <= 1'b0; f <= 1'b0; end else begin if (q_15 == 15)//此语句得到频率为15Hz的信号 begin q_15 <= 0; f_15 <= 1'b1; end else begin q_15 <= q_15 + 1; f_15 <= 1'b0; end if (q_16 == 14)//此语句得到频率为16Hz的信号 begin q_16 <= 0; f_16 <= 1'b1; end else begin q_16 <= q_16 + 1; f_16 <= 1'b0; end if (q_1 == 239)//此语句得到频率为1Hz的信号 begin q_1 <= 0; f_1 <= 1'b1; end else begin q_1 <= q_1 + 1; f_1 <= 1'b0; end if (en1 == 1'b1)//此语句得到计费脉冲f f <= f_15; else if (en0 == 1'b1) f <= f_16; else f <= 1'b0; end end end

源代码

点击下方的公众号卡片获取

661

661

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?