0.18ߤ微米CMOS中超低功耗、温度无关无电阻带隙基准电路的设计

摘要

本文提出了一种低功耗无电阻的电压参考电路。该电路采用标准0.18μm CMOS技术进行设计和仿真,能够在输出端提供稳定的参考电压,且不受电源和温度变化的影响。该电路在‐45至125 Ԩ的温度范围内,提供1.15V的参考电压和0.14ࣆ的电流,温度系数为11ppm/Ԩ ,调整线为20%/V,在1.8V电源电压下消耗的功率为0.25ࣆW。

关键词

带隙参考电压,与绝对温度成比例的电压(CTAT),与绝对温度成正比,温度系数和调整线。

I. 引言

近年来,集成电路(IC)技术发展迅速,对低功耗且能在恶劣环境中工作的集成电路的需求也日益增长。主要推动因素是电池供电的便携式设备的广泛应用[3]。在混合信号集成电路设计中,生成精确的电流和电压至关重要,为此通常采用带隙基准电路。这类基准提供直流量,其对电源和工艺参数的依赖性较小,并对温度具有明确的依赖关系[2]。带隙基准电路是许多模拟、数字和混合信号电子器件的基本单元,例如低压差稳压器、高分辨率模数和数模转换器、数字仪表、锁相环、阈值检测器、伺服系统、智能传感器、生命辅助医疗设备、电源管理系统以及其它需要高精度的各种系统[1,3]。

由于集成电路技术无法直接产生参考电流或电压,实现温度无关量的唯一实用方法是结合两种具有相反温度依赖性的现象。首个带隙基准电压由维德拉在1971[2, 4]中提出,其中利用了两个独立物理参数的加权和:在不同电流密度下的基极到发射极电压之差具有与绝对温度成正比(PTAT)特性,而基极到发射极电压则具有与绝对温度互补的特性。(与绝对温度成比例的电压(CTAT))提供具有零温度系数的参考电压。通过两种电压量之间的相互补偿实现该效果,使得

$$

V_{ref} = m_1V_{CTAT} + m_2V_{PTAT}

$$

其中 $m_1$ 和 $m_2$ 是缩放因子,我们电路的行为可以列举为,

$$

\frac{\partial V_{ref}}{\partial T} = m_1 \frac{\partial V_{CTAT}}{\partial T} + m_2 \frac{\partial V_{PTAT}}{\partial T} = 0

$$

这些电路的性能通过其参考电压在温度、电源和其他工艺参数变化下的精确性来衡量,这些设计是通过结合基极‐发射极电压(CTAT)和热电压(PTAT)等参数实现的。由于基极‐发射极电压[1]存在非线性依赖,其性能受到限制。为了在较宽的温度范围内提高性能,已发展出多种技术,专注于消除由基极到发射极电压引起的非线性。但大多数技术通过使用大量元件导致设计非常复杂,进一步恶化了电路的其他参数。

在许多论文中,参考电路使用电阻或低压晶体管等特殊器件实现。使用这些特殊器件会增加芯片的制造工艺复杂性,从而提高制造成本。在电路中使用电阻[9]会引入芯片面积与功耗之间的权衡困境。不同的电压基准采用不同的原理来提取与绝对温度成比例的电压(CTAT)和与绝对温度成正比的电压(PTAT),例如基于阈值电压之差;这可以依赖于选择性沟道注入、由不同栅极材料获得的平带电压之差,或由不同栅极掺杂获得的功函数差。这些技术无法在标准CMOS技术中实现,因为它们需要额外的制造步骤。

本文提出了一种无电阻电压基准电路的简单设计,通过引入一种新的自偏置CTAT电路,利用MOSFET的栅源电压补偿双极型晶体管的结电压,从而实现了改进的温度系数和调整线。

在第二节中讨论了所提出的电路,第三节包含了所有仿真结果,第四节对工作进行了总结。

II. 提出的工作

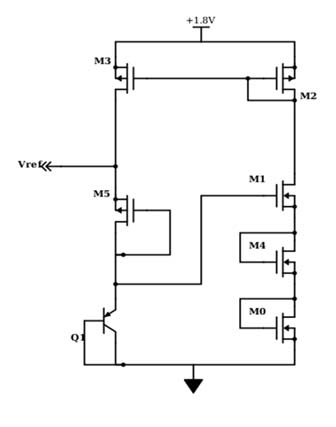

所提出的电路如图1所示。它包含PMOS M2和M3,构成一个电流镜,为二极管连接的PMOS M5提供偏置电流,PMOS M5作为电阻使用,其电阻随温度变化。所提出电路中所有晶体管的尺寸在表I中给出。

CTAT的产生

在此电路中,双极型晶体管的结电压$V_{BE}$由N个并联的nMOSFETs的栅源电压$V_{GS}$进行补偿。因此,栅源电压控制流过双极型晶体管的偏置电流。随着温度变化,结电压的非线性行为得到降低[4]。

假设所有MOSFET具有相同的长度L、宽度W和相同的斜率因子。结电压可表示为,

$$

V_{BE} = \left(\frac{m_1\phi - n_t}{1}\right)\left[\ln\left(2K\frac{W}{L}\frac{I_S}{I_Q}\right) - \frac{V_{T0}}{T}\right]

$$

由于三个nMOSFET堆叠,我们可以写出

$$

V_{BE} = 3V_{GS}

$$

并且,

$$

V_{GS,sub} = V_{GS,sub}(T_r) - \beta_{gs,sub}(T - T_r)

$$

其中$T_r$是参考温度,$\beta_{gs,sub}$是工作在亚阈值区的MOSFET的温度系数。$V_{GS}$随温度的变化比$V_{BE}$更线性。通过这种方式提取出CTAT参数。

B. PTAT的产生

双极结型晶体管的发射极电流$I_E$可以表示为,

$$

I_E = I_{SE} e^{\left(\frac{V_{BE}}{m\varphi_t}\right)}

$$

其中$V_{BE}$是双极型晶体管的发射极到基极电压,$I_{SE}$是p‐n结的反向饱和电流,$\varphi_t$是热电势,m是斜率因子。

如果电路中使用的每个MOSFET都在亚阈值区工作,则漏极电流$I_D$可以表示为[5],

$$

I_D = 2 I_{SQ} \frac{W}{L} exp\left(\frac{V_G - V_{T0}}{n\varphi_t} - \frac{V_S}{\varphi_t}\right)

$$

其中 $I_{SQ}$ 是单位面积特定电流,$V_{T0}$是零体源电压下的阈值电压, VG为栅极,Vs是相对于衬底的源极电压。

由电流镜产生的亚阈值电流对$V_{GS}$呈现指数依赖性,如公式7所示,可用于提取与绝对温度成正比项$V_T$。

where, $V_T = \frac{KT}{q}$

与绝对温度成正比的电流可通过一个作为电阻工作的二极管连接的PMOS来产生与绝对温度成正比的电压。工作在饱和区的PMOS两端的电阻可表示为,

$$

R_{ds} = \frac{1}{\beta(V_{SG} - V_{TH})}

$$

| 晶体管 | 尺寸(ࣆm) |

|---|---|

| M5 | W=0.42 L= 9.85 |

| M0, M1, M4 | W=1.6 L= 4 |

| M3,M2 | W=2 L= 4 |

| ## 表I. 所提出电路的晶体管尺寸 |

| 晶体管 | 尺寸(ࣆm) |

|---|---|

| M5 | W=0.42 L= 9.85 |

| M0, M1, M4 | W=1.6 L= 4 |

| M3, M2 | W=2 L= 4 |

带隙参考电压$V_{ref}$通过将与温度成反比的电压 $V_{BE}$和在 PMOS M5上获得的与温度成正比的电压相结合而得到,该电压近似等于硅的带隙电压(1.2V)。

III. 仿真结果

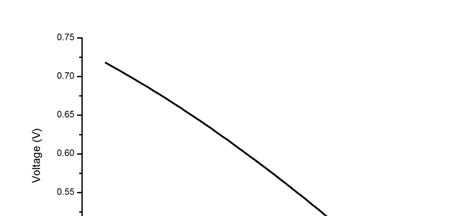

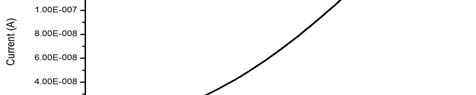

所提出的带隙基准电路采用标准的0.18ߤm CMOS技术实现。电流镜比例因子k取值为26,以正确缩放电流系数,并使用了N=3级联nMOS。在这些条件下,获得的与绝对温度成反比的电压为720mV,与绝对温度成正比的电流为140nA,如图2和图3所示。

如图4和图5所示,输出电压在‐45至125Ԩ的温度范围内进行绘制,其中我们获得的参考电压为1.15V,温度系数为11ppm/Ԩ ,当电源电压从1V变化到1.8V时,调整线为20%/V。

IV. 结论

本文提出了一种无电阻带隙基准电压电路。所提出的电路采用一种简单的方法来获取与绝对温度成正比(PTAT)和与绝对温度成反比的电压(CTAT电压)。根据仿真结果和表二可知,与先前实现的电压基准相比,所提出的设计在改进的温度系数和宽范围的电源和温度变化下的调整线方面表现出更具竞争力的结果,同时功耗更低、面积更小(因为无需使用电阻)。所提出电路的优异性能使其适用于低压差稳压器、高分辨率模数转换器及其他器件。

表二。提出的工作带隙基准电路的比较

| 规格 | 提出的工作 | [6] | [8] | [7] |

|---|---|---|---|---|

| 电源电压(伏特) | 1.8 | 0.45‐2 | 0.15‐1.8 | 1.2‐2.2 |

| 参考电压(伏特) | 1.15 | 0.263 | 0.017 | 0.986 |

| 温度范围(Ԩ) | ‐45‐125 | 0‐120 | 0‐120 | ‐40‐85 |

| 温度系数(ppm/Ԩ) | 11 | 142 | 1462 | 124 |

| 调节线性度(%/V) | 20 | 0.44 | 2.03 | 0.38 |

| 技术 | CMOS 0.18ߤm | CMOS 0.18ߤm | CMOS 0.18ߤm | CMOS 0.18ߤm |

469

469

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?