一、cache的基本概念和结构

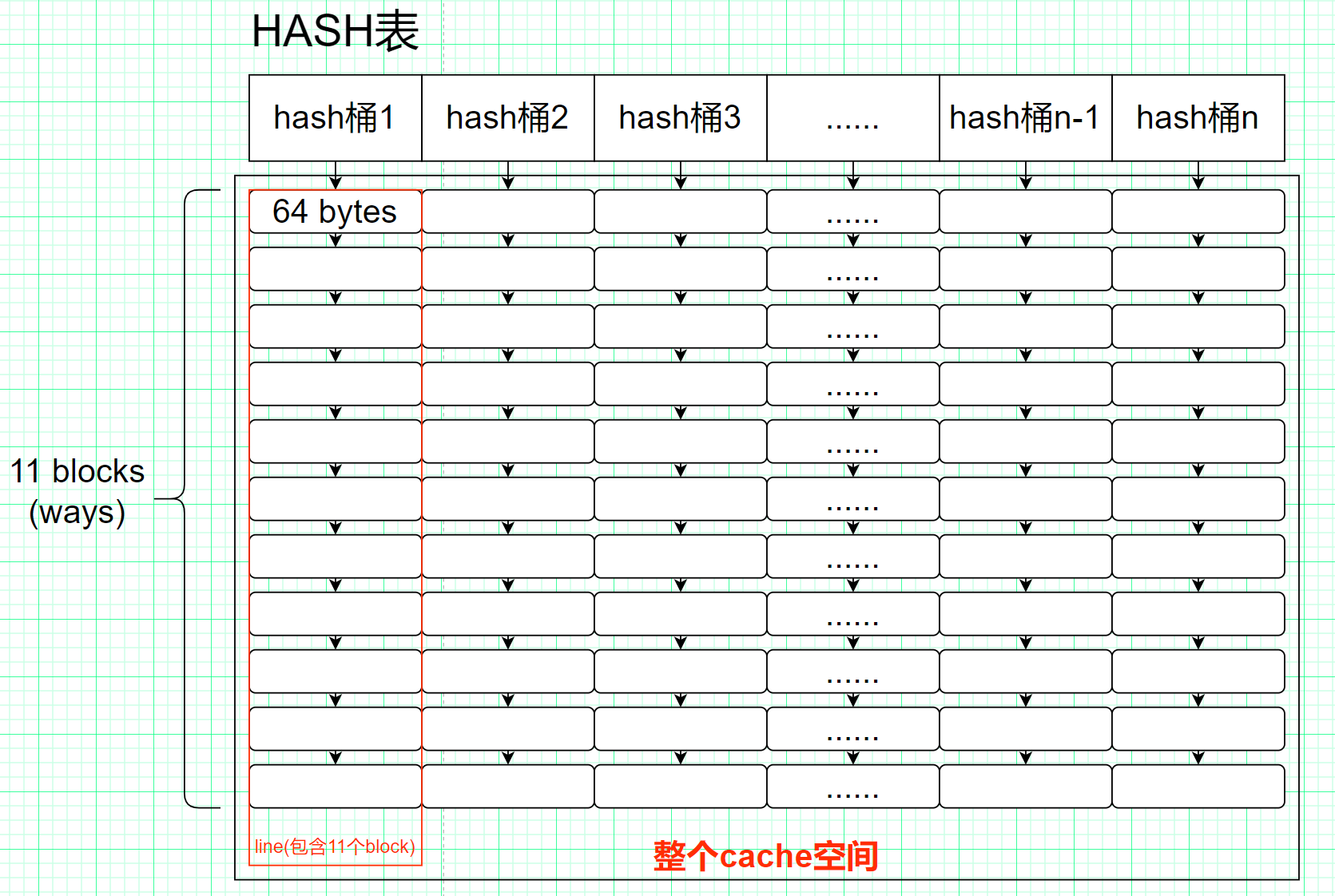

cache本质就是一个硬件hash表+SRAM。

cache本质就是一个硬件hash表+SRAM。

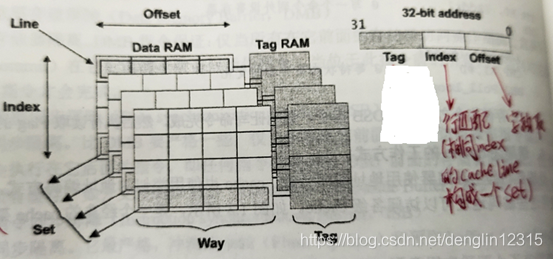

从上面的cache结构图可以解答如下疑问:

- cache有哪些属性?

- cache如何寻址?

- cache的一般结构是什么样子?

下面分点作答:

1. cache有哪些属性?

line:代表一个cacheline,cache中最小访问单元,常见的cache line大小是32/64 Byte

set(组):相同index的cache line组成的一个组。

way(路):在组相联的cache中,cache被分成大小相同的几个快,一个cache块就是一个way。

2. cache如何寻址?

处理器访问cache时,cache电路会将CPU地址进行解码,分成3个部分,分别是:

offset: 用于某个cache line——字抽取

index: 用于匹配某个cache line——组选择

tag: 用于判断匹配到的cache line存放的数据是否和处理器想要的一致——行匹配

3.cache的一般结构是什么样子?

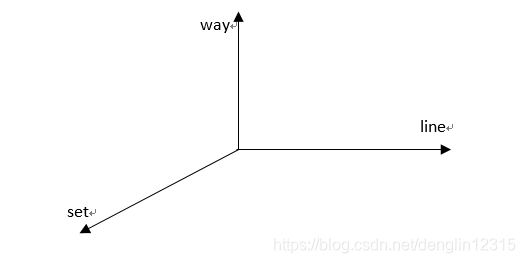

这里展示一个便于理解的抽象结构,而非实际物理结构(实际物理结构就是一块SRAM硅片,并不是上图的立体结构),再进一步,为了方便理解上图,抽象出如下三维坐标系:

将这个三维坐标和上图的cache立体结构对应起来,可以看出以下cache属性的关系:

way: 对应坐标系中一个(set,line)平面

set: 对应坐标系中一个(line,way)平面

index:用于匹配cache line所在的set(组)

二、cache的类型

直接映射高速缓存(一个路,多个组,每个组包含一个cache line)——缺点是多个组索引(Index)指向相同的cacheline,容易导致cache颠簸

组相联高速缓存(多个路,多个组,每个组包含多个cache line)——各缺点介于二者之间

全相联高速缓存(一个组,多个路,这个组包含cache的所有cache line)——缺点是要维护更庞大的cache查找表(Tag字段)

三、Data cache的组织方式以及各种的优缺点

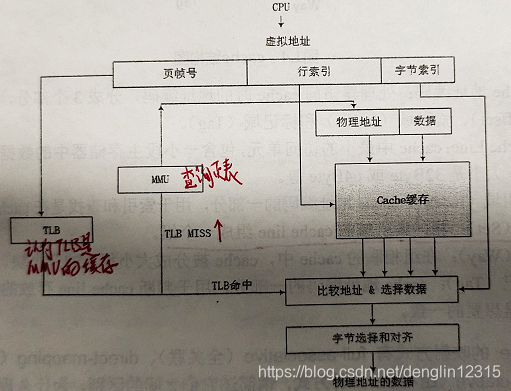

处理器在进行存储器访问时,处理器访问的地址是虚拟地址,经过MMU的转换,得到物理地址。那么查询cache组是用虚拟地址还是物理地址的Index域呢?当找到cache组时,使用虚拟地址,还是物理地址的Tag域来匹配cache line呢?

VIVT(Virtual Index Virtual Tag):使用虚拟地址Index域和虚拟地址Tag域

VIPT(Virtual Index Physical Tag):使用虚拟地址Index域和物理地址Tag域

PIPT(Physical Index Physical Tag):使用物理地址Index域和物理地址Tag域

说明:这里的V/P其实就是指上图中address中的Tag/Index/Line来自V(虚拟地址)还是P(物理地址)

下面以VIPT方式cache工作流程举例说明:

情形一:TLB hit并且cache hit

- CPU发出VA,给TLB/MMU和cache

- cache用VA的Index域匹配cache line组

- 用VA查找TLB,如果TLB hit,直接获取VA对应的PA

- 用PA中的tag域匹配cache line

- 如果cache hit,执行cache line字抽取动作

情形二:TLB hit并且cache miss

- CPU发出VA,给TLB/MMU和cache

- cache用VA的Index域匹配cache line组

- 用VA查找TLB,如果TLB hit,直接获取VA对应的PA

- 用PA中的tag域匹配cache line

- 如果cache miss,那么用获取到的PA访问系统主存,获取数据,并更新缓存

情形三:TLB miss并且cache hit

- CPU发出VA,给TLB/MMU和cache

- cache用VA的Index域匹配cache line组

- 用VA查找TLB,如果TLB miss,CPU重新查询页表,通过MMU将VA映射到PA,并更新TLB

- 用PA中的tag域匹配cache line

- 如果cache hit,执行cache line字抽取动作

情形四:TLB miss并且cache miss

- CPU发出VA,给TLB/MMU和cache

- cache用VA的Index域匹配cache line组

- 用VA查找TLB,如果TLB miss,CPU重新查询页表,通过MMU将VA映射到PA,并更新TLB

- 用PA中的tag域匹配cache line

- 如果cache miss,那么用获取到的PA访问系统主存,获取数据,并更新缓存

VIVT/VIPT/PIPT的优缺点分析:

VIVT:多个VA可能映射到同一PA,导致多个cache line组(VA不同,index域不同,查找到的cache 组则不同)映射到同一物理地址,这种现象叫做cache alias(高速缓存别名)。一旦一个VA到PA的映射关系改变,cache内容将会写回物理内存。此时,由于物理内存内容的变化需要同步到cache,就需要clean和invalidate(这两个操作结合起来就叫做flush)其余同名cache line,导致系统性能下降。

VIPT:如果index域位于地址的bit0~bit11(因为linux kernel以4KB(12bit位宽)大小为页面进行物理内存管理),就不会引起cache alias,否则还是会引起该问题。因为对于一个页面来说,虚拟地址和物理地址的低12bit是完全一样的,如果index域位于bit0~bit11,此时VIPT等价于PIPT。

PIPT:就不会存在cache alias问题,但是结构更复杂。ARM Cortex-A系列处理器使用的是PIPT方式。

3431

3431

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?