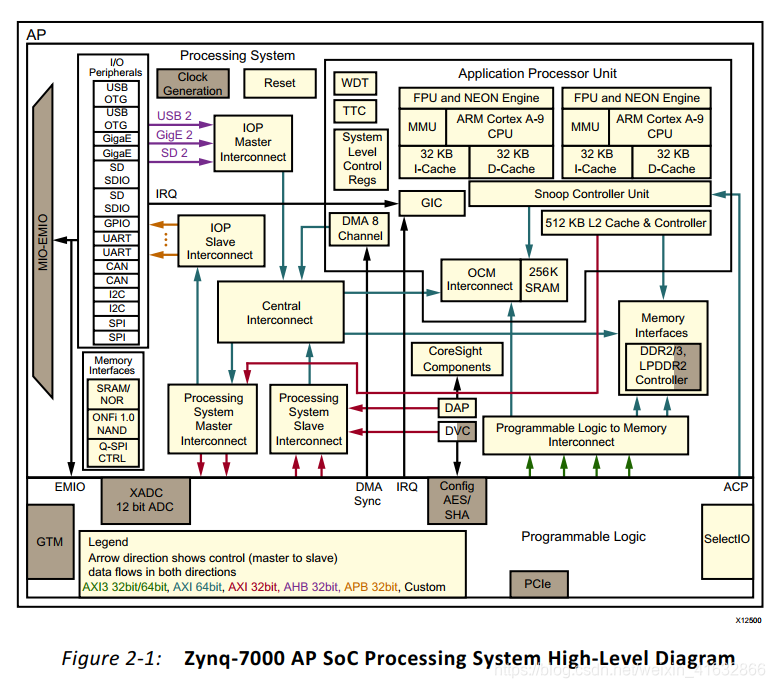

zynq 7000系列作为xilinx公司最具性价比的SOC系列,在消费市场大受欢迎。其内部配置一个或两个ARM架构的cortex A9核,对于管理调度有重大意义,同时在ARM侧(专业叫法为PS侧)配置了uart,iic,ethernet,flash,ddr等多个接口,不再需要FPGA侧(PL侧)针对这些接口再做控制器,使用起来更加方便,当然效率肯定不如纯FPGA来的高。

这篇文章只是分析一下PS侧的ARM架构,也是记录我自己学习的过程,完成从FPGA到嵌入式的转变。

1.Cache

cache可能被分为L1, L2, L3, 越往外,访问时间也就越长,但同时也就越便宜。L1 cache命中时,访问时间为1~2个CPU周期;

L1 cache不命中,L2 cache命中,访问时间为5~10个CPU周期。

当要去内存中取单元时,访问时间可能就到25~100个CPU周期了。

所以,我们总是希望cache的命中率尽可能的高。

关于Cache的原理,可参见:https://blog.youkuaiyun.com/orange_os/article/details/7853355

该博文中一个非常有用的例子,记录了什么样的操作更利于Cache的操作(该例子是在单核运行时;如果是多核运行,只要不同的线程或者进程访问同一cacheline的不同内容,就会发生“伪共享问题”。这样的问题较为隐蔽,难以发现。)。

Cache友好的代码:

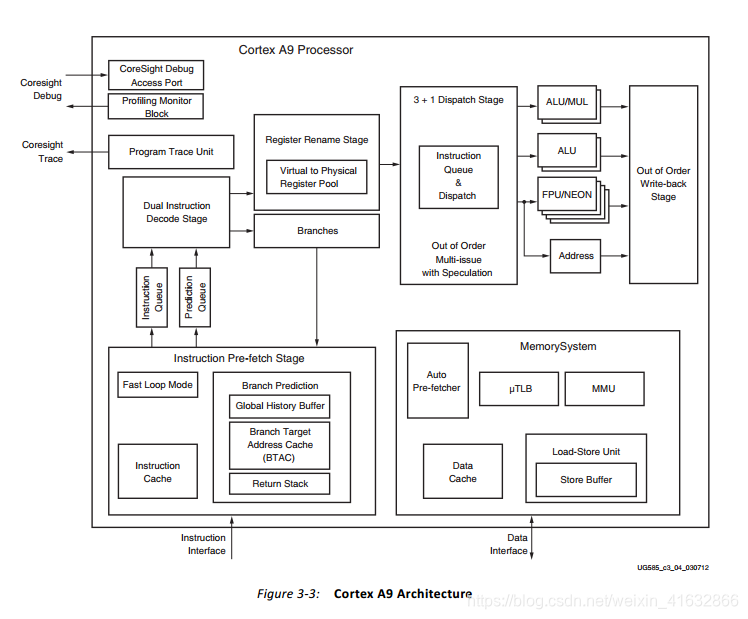

本文介绍了ZYNQ 7000系列中的ARM Cortex A9核,重点分析了L1和L2 Cache的结构与工作模式,特别是Cache的命中率对性能的影响。此外,还探讨了Branch Prediction在提升处理器效率中的作用,以及ZYNQ中ARM架构的具体实现。

本文介绍了ZYNQ 7000系列中的ARM Cortex A9核,重点分析了L1和L2 Cache的结构与工作模式,特别是Cache的命中率对性能的影响。此外,还探讨了Branch Prediction在提升处理器效率中的作用,以及ZYNQ中ARM架构的具体实现。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1836

1836

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?