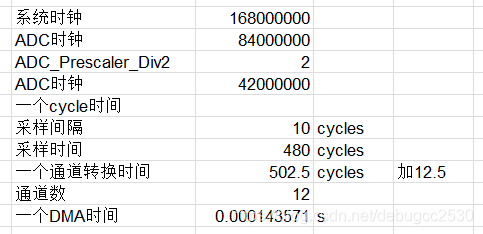

系统时钟 168M

ADC时钟 84M(根据下列PCLK2时钟)

/* PCLK2 = HCLK / 2*/

RCC->CFGR |= RCC_CFGR_PPRE2_DIV2;

ADC分频:2

ADC_CommonInitStructure.ADC_Prescaler = ADC_Prescaler_Div2;

ADC时钟:42M

采样间隔:10 cycles

ADC_CommonInitStructure.ADC_TwoSamplingDelay = ADC_TwoSamplingDelay_10Cycles;

采样时间:480 cycles

ADC_RegularChannelConfig(ADC1, ADC_Channel_0, 1, ADC_SampleTime_480Cycles);

采样通道数:12

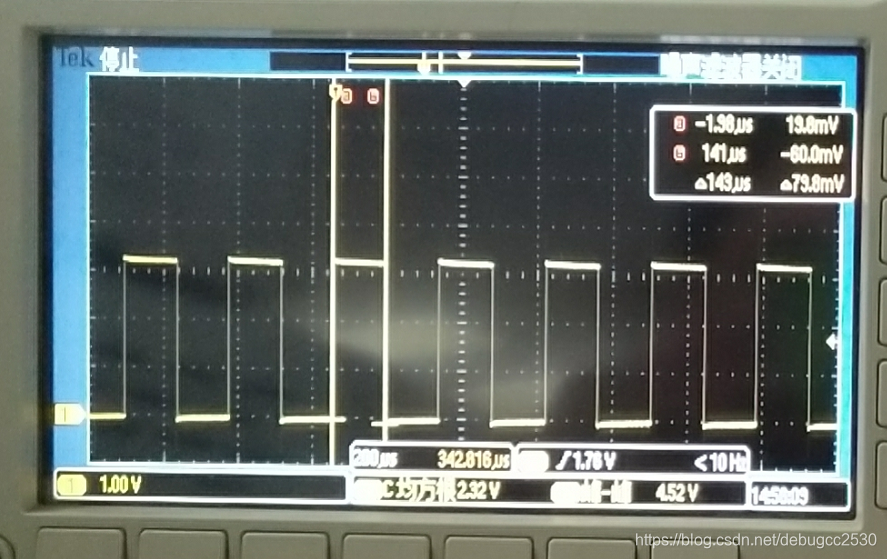

采样时间=(10+480+12.5)*12/42M = 143.57us

DMA中断周期:

本文详细介绍了STM32中ADC模块的配置过程,包括系统时钟设置为168MHz,通过寄存器配置使PCLK2为HCLK的一半即84MHz,并进一步将ADC时钟设置为42MHz。文章还深入解析了ADC采样时间的计算方法,包括采样间隔和总采样时间等关键参数。

本文详细介绍了STM32中ADC模块的配置过程,包括系统时钟设置为168MHz,通过寄存器配置使PCLK2为HCLK的一半即84MHz,并进一步将ADC时钟设置为42MHz。文章还深入解析了ADC采样时间的计算方法,包括采样间隔和总采样时间等关键参数。

1万+

1万+