module hutao(

input clk ,

output wire[15:0]out_RBG ,

output reg out_HSync,//行信号

output reg out_VSync//场信号

);

parameter RBG_white = 16'hFFFF; //白色

wire clk_25MHz ;

wire rst_n ;

reg [15:0] data_HS;

reg [15:0] data_VS;

reg [15:0] data_1;

reg [15:0] data;

always @ (posedge clk_25MHz or negedge rst_n)

begin if (~rst_n)

data_HS<=16'd0;

else if(data_HS==16'd799)

data_HS<=16'd0;

else

data_HS<=data_HS+1'd1;

end

always @ (posedge clk_25MHz or negedge rst_n)

begin if (~rst_n)

data_VS<=16'd0;

else if(data_HS==16'd799)

data_VS<=data_VS+1'd1;

else if(data_VS==16'd525)

data_VS<=16'd0;

else

data_VS<=data_VS;

end

always @ (posedge clk_25MHz or negedge rst_n)

begin if (~rst_n)

data_1<=16'd0;

else if(data_1==16'd10&&data_VS==16'd525)

data_1<=16'd0;

else if(data_VS==16'd525)

data_1<=data_1+1'd1;

else

data_1<=data_1;

end

always @ (posedge clk_25MHz or negedge rst_n)

begin if (~rst_n)

data<=16'd0;

else if(data==16'd0&&data_1==16'd10&&data_VS==16'd525)

data<=16'd0;

else if(data_1==16'd10&&data_VS==16'd525)

data<=data+1'd1;

else

data<=data;

end

always @ (posedge clk_25MHz or negedge rst_n)

begin if (~rst_n)

out_HSync<=1'd0;

else if(data_HS<16'd96)

out_HSync<=1'd1;

else

out_HSync<=1'd0;

end

always @ (posedge clk_25MHz or negedge rst_n)

begin if (~rst_n)

out_VSync<=1'd0;

else if(data_VS<16'd2)

out_VSync<=1'd1;

else

out_VSync<=1'd0;

end

reg [31:0]co_x;

reg [31:0]co_y;

always @ (posedge clk_25MHz or negedge rst_n)

begin if (~rst_n)begin

co_x<=1'd0;

co_y<=1'd0;

end

else begin

co_x<=data_HS-16'd143;

co_y<=data_VS-16'd34;

end

end

wire display;

reg rden_sig ;

// reg rden_sig1 ;

// reg rden_sig2 ;

// reg rden_sig3 ;

// reg rden_sig4 ;

// reg rden_sig5 ;

// reg rden_sig6 ;

// reg rden_sig7 ;

// reg rden_sig8 ;

// reg rden_sig9 ;

// reg rden_sig10;

// reg rden_sig11;

// reg rden_sig12;

// reg rden_sig13;

// reg rden_sig14;

// reg rden_sig15;

// reg rden_sig16;

// reg rden_sig17;

// reg rden_sig18;

// reg rden_sig19;

// reg rden_sig20;

// reg rden_sig21;

// reg rden_sig22;

// reg rden_sig23;

// reg rden_sig24;

// reg rden_sig25;

// reg rden_sig26;

// reg rden_sig27;

// reg rden_sig28;

// reg rden_sig29;

// reg rden_sig30;

wire [15:0]q1;

wire [15:0]q2;

wire [15:0]q3;

wire [15:0]q4;

wire [15:0]q5;

wire [15:0]q6;

wire [15:0]q7;

wire [15:0]q8;

wire [15:0]q9;

wire [15:0]q10;

wire [15:0]q11;

wire [15:0]q12;

wire [15:0]q13;

wire [15:0]q14;

wire [15:0]q15;

wire [15:0]q16;

wire [15:0]q17;

wire [15:0]q18;

wire [15:0]q19;

wire [15:0]q20;

wire [15:0]q21;

wire [15:0]q22;

wire [15:0]q23;

wire [15:0]q24;

wire [15:0]q25;

wire [15:0]q26;

wire [15:0]q27;

wire [15:0]q28;

wire [15:0]q29;

wire [15:0]q30;

reg [15:0]address_sig;

//assign display=((data_HS>=16'd143&&data_HS<16'd783)&&(data_VS>=16'd34&&data_VS<16'd514))?1'd1:1'd0;//显示标志

/* // ====== 修改部分:添加 prev_co_y 检测行变化 ======

reg [31:0] prev_co_y;

always @ (posedge clk_25MHz or negedge rst_n) begin

if (~rst_n)

prev_co_y <= 0;

else

prev_co_y <= co_y;

end

// ====== 替换原来的 rden_sig 和 address_sig 逻辑 ======

always @ (posedge clk_25MHz or negedge rst_n)

begin

if (~rst_n) begin

rden_sig <= 1'd0;

address_sig <= 16'd0;

end else if (display) begin

// 检查当前点是否在图像区域内

if (co_x >= 32'd270 && co_x < 32'd293 &&

co_y >= 32'd290 && co_y < 32'd312) begin

// 进入图像区域

rden_sig <= 1'd1;

// 如果是本行第一个像素 (x==270),则初始化 base 地址

if (co_x == 32'd270) begin

address_sig <= (co_y - 32'd290) * 16'd23; // 起始地址:行号 × 宽度

end else begin

address_sig <= address_sig + 1'd1; // 其他像素依次 +1

end

end else begin

rden_sig <= 1'd0;

address_sig <= 16'd0;

end

end else if (data_VS == 16'd525) begin // 帧结束时复位

rden_sig <= 1'd0;

address_sig <= 16'd0;

end else begin

rden_sig <= 1'd0;

address_sig <= address_sig;

end

end */

// ===== 第一步:添加参数 =====

parameter SCALE = 10;

// ===== 第二步:修改 display 判断区域 =====

localparam IMG_LEFT = 270;

localparam IMG_TOP = 290;

localparam IMG_WIDTH = 23 * SCALE; // 230

localparam IMG_HEIGHT = 22 * SCALE; // 220

assign display = ((data_HS >= IMG_LEFT && data_HS < IMG_LEFT + IMG_WIDTH) &&

(data_VS >= IMG_TOP && data_VS < IMG_TOP + IMG_HEIGHT)) ? 1'd1 : 1'd0;

// ===== 第三步:增加坐标映射 =====

wire [4:0] img_x;

wire [4:0] img_y;

wire [31:0] offset_x = co_x - IMG_LEFT;

wire [31:0] offset_y = co_y - IMG_TOP;

assign img_x = offset_x / SCALE;

assign img_y = offset_y / SCALE;

// ===== 第四步:替换 address_sig 和 rden_sig 逻辑 =====

always @ (posedge clk_25MHz or negedge rst_n)

begin

if (~rst_n) begin

rden_sig <= 1'd0;

address_sig <= 16'd0;

end else if (display) begin

rden_sig <= 1'd1;

address_sig <= (img_y * 23) + img_x; // 核心:定位原始像素

end else begin

rden_sig <= 1'd0;

address_sig <= 16'd0;

end

end

wire [15:0]q;

// always @ (posedge clk_25MHz or negedge rst_n)

// begin if (~rst_n)begin

// rden_sig1 <=1'd0;

// rden_sig2 <=1'd0;

// rden_sig3 <=1'd0;

// rden_sig4 <=1'd0;

// rden_sig5 <=1'd0;

// rden_sig6 <=1'd0;

// rden_sig7 <=1'd0;

// rden_sig8 <=1'd0;

// rden_sig9 <=1'd0;

// rden_sig10<=1'd0;

// rden_sig11<=1'd0;

// rden_sig12<=1'd0;

// rden_sig13<=1'd0;

// rden_sig14<=1'd0;

// rden_sig15<=1'd0;

// rden_sig16<=1'd0;

// rden_sig17<=1'd0;

// rden_sig18<=1'd0;

// rden_sig19<=1'd0;

// rden_sig20<=1'd0;

// rden_sig21<=1'd0;

// rden_sig22<=1'd0;

// rden_sig23<=1'd0;

// rden_sig24<=1'd0;

// rden_sig25<=1'd0;

// rden_sig26<=1'd0;

// rden_sig27<=1'd0;

// rden_sig28<=1'd0;

// rden_sig29<=1'd0;

// rden_sig30<=1'd0;

// end

// else

// begin

// case(data)

// 16'd0 :rden_sig1 <=rden_sig;

// 16'd1 :rden_sig2 <=rden_sig;

// 16'd2 :rden_sig3 <=rden_sig;

// 16'd3 :rden_sig4 <=rden_sig;

// 16'd4 :rden_sig5 <=rden_sig;

// 16'd5 :rden_sig6 <=rden_sig;

// 16'd6 :rden_sig7 <=rden_sig;

// 16'd7 :rden_sig8 <=rden_sig;

// 16'd8 :rden_sig9 <=rden_sig;

// 16'd9 :rden_sig10<=rden_sig;

// 16'd10 :rden_sig11<=rden_sig;

// 16'd11 :rden_sig12<=rden_sig;

// 16'd12 :rden_sig13<=rden_sig;

// 16'd13 :rden_sig14<=rden_sig;

// 16'd14 :rden_sig15<=rden_sig;

// 16'd15 :rden_sig16<=rden_sig;

// 16'd16 :rden_sig17<=rden_sig;

// 16'd17 :rden_sig18<=rden_sig;

// 16'd18 :rden_sig19<=rden_sig;

// 16'd19 :rden_sig20<=rden_sig;

// 16'd20 :rden_sig21<=rden_sig;

// 16'd21 :rden_sig22<=rden_sig;

// 16'd22 :rden_sig23<=rden_sig;

// 16'd23 :rden_sig24<=rden_sig;

// 16'd24 :rden_sig25<=rden_sig;

// 16'd25 :rden_sig26<=rden_sig;

// 16'd26 :rden_sig27<=rden_sig;

// 16'd27 :rden_sig28<=rden_sig;

// 16'd28 :rden_sig29<=rden_sig;

// 16'd29 :rden_sig30<=rden_sig;

// endcase

// end

// end

assign out_RBG=(~display)?1'd0:

(rden_sig==1'd1)?q:RBG_white;

assign q= (data==16'd0 )?q1 :

(data==16'd1 )?q2 :

(data==16'd2 )?q3 :

(data==16'd3 )?q4 :

(data==16'd4 )?q5 :

(data==16'd5 )?q6 :

(data==16'd6 )?q7 :

(data==16'd7 )?q8 :

(data==16'd8 )?q9 :

(data==16'd9 )?q10:

(data==16'd10)?q11:

(data==16'd11)?q12:

(data==16'd12)?q13:

(data==16'd13)?q14:

(data==16'd14)?q15:

(data==16'd15)?q16:

(data==16'd16)?q17:

(data==16'd17)?q18:

(data==16'd18)?q19:

(data==16'd19)?q20:

(data==16'd20)?q21:

(data==16'd21)?q22:

(data==16'd22)?q23:

(data==16'd23)?q24:

(data==16'd24)?q25:

(data==16'd25)?q26:

(data==16'd26)?q27:

(data==16'd27)?q28:

(data==16'd28)?q29:

(data==16'd29)?q30:white;

pll_25MHz pll_25MHz_inst (

.inclk0 ( clk ),

.c0 ( clk_25MHz ),

.locked ( rst_n )

);

rom1 rom1_inst (

.address ( address_sig),

.clock ( clk ),

.rden ( rden_sig),

.q ( q1)

);

rom2 rom2_inst (

.address ( address_sig),

.clock ( clk ),

.rden ( rden_sig),

.q ( q2)

);

rom3 rom3_inst (

.address ( address_sig),

.clock ( clk ),

.rden ( rden_sig),

.q ( q3)

);

rom4 rom4_inst (

.address ( address_sig),

.clock ( clk ),

.rden ( rden_sig),

.q ( q4)

);

rom5 rom5_inst (

.address ( address_sig),

.clock ( clk ),

.rden ( rden_sig),

.q ( q5)

);

rom6 rom6_inst (

.address ( address_sig),

.clock ( clk ),

.rden ( rden_sig),

.q ( q6)

);

rom7 rom7_inst (

.address ( address_sig),

.clock ( clk ),

.rden ( rden_sig),

.q ( q7)

);

rom8 rom8_inst (

.address ( address_sig),

.clock ( clk ),

.rden ( rden_sig),

.q ( q8)

);

rom9 rom9_inst (

.address ( address_sig),

.clock ( clk ),

.rden ( rden_sig),

.q ( q9)

);

rom10 rom10_inst (

.address ( address_sig),

.clock ( clk ),

.rden ( rden_sig),

.q ( q10)

);

rom11 rom11_inst (

.address ( address_sig),

.clock ( clk ),

.rden ( rden_sig),

.q ( q11)

);

rom12 rom12_inst (

.address ( address_sig),

.clock ( clk ),

.rden ( rden_sig),

.q ( q12)

);

rom13 rom13_inst (

.address ( address_sig),

.clock ( clk ),

.rden ( rden_sig),

.q ( q13)

);

rom14 rom14_inst (

.address ( address_sig),

.clock ( clk ),

.rden ( rden_sig),

.q ( q14)

);

rom15 rom15_inst (

.address ( address_sig),

.clock ( clk ),

.rden ( rden_sig),

.q ( q15)

);

rom16 rom16_inst (

.address ( address_sig),

.clock ( clk ),

.rden ( rden_sig),

.q ( q16)

);

rom17 rom17_inst (

.address ( address_sig),

.clock ( clk ),

.rden ( rden_sig),

.q ( q17)

);

rom18 rom18_inst (

.address ( address_sig),

.clock ( clk ),

.rden ( rden_sig),

.q ( q18)

);

rom19 rom19_inst (

.address ( address_sig),

.clock ( clk ),

.rden ( rden_sig),

.q ( q19)

);

rom20 rom20_inst (

.address ( address_sig),

.clock ( clk ),

.rden ( rden_sig),

.q ( q20)

);

rom21 rom21_inst (

.address ( address_sig),

.clock ( clk ),

.rden ( rden_sig),

.q ( q21)

);

rom22 rom22_inst (

.address ( address_sig),

.clock ( clk ),

.rden ( rden_sig),

.q ( q22)

);

rom23 rom23_inst (

.address ( address_sig),

.clock ( clk ),

.rden ( rden_sig),

.q ( q23)

);

rom24 rom24_inst (

.address ( address_sig),

.clock ( clk ),

.rden ( rden_sig),

.q ( q24)

);

rom25 rom25_inst (

.address ( address_sig),

.clock ( clk ),

.rden ( rden_sig),

.q ( q25)

);

rom26 rom26_inst (

.address ( address_sig),

.clock ( clk ),

.rden ( rden_sig),

.q ( q26)

);

rom27 rom27_inst (

.address ( address_sig),

.clock ( clk ),

.rden ( rden_sig),

.q ( q27)

);

rom28 rom28_inst (

.address ( address_sig),

.clock ( clk ),

.rden ( rden_sig),

.q ( q28)

);

rom29 rom29_inst (

.address ( address_sig),

.clock ( clk ),

.rden ( rden_sig),

.q ( q29)

);

rom30 rom30_inst (

.address ( address_sig),

.clock ( clk ),

.rden ( rden_sig),

.q ( q30)

);

endmodule哈哈哈哈这样可以吗]

最新发布

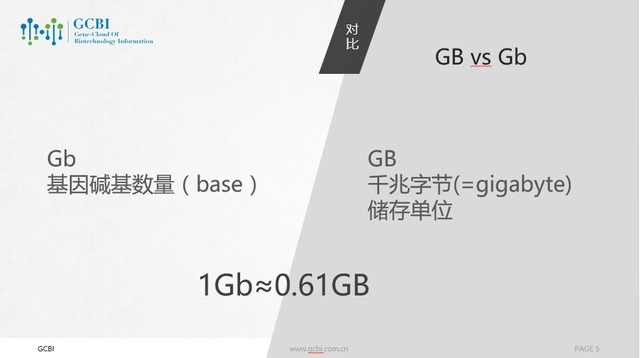

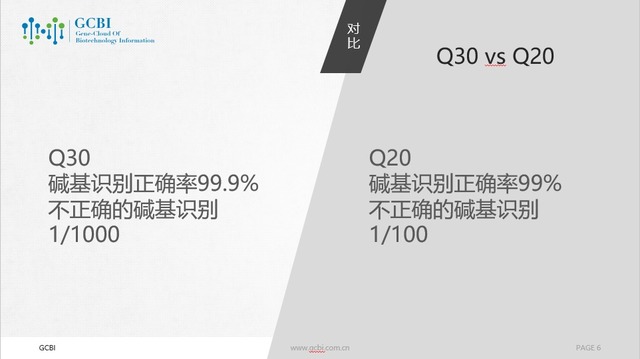

本文介绍了测序数据的不同阶段,包括原始数据、PF数据、Q30数据和干净数据。原始数据是未经处理的全部测序信息,PF数据通过质控筛选保留高质量片段,Q30数据则进一步确保碱基识别的99.9%可靠性,而干净数据是在PF数据基础上根据特定标准进行深度清理后的结果。

本文介绍了测序数据的不同阶段,包括原始数据、PF数据、Q30数据和干净数据。原始数据是未经处理的全部测序信息,PF数据通过质控筛选保留高质量片段,Q30数据则进一步确保碱基识别的99.9%可靠性,而干净数据是在PF数据基础上根据特定标准进行深度清理后的结果。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1326

1326

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?