用于时钟数据恢复应用的65纳米CMOS技术中低功耗宽调谐范围环形振荡器的双控制电压延迟单元的设计与分析

摘要

本文评估了用于四级环形振荡器的三种延迟单元结构。在第一种结构中,控制电压施加到与输入PMOS晶体管串联的PMOS晶体管的栅极,从而实现最低的功耗。当控制电压注入到与输入晶体管并联的PMOS晶体管时,可获得更高的频率调谐范围和更低的相位噪声。为了在调谐范围、相位噪声和功耗之间取得折衷,在改进的结构中,由控制电压驱动的PMOS晶体管被同时应用于串联和并联路径。在65纳米CMOS技术下,该振荡器在1伏特电源电压下的工作频率范围为2.65‐13.93吉赫兹。在3.7吉赫中心频率偏移1兆赫处的相位噪声为‐94.33分贝每赫兹,功耗为328.6瓦,芯片面积为139.5μm²。

关键词 :环形压控振荡器,宽调谐范围,低功耗,时钟与数据恢复

1. 引言

随着个人用途无线通信的发展,对低成本、低功耗和最小面积的无线系统的需求迅速增长[1]。在现代通信中,用于再放大、整形和重定时的时钟和数据恢复(CDR)起着关键作用[2]。为了在接收器中消除晶体振荡器,CDR被用来从输入数据中恢复时钟信息[3,4]。因此,设计高能效且更高速度的CDR具有挑战性[5,6]。基于锁相环的CDR的框图由压控振荡器(VCO)、相位检测器(PD)、电荷泵(CP)和环路滤波器组成。由于VCO在CDR中消耗主要功率,因此应精确设计。

LC‐VCO和环形VCO是可用于CDR的两种结构。LC‐VCO具有更好的相位噪声[7,8]和更高的工作频率。尽管如此,由于螺旋电感的存在,LC‐VCO的调谐范围较窄且芯片面积较大,这是其缺点。此外,LC‐VCO的制造需要额外的工艺步骤,导致成本更高。另一方面,全晶体管振荡器具有易于集成的特点,并且在芯片上占用的面积远小于使用LC谐振槽的振荡器[9,10]。因此,环形振荡器是CDR应用中的良好选择,因为它具有更宽的调谐范围和更小的芯片面积。选择振荡器的环形拓扑是因为其启动时间非常短,并避免了电感的使用,而在宽带信号生成中,高相位噪声的问题显然并不重要[11]。另一方面,由于易于集成并兼容数字CMOS工艺,环形振荡器近年来被广泛需求。

CMOS压控振荡器的各种配置可分为两种主要拓扑结构:采用单端和差分延迟单元的压控振荡器[9,12]。差分拓扑更适合高速串行接口,因为它们提供更好的共模和电源抑制性能[9]。有趣的是,已有多种技术被提出用于降低差分VCO的相位噪声和功耗。文献[7]中提出的前馈相位噪声抵消技术可改善环形振荡器的相位噪声,但会消耗较高的功率。文献[13]中提出的PMOS‐NMOS交叉耦合(PNC)噪声抵消技术是改善相位噪声的有效方法之一;然而,为了实现更好的噪声抵消,它需要更大的晶体管宽度。此外,在低工作频率下,晶体管的注入沟道热噪声在输出电压转换期间会被衰减[14]。粗/细频率调谐是另一种可用于降低VCO在低电源电压下噪声敏感性的方法,但它会导致更高的功耗[15]。文献[16]中提出的相位对齐环形振荡器可以在较低工作频率下显著改善相位噪声,但代价是占用更多面积和功耗。互补电流控制技术不仅能在较高振荡频率下改善相位噪声性能,还能扩展调谐范围,但同样以高功耗为代价[17]。文献[9]中提出的压控振荡器拓扑包含了所有必要的辅助电路,用于改善诸如输出电压摆幅、共模抑制比(CMRR)和占空比等基本性能。最重要的设计规格包括低功耗下的相位噪声表现以及在工艺、电压、温度角(PVT corners)下的性能容差。文献[18]中提出了一种宽带双频调谐环形压控振荡器,具有缩放功能,有助于确保锁相环(PLL)的稳定运行。尽管该方案具有一些优势,但它需要一个6位模数转换器来生成Vcoarse,这会消耗更多的功耗和芯片面积。

在本简报中,提出了三种不同的延迟单元结构并进行了分析。仿真结果表明,具有两个控制电压的所提出的延迟单元不仅改善了四级环形振荡器的功耗和相位噪声,还改善了其调谐范围。本文组织如下:第2节提出了三种不同的延迟单元,并详细说明了每个晶体管的作用;第3节给出了频率分析;第4节提供了仿真结果;最后,第5节对整个工作进行了总结。

2. 所提出的延迟单元的评估

环形振荡器的延迟单元可分为两类:单端和差分延迟单元[19]。使用单端延迟单元产生振荡信号时,所用反相器的数量应为奇数,而在差分环形振荡器中,则可以使用奇数或偶数级反相器。需要注意的是,较少的级数有助于降低功耗和芯片面积;因此通常采用两级、三级或四级的差分环形振荡器。两级或四级环形振荡器可产生正交输出,但如果速度是关键因素,三级环形振荡器的性能优于四级环形振荡器。在本研究中,为了在具有高工作频率和调谐范围的时钟数据恢复电路中应用,采用了具有双延迟路径方案的四级环形振荡器。

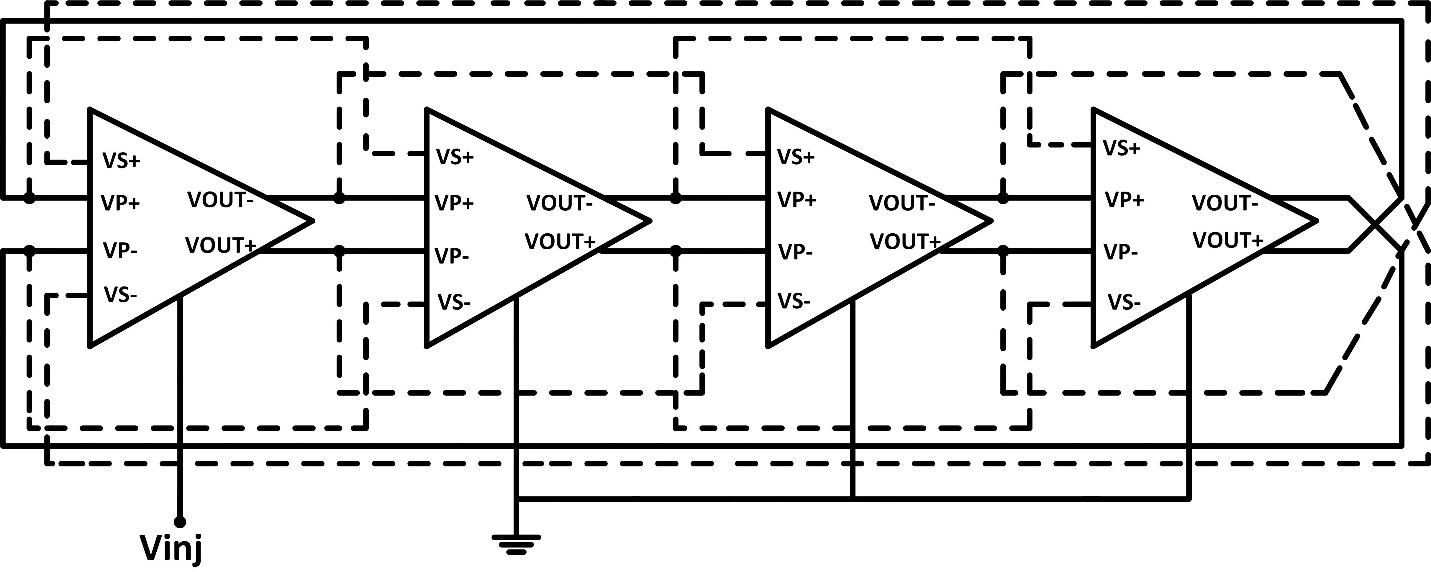

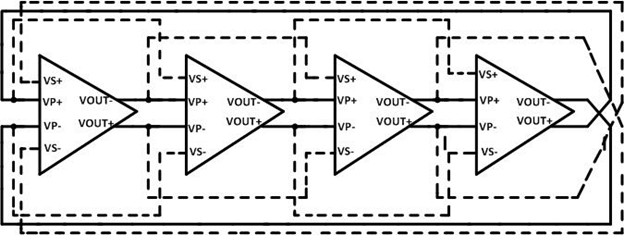

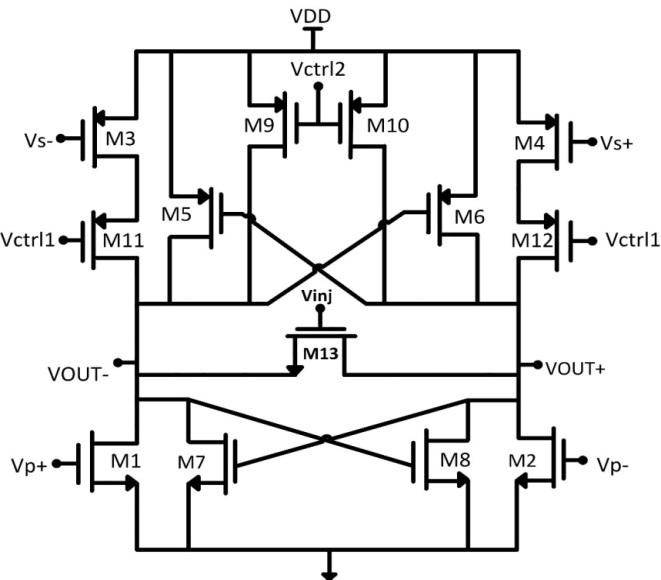

除了主输入外,双延迟环中还存在次级输入[19]。在这种情况下,次级输入比主输入更早切换。图1所示的四级双延迟环振荡器展示了延迟单元之间的连接方式[15]。为了区分主环和次级环路,分别使用实线和虚线表示。由实线表示的主环构成了普通的差分环形振荡器。

用虚线绘制的次级环路改善了输出的转换速率时间,因为次级输入来自前级输出。

注入锁定技术被应用于振荡器以降低总相位噪声。在此条件下,注入信号激活连接在其中一个延迟单元差分输出节点处的NMOS开关[20]。通过向NMOS开关注入低噪声信号,注入脉冲将与VCO输出锁定,从而相位误差不再累积。因此,相位噪声得到显著改善,因为它影响了注入锁定振荡频率的噪声整形。

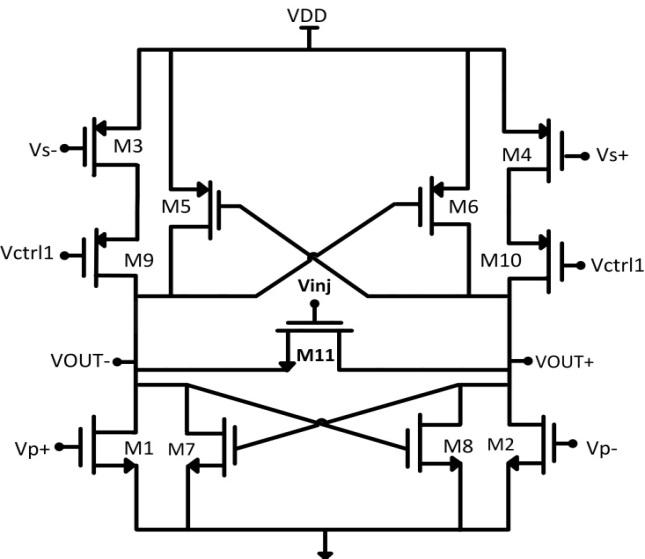

此外,由于振荡器输出信号转换期间注入的噪声量会影响相位噪声,因此对[14]中提出的低噪声延迟单元进行了评估。在此结构中,如图2所示,M1和M2为NMOS输入晶体管,M3和M4为交叉耦合PMOS晶体管,M5和M6为PMOS输入晶体管,Mcont1和Mcont2为PMOS控制晶体管。在该结构中,用于评估半电路时,在高‐低转换期间,晶体管M5关断,因此噪声电流仅受晶体管影响。

受此技术启发,图3展示了所提出的延迟单元,其具有与输入PMOS晶体管串联的PMOS控制晶体管。在此结构中,和是NMOS差分主输入晶体管,和是次级环路的PMOS输入晶体管。晶体管和是PMOS负载,用于产生正反馈并降低功耗。为了实现正反馈锁存器,采用了晶体管和。使用NMOS交叉耦合晶体管不仅提高了开关速度,还扩展了振荡频率范围。为了改变振荡频率,在输入PMOS晶体管上串联使用了晶体管和。如前所述,为了降低振荡器的相位噪声,采用了注入锁定方法。在这种情况下,功耗降低至123.3微瓦,同时通过将控制电压从0伏特调节到1伏特,使振荡频率设置在3.27吉赫兹至871.6兆赫兹的范围内。

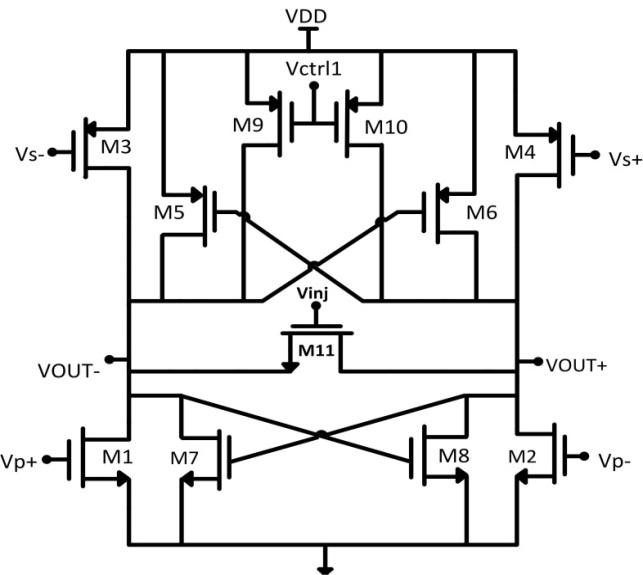

为了降低相位噪声并提高振荡频率,如图4所示,PMOS控制晶体管M9和M10与输入PMOS晶体管并联使用。由于提供了从VDD到输出的额外路径,输出电容负载可以从电压源获取更多电流而更快充电,从而输出频率得以提高。该拓扑结构的优点是振荡器可在11.79至8.12GHz的高频范围内工作。尽管高频具有积极意义,但功耗约为435.9微瓦,不适合低功耗应用。

图5. 具有两个控制电压的所提出的延迟单元

为了在频率范围和功耗之间进行权衡,提出了一种具有两个控制电压的延迟单元,如图5所示。这两个控制电压可以在粗调和细调模式下调节频率。Vctrl1在较宽范围内改变频率,而Vctrl2以细小步进调节频率。在此延迟单元中,功耗为328.6μW,同时频率范围在2.65至13.93GHz之间。

3. 频率分析

环形振荡器的输出电压为正弦或方波波形[21]。根据晶体管工作区域的不同,输出电压电平也会有所差异。当输出频率增加时,输出波形会从方波变为正弦波。通过假设正弦波和方波的波峰,利用输出电压的压摆率可提取出输出频率。因此,输出电压及其压摆率为:

$$

V_{out} = k \sin(\omega t)

$$

$$

\frac{dV_{out}}{dt} = k \omega \cos(\omega t)

$$

其中k为常数,ω为角频率。为了评估每条支路的电流,可以考虑输出处于从VDD转换到零的中间阶段这一条件。因为在VDD/2输出时获得压摆率的最大值;此处ω等于1。

通过将时间设为零并假设k=1,输出的角频率为:

$$

\omega = \left. \frac{dV_{out}}{dt} \right|_{t=0} = k \omega \Rightarrow \omega = \frac{1}{k}

$$

由于从输出端看去,等效电容(CL)的充放电速度即为压摆率,因此我们有:

$$

\frac{dQ}{dt} = I, \quad Q = C_L V, \quad \frac{dV}{dt} = \frac{I}{C_L} \Rightarrow \omega = \frac{I}{C_L}

$$

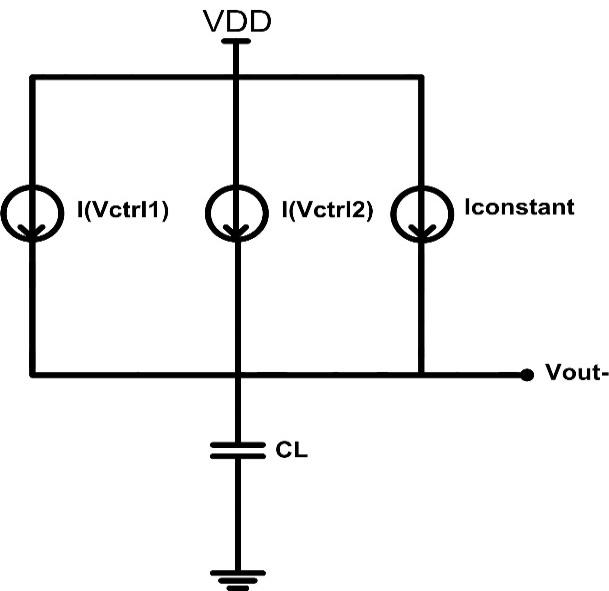

因此

$$

\omega = \frac{I(V_{Ctrl1}) + I(V_{Ctrl2}) + I_{Constant}}{C_L}

$$

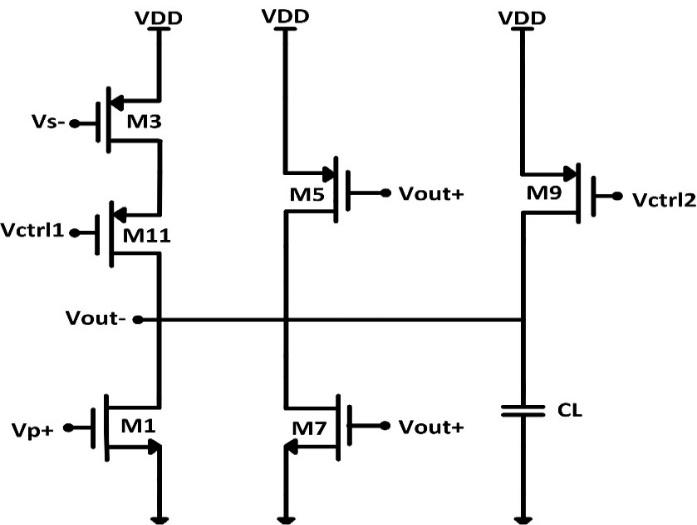

其中,$I(V_{Ctrl1})$ 和 $I(V_{Ctrl2})$ 分别是 $V_{Ctrl1}$ 和 $V_{Ctrl2}$ 的函数,而 $I_{Constant}$ 是与 $V_{ctrl1}$ 和 $V_{ctrl2}$ 无关的电流。需要注意的是,$I(V_{Ctrl2})$ 是 $I_{M5}$ 和 $I_{M9}$ 的总和。因为当增加 $V_{Ctrl2}$ 时,M9 和 M10 的电流减小,相当于降低了 M5 和 M6 的栅极电压,因此 M5 和 M6 的电流增加。

通过调节 M5 和 M9 的尺寸以实现在输出节点处电流的增加,从而使输出频率以细小步进方式增加。因此,$V_{Ctrl2}$ 起到了精细调节作用。

$C_L$是$C_{d1}$、$C_{d5}$、$C_{d7}$、$C_{d9}$和$C_{d11}$的总和。$C_{d1}$、$C_{d5}$和$C_{d7}$与控制电压无关,而$C_{d9}$和$C_{d11}$对控制电压的依赖性非常低。由于交流分析是在$V_{out}=V_{DD}/2$下进行的,因此M9和M11的栅‐漏电压始终低于$V_{DD}/2$。由于晶体管M11存在体效应,它始终工作在饱和区,而M9大部分时间也工作在饱和区。因此,$C_{d9}$和$C_{d11}$对栅极(控制)电压的敏感性较低。从而$C_L$对控制电压的依赖性可以忽略不计。

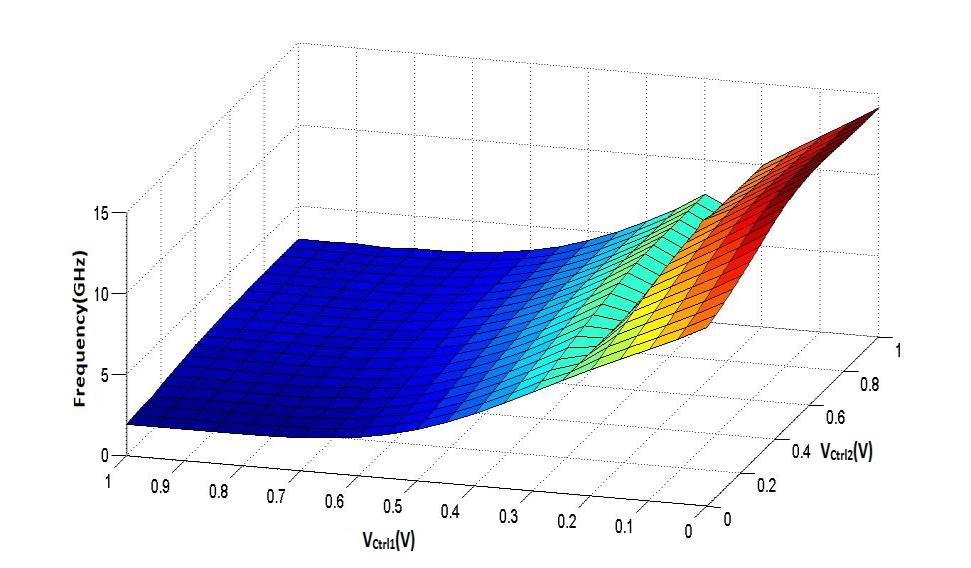

方程(4)和图6验证了频率依赖于控制电压。通过增加$V_{Ctrl1}$,晶体管M11开始关断。在这种情况下,由次级输入(VS)控制的晶体管M3,的影响减弱。由于VS用于提高速度的目的,当该晶体管被断开时,其控制电压起粗调频率的作用,从而使频率降低。此外,当$V_{Ctrl2}$增加时,M9的栅源电压减小,导致其支路电流减小,进而使频率绝对值增加。$V_{Ctrl2}$是细调频率的控制电压,当其超过0.6伏特时,保持频率不变。事实上,PMOS晶体管M9此时关断。类似地,当$V_{Ctrl1}$从0.6伏特继续增大时,PMOS晶体管M11断开,频率也随之固定。

4. 仿真结果

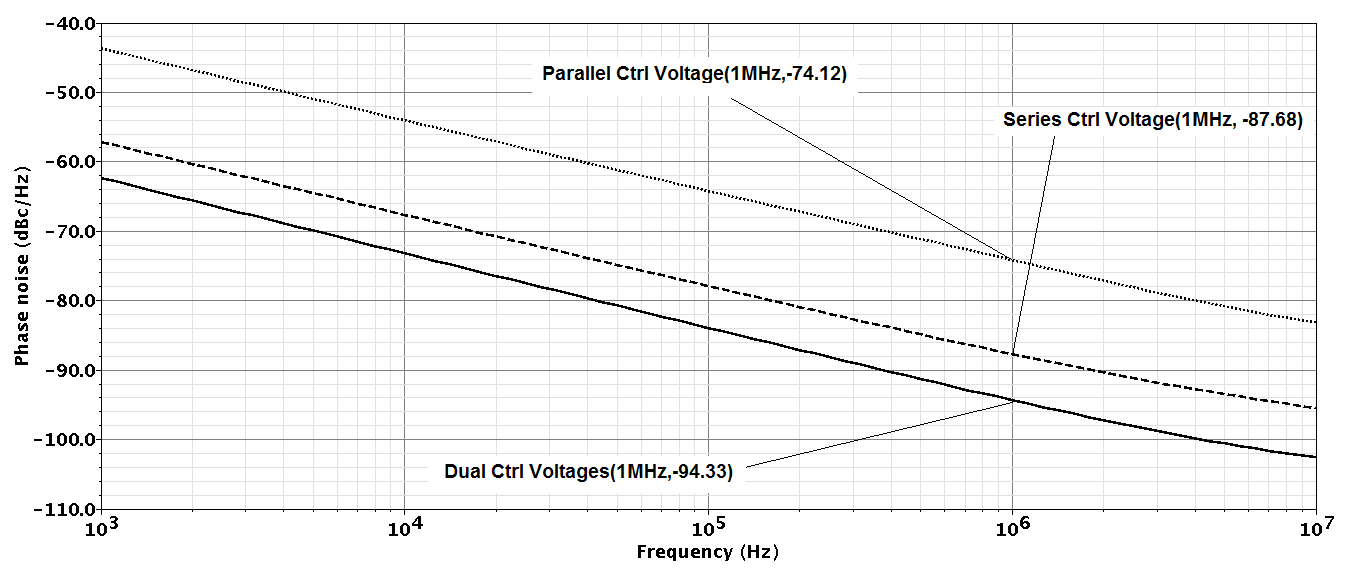

所提出的延迟单元在65纳米台积电CMOS工艺中进行了仿真。三种结构的相位噪声在图7中进行了相互比较。

施加到NMOS开关栅极的注入信号是一个脉宽为20皮秒的100兆赫脉冲。需要注意的是,该信号被注入到四级环形振荡器中的一个延迟单元中。如图7所示,具有两个控制电压的所提出的延迟单元的相位噪声优于其他结构,在1兆赫偏移频率下达到‐94.33分贝每赫兹。

具有串联PMOS控制晶体管的所提出的延迟单元的相位噪声约为‐87.68dBc/Hz,而在1兆赫偏移频率下,具有并联PMOS控制晶体管的延迟单元的相位噪声为‐74.12dBc/Hz。图8展示了每个控制电压对具有两个控制电压的所提出的延迟单元的频率调谐范围的影响。

通过改变VCtrl1从0到1V,当VCtrl1为0.55V时,频率可在13.93至2.65GHz之间变化;而通过将VCtrl1设为0.55V(这是实现宽调谐范围的最佳情况),VCtrl2可在3.8至2.65GHz范围内设置频率,调节范围为0到1V。采用所提出的具有粗调和细调控制电压的延迟单元的四级环形振荡器具有更宽的调谐范围。换句话说,在图3和图4的结构中,通过将Vctrl从0V调节到1V,所实现的调谐范围分别为3.27GHz至871.6MHz和11.79至8.12GHz;而该频率范围在第三种结构中得到进一步改善。因此第三种提出的结构通过为串联和并联路径使用两个控制电压,实现了更宽的调谐范围和更精确的频率调谐范围。

为了更好地进行比较,环形振荡器的品质因数(FOM)由公式(5)[12]计算得出。

$$

FOM = 20 \log \left( \frac{f_{osc}}{f_{off}} \right) + 10 \log \left( \frac{1}{L(f_{off})} \right) - 10 \log \left( \frac{P_{diss}}{1\,\text{mW}} \right)

$$

其中,$L(f_{off})$ 处的偏移频率下振荡器的相位噪声为dBc/Hz,$f_{osc}$为中心频率,$P_{diss}$为以毫瓦为单位的功耗。采用具有两个控制电压的延迟单元的提出的RO的计算的FOM为‐170.53。

表1比较了三种提出的延迟单元的参数。对于这三种结构,环形振荡器的技术、电源电压和级数等条件均相同。如表中所示,具有两个控制电压的延迟单元相比另外两种使用一个控制电压的延迟单元具有更好的调谐范围和相位噪声性能。

表1 三种提出的延迟单元的比较

| 延迟单元技术 (nm) | 电源 (V) | 数量 级数 | 调谐 范围 (GHz) | $f_{osc}$ (GHz) | 相位 噪声 (dBc/Hz) 在1MHz处 | $P_{diss}$ (µW) | FOM |

|---|---|---|---|---|---|---|---|

| 并行控制电压 | 65 | 1 | 4 | 8.12–11.79 | 8.33 | -74.12 | 435.9 |

| 串联控制电压 | 65 | 1 | 4 | 0.871–3.27 | 1.38 | -87.68 | 123.3 |

| 双控制电压 | 65 | 1 | 4 | 2.65–13.93 | 3.7 | -94.33 | 328.6 |

为了评估工艺、电压和温度(PVT)的敏感性,对所提出的采用具有两个控制电压的延迟单元的四级环形振荡器进行了PVT角分析。针对典型、快速‐最佳和慢速‐最差模式,仿真了调谐范围、中心频率和功耗。PVT角分析的仿真结果如表2所示。

表2 采用具有两个控制电压的延迟单元的四级环形振荡器的PVT角分析

| 参数 | 典型 | 快速‐Best | 慢速‐最差 |

|---|---|---|---|

| 调谐范围(GHz) | 2.65–13.93 | 3.6–16.63 | 1.81–11.66 |

| $f_{OSC}$(GHz) | 3.7 | 4.96 | 2.53 |

| $P_{diss}$(µW) | 328.6 | 461.6 | 242.4 |

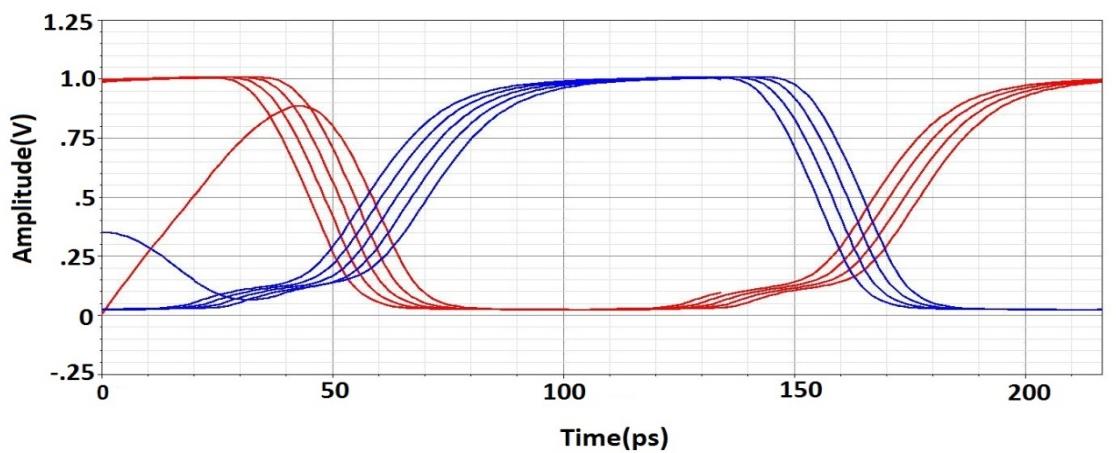

此外,图9展示了具有两个控制电压的提出压控振荡器的眼图。使用3.7Gbps伪随机输出获得该眼图,估计抖动为13.54皮秒抖动。

为了评估电路在工艺和失配变化下的行为,进行了100次运行的蒙特卡洛仿真,结果如图10所示。蒙特卡洛仿真通过重复运行和测试仿真来进行风险分析。测试结果应呈正态分布。由蒙特卡洛仿真得到的钟形曲线的均值和标准差表示围绕中心的变化情况。接近均值的输出结果最有可能出现。所提出电路的仿真结果显示,频率均值为3.77吉赫,标准差为470.72兆赫。

图11(a)所示的具有两个控制电压的 proposed 延迟单元的布局面积估计约为 20.96μm²;而如图11(b)所示,四级环形振荡器占用了 139.5μm²。

具有两个控制电压的 proposed 延迟单元的布局)

具有两个控制电压的 proposed 延迟单元的布局)

四级环形振荡器的布局)

四级环形振荡器的布局)

表3将采用具有两个控制电压的延迟单元的提出的环形振荡器与采用相同技术的其他近期发表的论文进行了比较。从该表中可以明显看出,所提出的延迟单元在具有更宽频率范围的其他四级环形振荡器中功耗最低。同时,由于在其布局中采用了指状和中心点技术,芯片面积也得到了改善。通过使用两个控制电压,与其它传统环形振荡器相比,调谐范围得到了提升,同时相位噪声也尽量保持与其他设计相当。

表3 与其他VCO的性能比较

| Ref. | 技术 (nm) | 电源 (V) | 数量 级数 | 调谐 范围 (GHz) | 有源 Area (μm²) | $f_{osc}$ (GHz) | 相位 噪声 (dBc/Hz) 在1MHz处 | $P_{diss}$ (mW) | FOM (dBc/Hz) |

|---|---|---|---|---|---|---|---|---|---|

| [1] 2014 | 65 | 0.7 | 3 | 0.83–3.77 | 67.65 | ------- | 26.73 × | — | |

| [9] 2015 | 65 | 1.2 | 4 | 1.55 – 3.9 | — | 3 | -94 | 7.68 | -77 |

| [12] 2016 | 65 | 1.2 | 3 | 2.5 – 7 | 1.05 | 5.3 | -89.2 | 2.2 | -160.26 |

| [14] 2013 | 65 | 1 | 4 | 0.48 – 1.01 | 22.54× | 0.645 | -110.8 | 10 | -157 |

| [18] 2013 | 65 | 1.2 | 2 | 2 – 8 | 38 | 4.2 | -101 | 6.4 | -187 |

| This work | 65 | 1 | 4 | 2.65–13.93 | 139.5 | 3.7 | -94.33 | 328.6× | -170.56 |

5. 结论

提高调谐范围以及降低功耗是本工作的目标,该工作应用于四级双延迟环振荡器。所提出的延迟单元包含两对控制晶体管,它们与PMOS输入晶体管并联和串联使用。仿真在65纳米CMOS技术下通过Cadence软件完成。该仿真结果表明,在1兆赫偏移频率处相位噪声为‐94.33分贝每赫兹,3.7吉赫中心频率下的功耗为328.6毫瓦,频率调谐范围为2.65至13.93吉赫兹。根据其布局估算的芯片面积为139.5微米²,而延迟单元占据20.96微米²。该环形振荡器专为时钟数据恢复应用设计。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?