提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

文章目录

前言

PCI Express (Peripheral Component Interconnect Express),通常简写为 PCIe,是一种高速串行计算机扩展总线标准。它被设计用来替代旧的PCI、PCI-X和AGP总线标准,广泛应用于个人电脑、服务器、嵌入式系统等设备中。PCIe的主要目的是提供一个更高性能、更低延迟的数据传输解决方案,支持更高效的电源管理,并允许热插拔(即在不关闭系统的情况下添加或移除硬件组件)。

PCIe接口通过一系列的连接通道(被称为“lanes”)来传输数据,每个lane由两对线路组成:一对用于发送数据,另一对用于接收数据。根据不同的配置,PCIe卡可以使用单个lane (x1) 到最大32个lane (x3/XMLSchema 32,但在实际应用中很少见)。目前,PCIe技术已经发展到了第五代(PCIe 5.0),其数据传输速率相较于初代有了显著提高。例如,PCIe 4.0 x16配置可以提供高达64 GB/s的双向数据传输速度。

PCIe常用于连接各种高性能组件,如显卡、固态硬盘、网卡、声卡以及其他需要高速数据传输的外围设备。随着技术的进步,PCIe规范也在不断更新以满足日益增长的带宽需求和性能要求。

PCIE6.0-Flit_Mode学习

一、新增的Flit模式是什么?

Flit Mode是PCIe 6.0中新增的一种全新的数据传输机制,和之前有很大的改变。它支持更高的数据传输速率、改进的信号完整性和更高效的带宽利用。数据被分割成固定大小的数据包,成为Flow Control Units(FLITs),每个FLIT固定大小为256字节。

Flit Mode的主要特点和优势包括:

1、固定大小的数据包:使用固定大小的FLIT可以简化数据链路层的设计,并提高带宽效率,因为不需要额外的开销来处理不同大小的TLP头部。

2、内置错误检测与纠正:每个FLIT都包含自己的循环冗余校验(CRC),这意味着不再需要像前几代那样为TLP和DLLP单独提供CRC字节。此外,轻量级前向纠错(FEC)被用来降低误码率,同时保持低延迟。

3、支持高数据速率:PCIe 6.0将数据速率提升到了64GT/s,并且由于采用了PAM-4编码,使得在高频率下信号更加稳定。Flit Mode配合轻量级FEC解决了PAM-4带来的误码问题,从而允许系统在不显著增加延迟的情况下达到更高的可靠性。

4、减少延迟:尽管FEC通常会增加延迟,但PCIe 6.0使用的轻量级FEC仅引入了很小的延迟(如2ns到32ns不等,取决于链路宽度),这使得总往返时延显著降低至约25ns左右。

5、新的电源管理状态L0p:这是专门为Flit Mode设计的一种新的低功耗状态,可以在不影响数据流的情况下动态调整链路宽度,以节省电力。

二、Flit Mode 结构组成是怎么样的?

1.Flit 组成和Flit Type

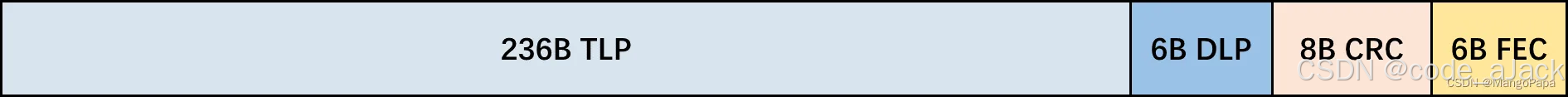

当使用Flit Mode时,在PCIE6.0协议4.2.3中说由 236B TLP + 6BDLP+ 8B CRC + 6B ECC 共 256B 一个Flit作为最小单位进行传输。

当使用Flit Mode时,在PCIE6.0协议4.2.3中说由 236B TLP + 6BDLP+ 8B CRC + 6B ECC 共 256B 一个Flit作为最小单位进行传输。

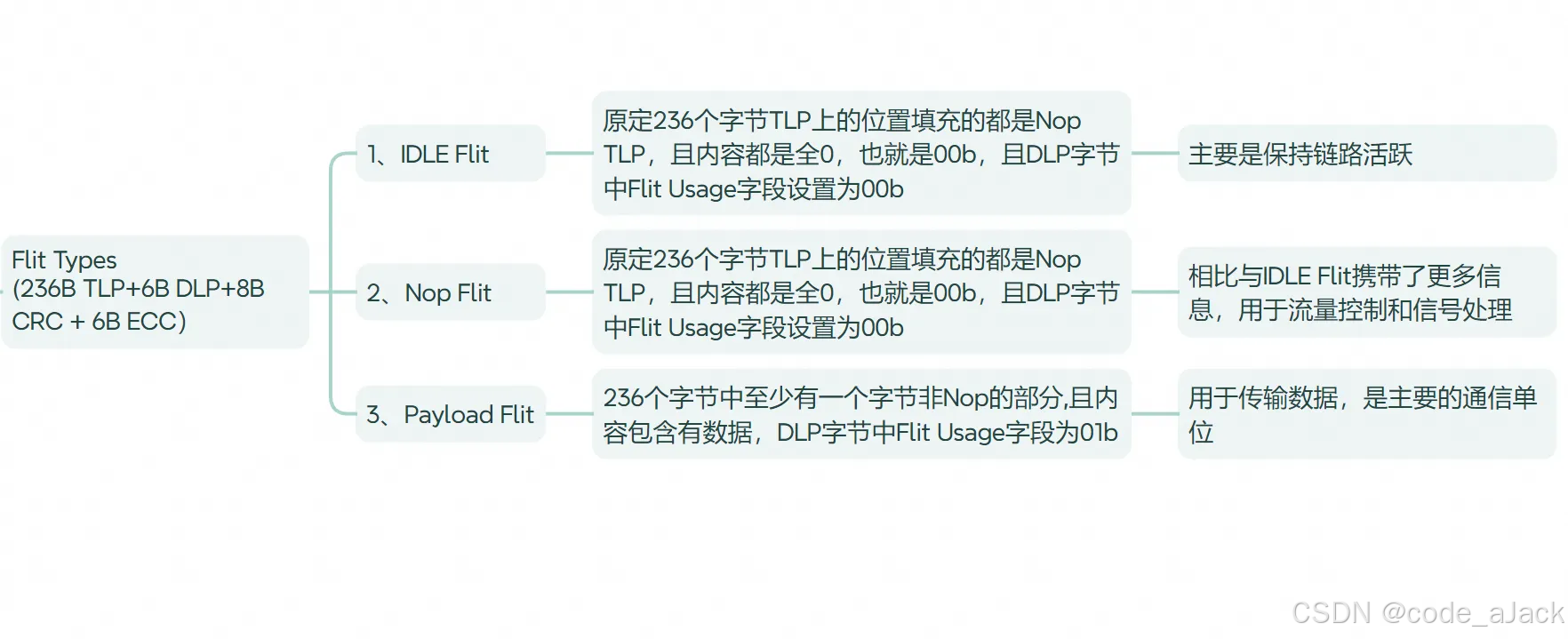

而Flit Type又分为三类,分别为Idle Flit、Nop Flit、Payload Flit

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

82

82

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?