本篇文章是博主阅读tessent IJTAG ug的笔记,如果有理解不正确的地方,还请各位大佬指出。

IJTAG也称之为1687协议,而tessent的IJTAG ug是对IJTAG协议的提炼,因此读者不需要去全部阅读IJTAG的协议,只需要阅读tessent IJTAG ug即可。

Tessent IJTAG主要由三部分组成:

Hardware rule(硬件语言): 包括port的function,timing,connction rules

Instrument Connectivity Language(ICL): 描述了独立的节点,以及部分或者全部网络。从而让你可以进行iwrite或者iread这些pin/register

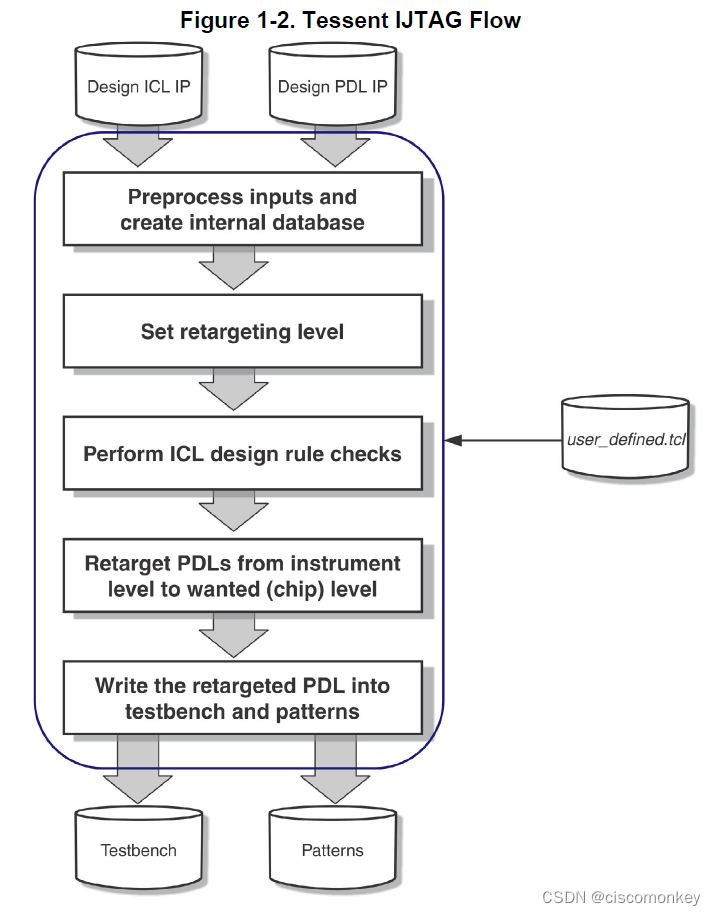

Procedure Description Language(PDL): pdl描述了对这些pin/register的操作,比如你在core level进行iread/iwrite的动作,只需要吃了这个core-level的pdl,就可以映射到top层。

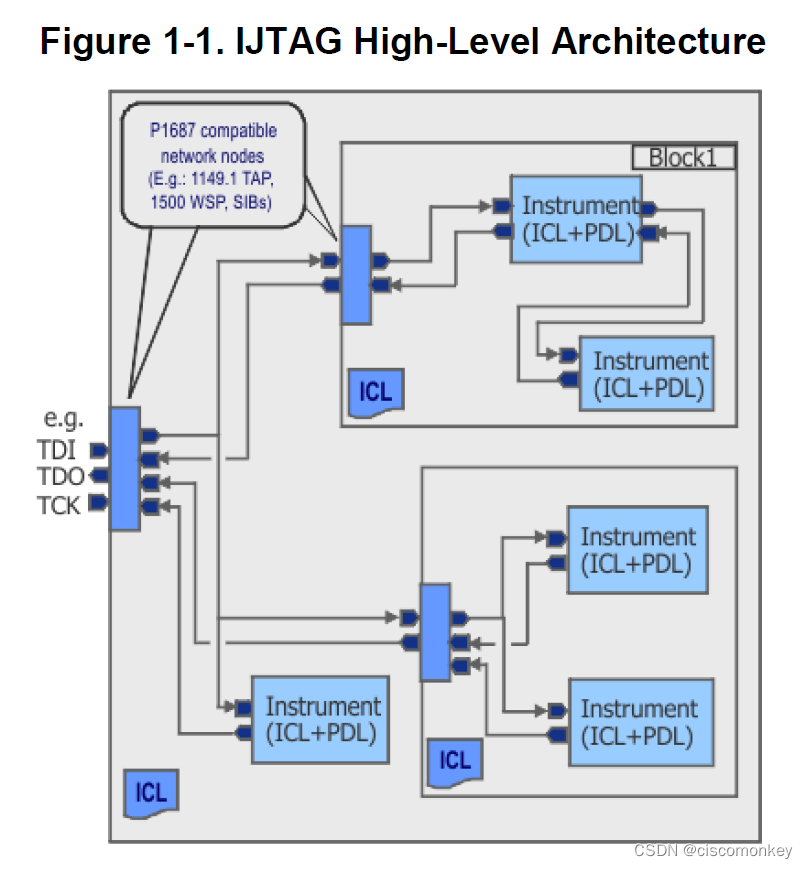

如下图所示,在block层有对每个core-level的ICL+PDL, 有了ICL+PDL 我们就称之为instrument,也就是说知道这些instance之间的port链接性,也知道了对这些接口的操作(iwrite/iread)。从而在top集成的时候,可以用jtag对这些iwrite/iread进行真正的写入值和观察值。

instrument 是指具有1687 interface的IP都可以称之为instrument,

包括了:BIST controller\TestKompressIP\PLL等

此外,所有1687的标准件,也称之为instrument,比如TDR,SIB,TAP等

上面是tessent IJTAG的Flow流程,但IEEE描述的IJTAG,在tessent IJTAG中可能并不一定可以支持,比如有的cmd,当然先知道有这样的局限性即可。

本文档介绍了Tessent IJTAG工具对IEEE 1687 IJTAG协议的简化理解和应用。Tessent IJTAG由硬件规则、Instrument Connectivity Language (ICL) 和Procedure Description Language (PDL) 三部分组成,用于描述IP核的互联及操作。ICL定义了仪器间的连接,PDL则描述了对这些接口的操作。通过ICL和PDL,可以创建instrument并使用JTAG进行读写操作。博客还提到了一些不被Tessent支持的IEEE IJTAG命令,并展示了Tessent IJTAG的工作流程。

本文档介绍了Tessent IJTAG工具对IEEE 1687 IJTAG协议的简化理解和应用。Tessent IJTAG由硬件规则、Instrument Connectivity Language (ICL) 和Procedure Description Language (PDL) 三部分组成,用于描述IP核的互联及操作。ICL定义了仪器间的连接,PDL则描述了对这些接口的操作。通过ICL和PDL,可以创建instrument并使用JTAG进行读写操作。博客还提到了一些不被Tessent支持的IEEE IJTAG命令,并展示了Tessent IJTAG的工作流程。

298

298

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?