11.串口接收原理与思路

1.原理

-

基本原理:采样。

-

技巧是:一位数据采多次,统计得到该电平出现的次数,次数多的就是该电平值。

-

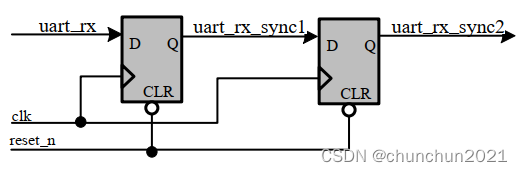

起始位检测:通过边沿检测电路。

-

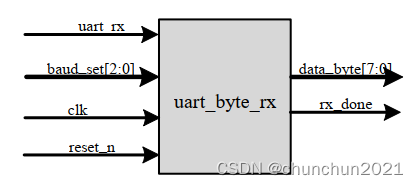

串口接收模块整体框图

2.思路

-

对边沿电平进行检测

-

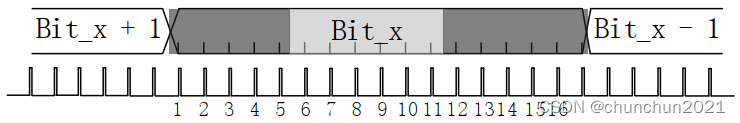

波特率的设置,我们这里要把它分割成16份

-

对(bps_cnt)16位操作 总共10位数据 那么要计数到160

-

接收16个格子中的中间的数据(r_date,sto_date,sta_date )

-

基本的分频器(div_cnt)来得到bps_clk = ( div_cnt == Bps_DR /2) 和 使能端口(RX_EN)

-

接收数据

-

处理rx_done

3.代码

`timescale 1ns / 1ps

module uart_byte_tx(

sys_clk , sys_rst , baud_set ,date_rx , date , rx_done );

input sys_clk ;

input sys_rst ;

input [2:0] baud_set ;

input date_rx ;

output reg [7:0] date ;

output reg rx_done ;

// 1. 滤波

// reg date_rx_sync_1 ;

// reg date_rx_sync_2 ;

// wire date_rx_sync ;

// always@(posedge sys_clk or negedge sys_rst )

// if(!sys_rst)

// begin

// date_rx_sync_1 <= 0 ;

// date_rx_sync_2 <= 0;

// end

// else

// begin

// date_rx_sync_1 <= date_rx ;

// dat

该文详细阐述了串口接收的原理和思路,包括通过采样确定数据电平、边沿检测来识别起始位,以及使用分频器设置波特率。在Verilog代码中,实现了滤波、波特率配置、边沿检测、数据接收和计数等功能,以完成串行数据到并行数据的转换。

该文详细阐述了串口接收的原理和思路,包括通过采样确定数据电平、边沿检测来识别起始位,以及使用分频器设置波特率。在Verilog代码中,实现了滤波、波特率配置、边沿检测、数据接收和计数等功能,以完成串行数据到并行数据的转换。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1506

1506

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?