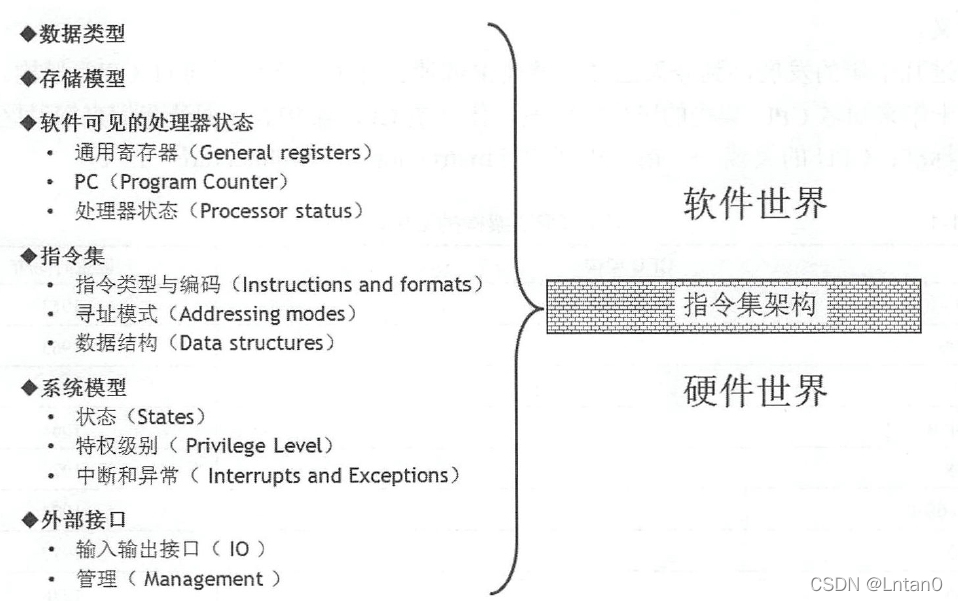

提起RISC-V,我们不得不提的一个词便是指令集架构(ISA)。

那么,何谓“ISA”,ISA可以称得上是CPU的灵魂,有时简称为“架构”或者称为“处理器架构”。

上图对ISA做了一个详细的描述,这里便不再赘述。

有了指令集架构,便可以使用不同的处理器硬件实现方案来设计不同性能的处理器。处理器的具体硬件实现方案称为微架构(Microarchitecture)。

RISC-V(英文读作“risk-five”),是一种全新的指令集架构。RISC-V架构主要由美国加州大学伯克利分校的几名教授于2010年发明。伯克利的开发人员之所以发明一套新的指令集架构,而不是使用成熟的X86或者arm架构,是因为这些架构经过多年的发展,变得极为复杂和冗杂,并且存在高昂的专利和架构授权问题。因此,RISC-V架构是一种全新的,简单且开放免费的指令集架构。

简单介绍一些CPU原理:

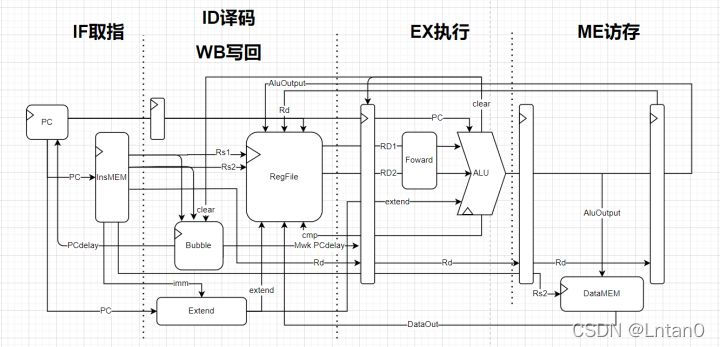

1.经典的五级流水线

一条指令的流程:取指>译码>执行>访存>写回

简单提及一个概念:流水线深度

越来越深的流水线:追求高性能

越来越浅的流水线:追求低功耗

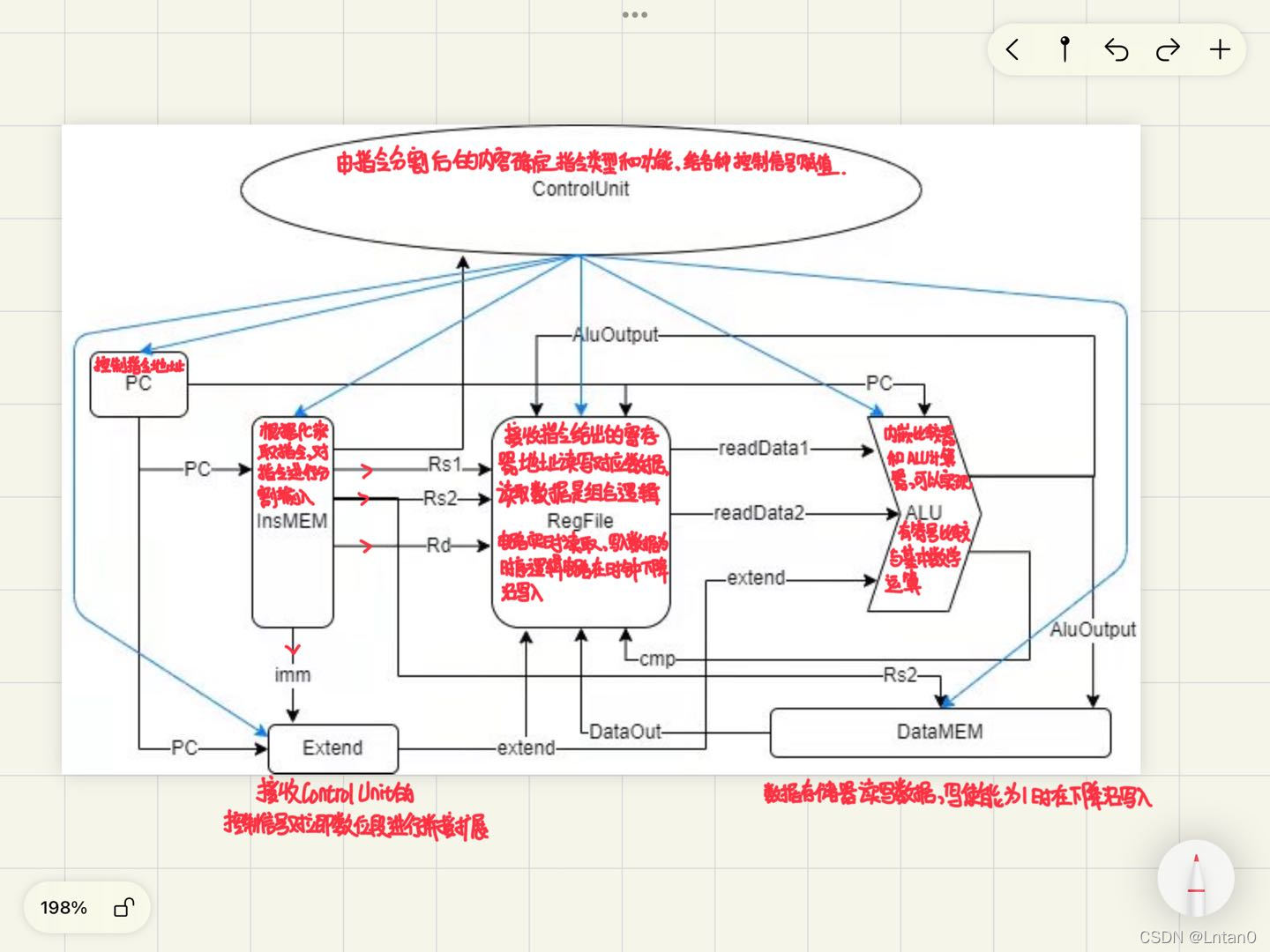

2.CPU数据通路

关于比赛

赛题:基于蜂鸟E203 RISC-V内核的智能识别SoC设计与应用系统开发

内容:基于芯来科技的开源蜂鸟E203 Demo SoC(e203_hbirdv2)进行扩展, 在限定的可编程逻辑平台上构建面向智能识别应用领域的SoC,进而完成实际的应用系统开发。要求在所搭建的SoC中实现专门的硬件加速器以提高系统整体性能,所实现的应用系统具有创新性、实用性以及市场应用前景。

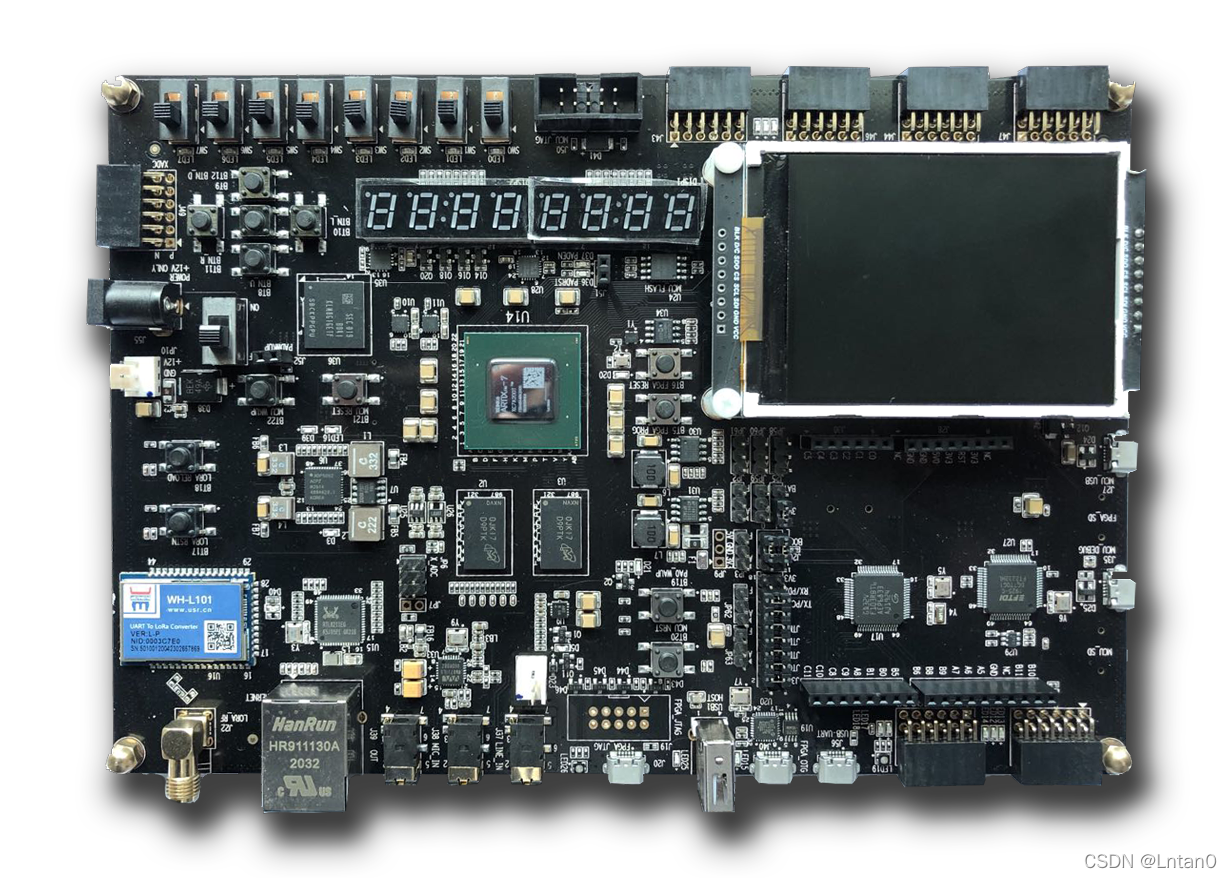

吐槽一下:借不到&买不起板子也太劝退了

(Nuclei MCU200T,售价2499)

(Nuclei DDR200T,售价4999)

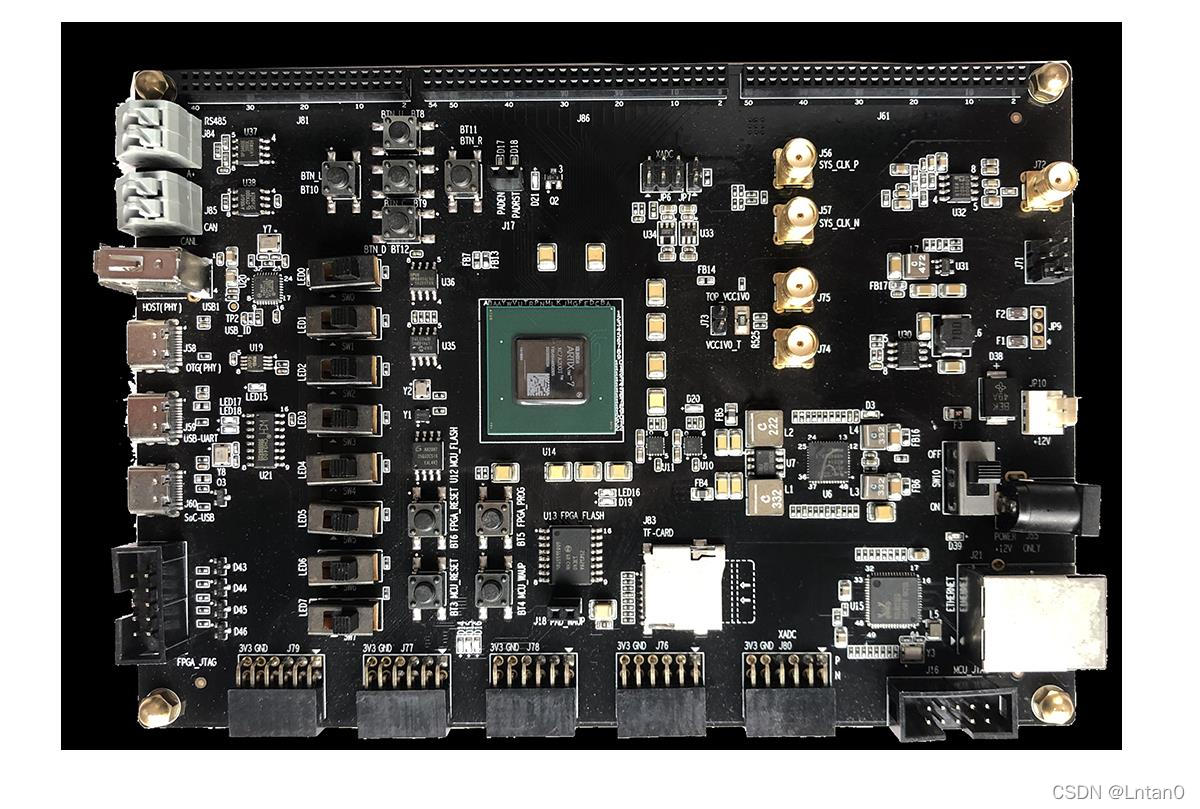

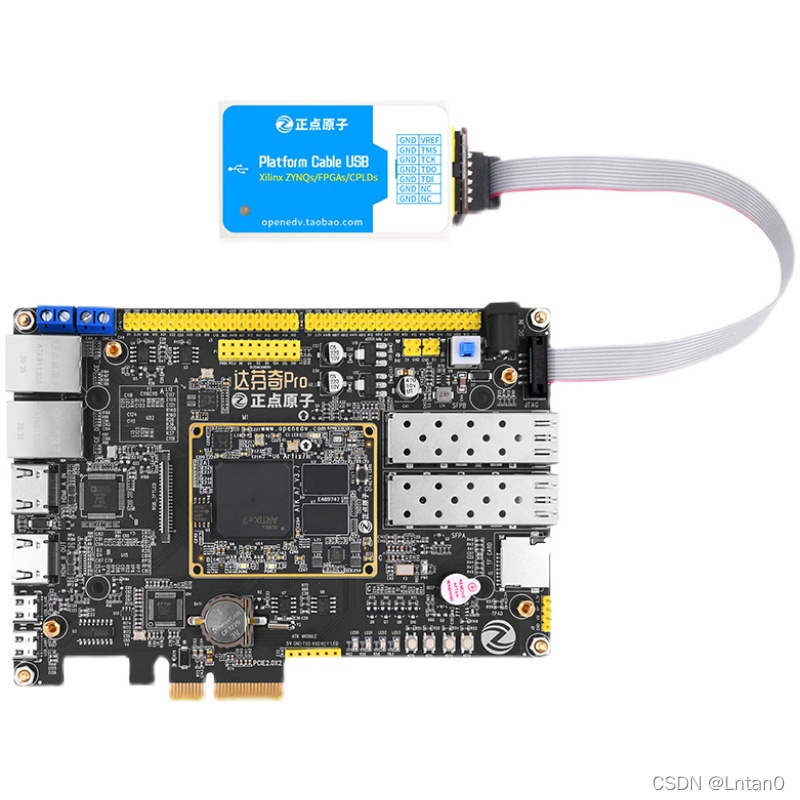

最后在实验室王学长的支持下,买到了一款开发板

(达芬奇pro 35T,售价1526)

熟悉板子,最头疼的还是将E203 soc内核移植到板子里(网上教程几乎为0)

移植教程会在后续发出

分享只为学习交流,还望大佬们不吝赐教🥰

本文介绍了RISC-V指令集架构的背景及其作为CPU灵魂的重要性,对比了复杂的X86和ARM架构。作者参与了一项基于蜂鸟E203RISC-V内核的SoC设计比赛,面临硬件成本和移植教程稀缺的挑战,最终在实验室支持下购得开发板进行实践。文章分享了CPU的五级流水线原理和数据通路,并预告了E203soc内核移植教程。

本文介绍了RISC-V指令集架构的背景及其作为CPU灵魂的重要性,对比了复杂的X86和ARM架构。作者参与了一项基于蜂鸟E203RISC-V内核的SoC设计比赛,面临硬件成本和移植教程稀缺的挑战,最终在实验室支持下购得开发板进行实践。文章分享了CPU的五级流水线原理和数据通路,并预告了E203soc内核移植教程。

6160

6160

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?