AMD Vivado™ 集成设计环境 (IDE) 提供了多项报告命令,用于验证设计是否满足所有时序约束,以及是否准备好加载到应用开发板上。“Report Timing Summary”(时序汇总报告)属于时序验收报告,等同于 ISE Design Suite 中的 TRCE。“Report Timing Summary”可提供所有时序检查的完整概览,并显示充足的信息以支持您开始对任何时序问 题进行分析和调试。

可在窗口中生成此报告、将其写入文件或者打印到 log 日志文件中。当“Report Timing Summary”显示设计不 满足时序或者缺少某些约束时,可浏览汇总报告各部分中提供的详细信息并运行更具体的分析。其他时序报告可提供 有关特定状况的更多详细信息,并且可通过使用筛选工具和限定作用域功能来将分析限定于某些逻辑。

1、时序路径

时序路径是由设计实例之间的连接定义的。在数字化设计中,时序路径由一对时序元件组成,这对时序元件受相同时钟 或 2 个不同时钟控制。

任意设计中最常见的路径为:

• 从输入端口到内部时序单元的路径

• 从时序单元到时序单元的内部路径

• 从内部时序单元到输出端口的路径

• 从输入端口到输出端口的路径

从输入端口到内部时序单元的路径

在从输入端口到时序单元的路径中,数据:

• 在器件外部由开发板上的时钟发送。

• 经延迟后到达器件端口,此延迟称为输入延迟(Synopsys 设计约束 (SDC) 定义)。

• 通过器件内部逻辑传输后到达由目标时钟进行时钟设置的时序单元。

从时序单元到时序单元的内部路径

在从时序单元到时序单元的内部路径中,数据:

• 在器件内部由时序单元发送,该时序单元的时钟由源时钟进行设置。

• 通过部分内部逻辑传输后到达由目标时钟进行时钟设置的时序单元。

从内部时序单元到输出端口的路径

在从内部时序单元到输出端口的路径中,数据:

• 在器件内部由时序单元发送,该时序单元的时钟由源时钟进行设置。

• 传输穿过部分内部逻辑,然后到达输出端口。

• 经过称为输出延迟(SDC 定义)的附加延迟后,由板上时钟捕获。

从输入端口到输出端口的路径

在从输入端口到输出端口的路径中,数据无需锁存即可遍历整个器件。此类路径通常也称为输入到输出路径 (in-to-out path)。输入和输出延迟参考时钟可能是虚拟时钟,也可能是设计时钟。

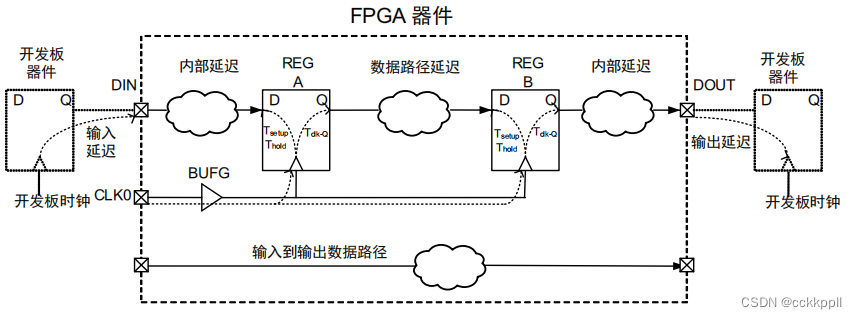

下图显示了以上描述的路径。在此示例中,设计时钟 CLK0 可用作为 DIN 和 DOUT 延迟约束的开发板时钟。

每条时序路径均由 3 个部分组成:

• 源时钟路径

• 数据路径

• 目标时钟路径

源时钟路径

源时钟路径是源时钟从源点(通常为输入端口)到发送时序单元的时钟管脚的路径。对于始于输入端口的时序路径,不存在源时钟路径。

数据路径

数据路径表示在其中传输数据的时序路径(介于路径起点与路径端点之间)。适用如下定义:(1) 路径起点为时序单元 时钟管脚或数据输入端口;(2) 路径端点为时序单元数据输入管脚或数据输出端口。

目标时钟路径

目标时钟路径表示目标时钟从源点(通常为输入端口)到捕获时序单元的时钟管脚的路径。对于终止于输出端口的时序 路径,不存在目标时钟路径。目标时钟路径 显示了典型时钟路径所包含的 3 个部分。

文章介绍了AMDVivado集成设计环境中的时序报告功能,特别是ReportTimingSummary,用于验证设计满足时序约束。详细解释了时序路径的不同类型,包括输入到内部、内部到内部、内部到输出以及输入到输出路径,强调了源时钟、数据和目标时钟路径的重要性。

文章介绍了AMDVivado集成设计环境中的时序报告功能,特别是ReportTimingSummary,用于验证设计满足时序约束。详细解释了时序路径的不同类型,包括输入到内部、内部到内部、内部到输出以及输入到输出路径,强调了源时钟、数据和目标时钟路径的重要性。

1119

1119

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?