14 案例研究:三维集成电路中的 热耦合

章节大纲

14.1 热传播测试电路.382

14.1.1 三维集成电路制造技术.383

14.1.2 三维测试电路.383

14.2 实验设置与实验.384

14.3 基于实验结果的设计考虑.395

14.3.1 模块布局对热点形成的影响及缓解技术............ 395

14.3.2 水平与垂直热导通道.395

14.3.3 多个对齐的有源模块.399

14.3.4 多个非对齐的有源模块.399

14.3.5 其他设计考虑.401

14.4 使用仿真验证实验结果.401

14.4.1 仿真设置与工具.403

14.4.2 与实验结果的比较.403

14.4.3 硅通孔密度对热耦合的影响.407

14.5 总结.408

在之前的章节中讨论了三维集成电路中热问题的重要性。之前的研究工作(其中一些也在第 12章,热建模与分析中讨论过)主要集中在对3D集成电路内热点形成和传播的仿真[548]和建 模[459, 552,553]。诸如3D‐ICE[551]以及HotSpot的3D扩展[552,553]等工具已被开发出 来,用于模拟3D电路的热分布,并根据每个器件平面的功耗需求提供热点形成的可视化解释。

模型和仿真已扩展到模块级布局规划,包括全局布线拥塞,从而可以根据热热点的位置调整 三维集成电路中高活跃度模块的位置[351,554–556]。此外,还提出了其他缓解技术,包括使 用被动技术如热通硅过孔(TTSVs)[489]以及主动技术如微通道或微流体冷却[455,477],, 以解决三维集成电路中的散热问题。

尽管大量的理论研究已经加深了对3D集成电路中热传导的理解,但在量化器件平面之间 热量流动方面的实验研究仍然有限。Meindl 等人通过实验表征了微流体冷却技术对二维和三 维电路的影响 [557–559]。其他实验结果也表征了微流体冷却方法[455]。已有研究描述了针对垂直堆叠DRAM/多处理器片上系统的层间冷却系统实 验[560]。还描述了对封装的逻辑芯片上DRAM三维集成电路中热热点的数值和实验表征[561]。

与本研究类似,探讨了层间热传播问题。然而,本章所述结果的主要目的是表征层内和层间 热耦合,以改进堆叠集成电路的设计方法和技术。本文讨论的实验结果有助于深入了解热源 位置和主动冷却对3D集成电路内热梯度的影响。

特扎伦半导体公司已在130纳米CMOS技术中制造了一个测试电路,该电路采用直径为 1.2 μm的硅通孔。使用面对面键合技术将两层逻辑器件垂直堆叠。该测试电路还旨在评估层 间和层内热阻对热点形成的影响。

本章由以下几节组成。热传播测试电路在第14.1节中进行描述。一组测试配置的热耦合 实验表征在第14.2节中给出。关于实验结果的讨论,包括热点形成的影响及缓解技术,在第 14.3节中提供。实验结果与仿真的比较在第14.4节中给出。一些结论在第14.5节中提出。

14.1 热传播测试电路

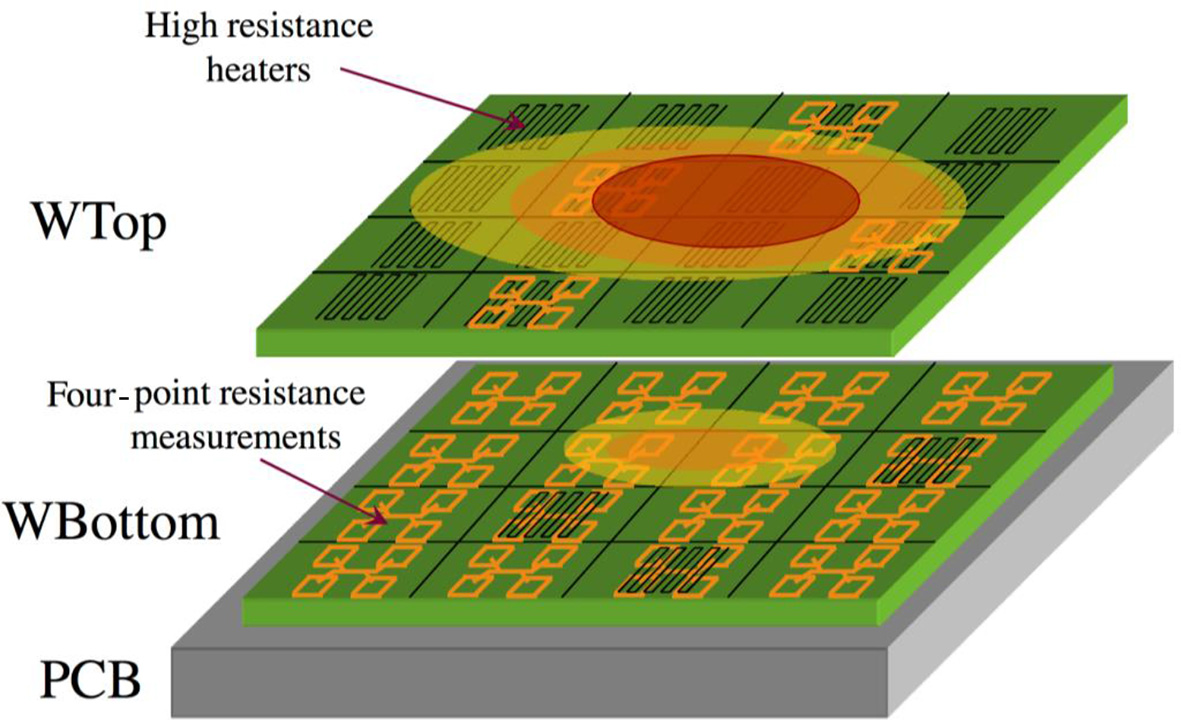

已制造出一种由两层硅组成并在其中一个器件平面上具有背面金属的三维测试电路,用于实 验性分析3D集成电路中的水平和垂直热耦合。实验结果有助于评估基于硅通孔的三维结构内 的热传播路径。该测试电路的示意图如图14.1所示。

14.1.1 三维集成电路制造技术

每个器件平面在三维键合、硅通孔制造和晶圆减薄之前,均由特许半导体公司采用130纳米 CMOS技术单独加工。特许半导体的制造工艺包括低功耗1.5伏和2.5伏晶体管、每个器件平 面上的六层金属层、单多晶硅层、2.5伏晶体管的双栅极,以及低阈值和标称阈值电压器件 [562]。每块芯片的第六层金属层专用于面对面键合,以垂直堆叠两个逻辑器件平面。

14.1.2 三维测试电路

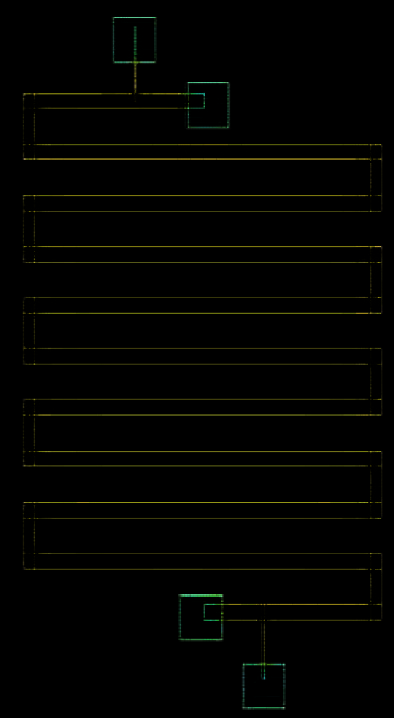

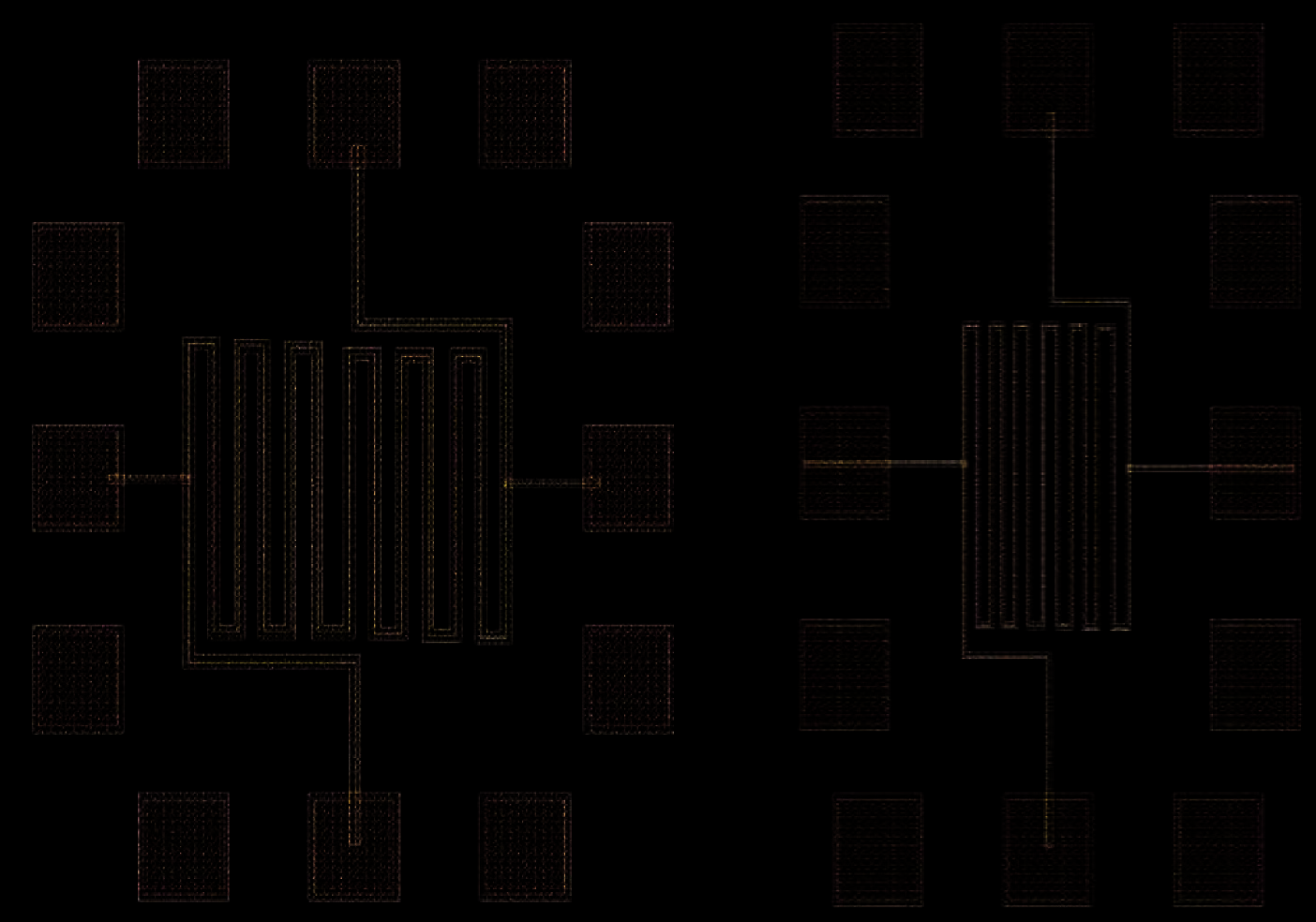

测试结构旨在研究相邻层之间的热耦合,包含电阻式热源和温度传感器。温度传感器采用四 点电压测量方法。每个热源与位于相邻金属层上的电阻热传感器配对,这些配对分布在双层 三维堆叠的每一层中。热源为加热电阻,最大施加电压为28伏,产生最大电流为1.5安培。加 热器位于金属层2,尺寸为 200 μm × 210 μm,与[561],中的加热器尺寸相似。在此区域内, 加热器的总长度为2,120 μm,宽度为6 μm。金属层2的厚度为0.42 μm,标称方块电阻为0.053 Ω/□。因此,加热器的电阻为18.7 Ω。通过控制电流来调节电阻加热器中的焦耳热,从而 控制在 200 μm × 210 μm区域内的I²R功耗。尺寸为 200 μm × 86 μm的温度传感器直接 放置在金属层3中加热器的上方。传感器的总长度为4,442 μm。当宽度为 2 μm、金属层3厚度 为0.42 μm、标称方块电阻为0.053 Ω/□时,传感器的电阻为117.7 Ω。温度传感器在小电流下 进行校准的四点测量,以避免焦耳热的影响。电阻加热器、热传感器以及组合的加热器和传 感器如图14.2所示。

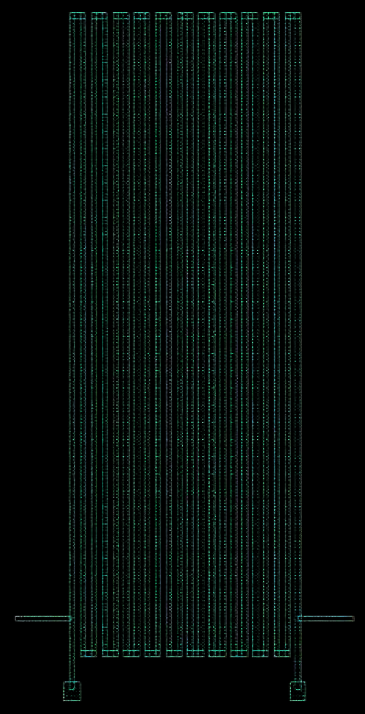

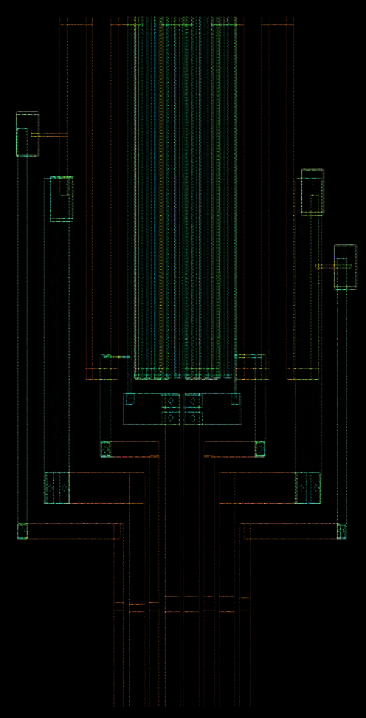

类似的电阻加热器和热传感器包含在铝背侧金属层中,如图14.3A和B所示。位于逻辑层 和背面金属中的加热器与传感器之间的差异包括:(1)由于仅有一个背面金属层,因此加热 器和传感器不像在逻辑层中那样在相邻金属层上垂直堆叠;(2)背面金属层的厚度几乎是金 属层2或3的三倍厚度(1.2 μm 对比 0.42 μm);(3)由于宽度和厚度更大,更大的电流通 过背面金属层。背面金属上的加热器和传感器通过减薄硅与内部逻辑层上的温度传感器实现 热耦合,从而增强的理解了热量通过硅向邻近器件平面热扩散的影响。

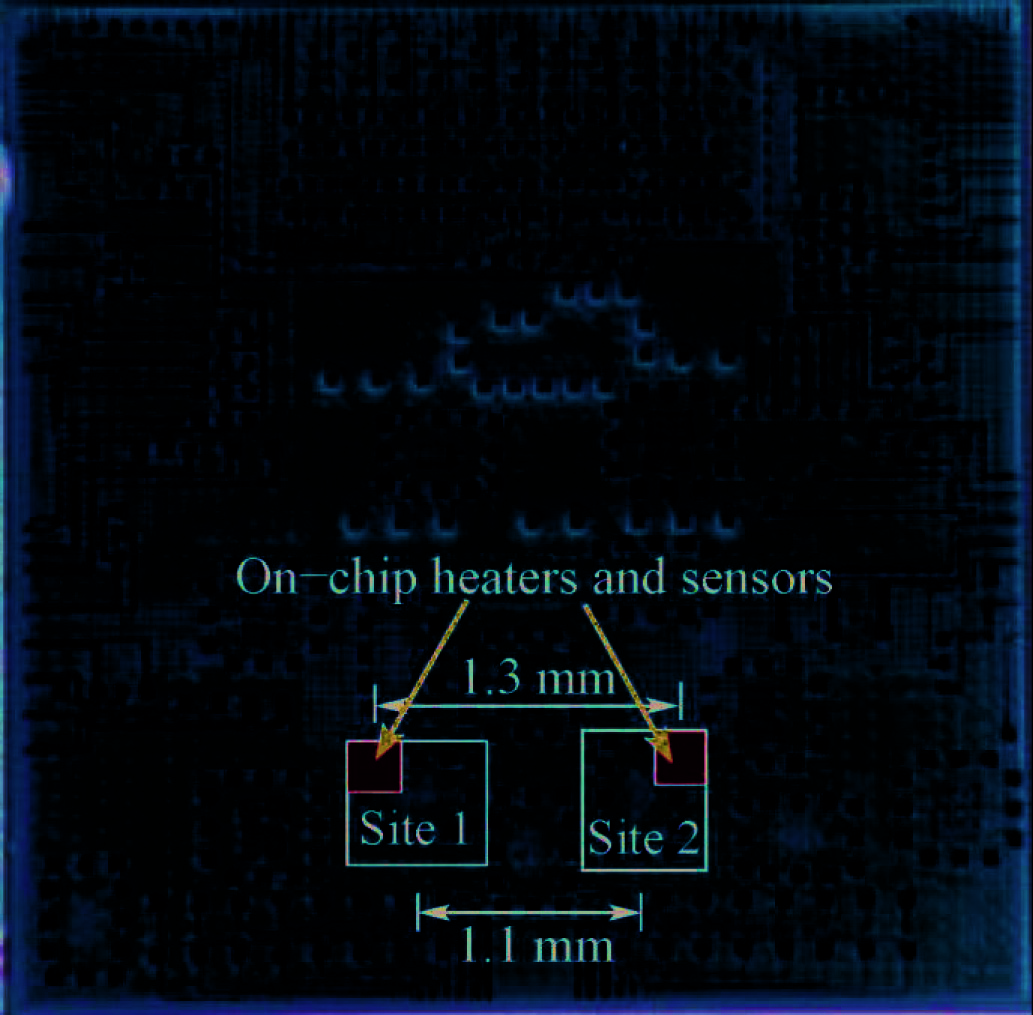

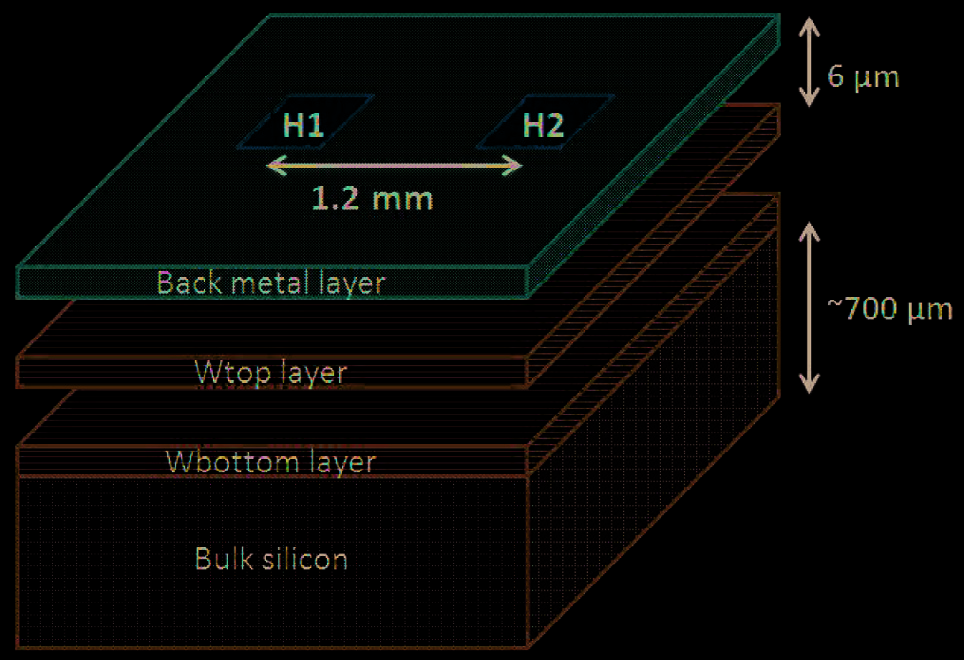

片上热传感器和电阻加热器相对于背面传感器的位置如图14.4所示。一个5 mm×5 mm的3D集成电路的显微照片显示了两个采集热数据的位置。背金属传感器之间的中心到中 心距离为1.1毫米,而片上传感器之间的间距为1.3毫米。完整的3D集成电路堆叠的截面图如 图 14.5所示。每个器件平面(在图中标记为WTop和WBottom)均包含位于金属层3上的热 传感器和位于金属层2上的电阻加热器。背面金属加热器和传感器位于堆叠的顶部,如图 14.5所示。此外,示意图中还标出了WBottom硅和测试结构有源部分的厚度。

在 图 14.5中,表明到三维堆叠顶部的热阻路径明显小于到下方电路板的热阻路径。

直径为1.25 μm的硅通孔在WTop和WBottom上以 100 μm的间距布置。硅通孔对热传播 过程的影响极小。该测试电路的重点是研究堆叠集成电路中的水平和垂直热耦合。此外,最 近的研究表明,放置过多的硅通孔,特别是小直径硅通孔(此时更大比例的面积被绝缘材料 (即SiO₂)占据),实际上会提高芯片温度,因为与被替代的硅相比,绝缘材料的导热性能 较差 [563]。影响散热特性的更关键参数是硅衬底的物理特性 [564]。

14.2 实验设置与实验

片上和背面金属热传感器在进行逻辑层之间热耦合的实验分析之前需要进行校准。校准通过 温控卡盘设置晶圆温度,并在从室温(27°C)到 120°C 的每个温度下测量传感器的电阻来 完成。用于校准片上和背面金属四端热传感器的电阻数据见 表 14.1。使用温控加热板来

| 表 14.1 | 片上和背面金属热传感器的校准数据 |

|---|---|

| 温度 (°C) | 电阻 (Ω) – 片上传感器 |

| 27 | 156.8 |

| 40 | 158.8 |

| 60 | 161.0 |

| 80 | 163.3 |

| 100 | 165.3 |

| 120 | 167.0 |

在位置1和2的WTop、WBottom以及背面金属上的温度传感器上测量电阻随温度的变化。通 过将数据拟合到二阶多项式表达式,以根据电阻测量结果确定温度。

每个已校准传感器的电阻随温度的变化如图14.6所示。所有传感器对温度均表现出线性 响应。如图14.6A所示,位于同一逻辑层上的片上传感器产生一致的结果。然而,由于两层之 间的工艺变化,顶层和底层逻辑层之间存在电阻差异,如图14.6A所示。在特定芯片内,传感 器结果一致,表明热传感器可以从单个传感器进行校准。然而,背金属传感器的情况并非如 此,如图14.6B所示。背金属上两个站点之间的电阻差异表明,背金属层的工艺变化大于片上 金属层,因此每个热传感器都必须在室温下单独校准和归一化。

实验装置包括使用HP 4145B半导体参数分析仪和HP 16058‐60003接口板。此外,还使 用Metric Technology公司提供的交互式表征软件来确定参数分析仪的设置。吉时利2420源 表用作电流源,为片上加热器和背金属加热器提供 0 到 110 毫安的电流(背面金属为 130 毫安)。参数分析仪将传感器上的电压从 0.1 伏特扫描到 0.6 伏特,步进为 0.01 伏特,从而确定此电压范围内的平均电阻。在每个站点和每个传感器(共六个数据位置)的每个电流水平下进行测量。此外,有六个不同的加热器位置,如 图 14.5 所示。根据 图14.6 中所示结果,将电阻测量值转换为温度。

通过控制电阻加热器以提供不同的测试条件,模拟常见的片上器件,并研究其对三维堆 叠内温度分布和热通道的影响。分别向位于WBottom和WTop的加热器提供电流。这些结果 如图 14.7A 和 B所示。位于每个芯片金属层2上的电阻加热器的功率密度最高可达17.4瓦/平 方毫米²,位于背面金属上的加热器的功率密度最高可达24.3瓦/平方毫米²(根据电流、电阻 和有效面积确定)。常见片上器件的功率密度列于表 14.2中。请注意,本实验中产生的功率 密度与实际集成电路一致[565–567]。

不同测试条件下的结果也在图 14.7中展示。通过移除围绕位于WTop 第2站点的传感器 和加热器周围的金属散热片,研究金属散热片(金属互连)对层内热分布的影响。该实验的 结果如图 14.7C 所示,并与WTop的实验结果进行了比较。

研究了在两个高活跃度器件模块上放置对热梯度的影响。本案例中 考察了两种不同情况:(1)WBottom 和 WTop 上的加热器同时工作且在垂直方向上直接 对齐;(2)WBottom 和 WTop 上的加热器同时工作但在物理位置上未对齐。这些结果如 图14.7D 和 E所示。第四种测试条件用于评估从背面金属热源到片上热传感器的热量传递情 况。两个背金属传感器中的一个作为加热器使用,另一个则用于检测温度。将CMOS 3D集成 电路置于热量可从减薄硅衬底背面耦合的位置时所产生的影响如 图14.7F所示。最后一种测 试条件考察了主动冷却对堆叠集成电路内部散热的影响。在3‐D堆叠上方1英寸处放置一个12 伏特、0.13安培、6,500转/分钟、8立方英尺/分钟的风扇,以实现对流散热。该风扇用于三种 不同的电阻加热器条件:(1)WBottom位置1处的加热器工作;(2)WBottom和WTop位 置1处的加热器同时工作;(3)背面金属位置1处的加热器工作。该冷却实验的结果分别如 图 14.7G 至14.7I所示。

| 表 14.2 常用集成电路的功率密度 |

|---|

| 电路 |

| ------ |

| 功率晶体管 |

| SC |

| PWM |

14.3 基于实验结果的设计考虑

第14.2节中所述的实验测试条件有助于了解三维集成电路中的热传播路径和热点形成。所有 测试配置均包括放置在金属层2中的加热器,用以模拟器件平面内有源器件产生的热量。所有 测试条件下的温度数据均由四个片上和两个背面金属电阻式温度传感器确定。电阻加热器的 位置决定了具体的测试条件。单个加热器、双加热器以及主动冷却作用下,六个温度传感器 处的温度列于表14.3中。这些数据源自转换后的测量电阻。以下小节将讨论最小化热点形成 的设计器件。

14.3.1 模块布局对热点形成的影响及缓解技术

堆叠两个芯片对3D集成电路温度分布的影响显著,如图14.7A 和B所示。当电阻加热器在 WBottom工作时,WBottom位置1观测到的最高温度比在WTop有源加热器工作时升高了 65.7%(从60.9°C升至100.9°C),如表14.4所列数据所示。最高观测温度出现在施加电流为 110毫安时。当加热器电流小于110毫安时,由于电流减小导致温度呈指数级下降, WBottom相对于WTop的温度升高百分比也随之降低。其余五个热传感器的数据显示温度升 高范围为6.1%至13.0%(见表14.4),其中13.0%的温升出现在位于WTop有源加热器正上方的传感器上。尽管距离热点1.3毫米处的热传感器测得的温度较低,但下降幅度不如[561],中报告的显著,在 500 μm距离处测得的温度降幅超过50%。对于所有小于50毫安的加热器电 流,当WBottom位置1的电阻加热器工作时,WBottom的观测温度与WTop位置1加热器工 作时同一WBottom传感器测得的温度相比,在20%以内。将高活跃度器件模块放置于 WBottom需特别考虑,因为热量传递至三维堆叠顶部路径的热阻高于放置于WTop的模块。

可以考虑三种潜在的缓解技术。在布局布线过程中,可将具有大电流负载的电路模块放 置在能最小化模块与散热器之间热阻的位置。电流负载对热分布有显著影响(当电流低于 50mA时,温度变化小于20%)。另一种控制模块活动性的方法是确保平均电流负载保持在 可接受值以下,从而避免热点形成。此外,还可采用被动与主动冷却技术,如硅通孔热通路 和微流体通道,通过改变高活跃度电路模块内的热阻路径,从内部器件平面移除热量。

14.3.2 水平和垂直热导管

研究层内热扩散的实验(图14.7B 和 C)需要进一步讨论。通过移除围绕热传感器和电阻式加热器周围的金属散热片,热量在水平方向上的扩散能力减弱。当加热电流为110毫安时,WTop 第2站点有源加热器正上方传感器测得的最高温度比WTop 站点 1的有源加热器高出16.4%。所有其他传感器显示的温度比存在金属散热片且施加110毫安加热电流时高出14.9%至27.7%,如表14.5所 列。当WTop 第2站点的加热器工作时,该位置温度升高是预期之中的;然而,位于位置1的 片上传感器所示温度降低(以负变化表示)的程度却不如预期显著。由于去除了水平方向的 金属散热片,从位置2到散热器的热阻增大,导致芯片上的温度升高。通过布置导热片将热量 在水平方向上分散,从而降低有效热阻,可使距离热点1.3mm且相隔一个器件平面的模块所 经历的最高温度下降。因此,必须通过提供热量从热点流向散热器的路径,来降低层间和层 内热阻。

| 表 14.3 不同加热器活动下的传感器温度(单位:°C) |

|--------------------------------------------------|

| 加热器活动 (毫安) | WTop 站点1 | WTop 站点2 | WBottom 位置1 | WBottom 站点2 | BM 位置1 | BM 站点2 |

|-------------------|------------|------------|----------------|----------------|----------|----------|

| 110 | 100.9 | 54.9 | 100.9 | 55.1 | 55.6 | 64.8 |

| 120 | 112.0 | 71.8 | 148.6 | 76.2 | 81.0 | 80.9 |

| 130 | 124.8 | 81.4 | 161.0 | 86.5 | 91.9 | 89.9 |

| 100 (双加热器) | 137.2 | 125.6 | 179.9 | 130.6 | 121.0 | 128.4 |

| 110 (双加热器) | 161.0 | 130.6 | 179.9 | 138.01 | 130.95 | 141.39 |

| 130 (背面加热) | 54.1 | 64.1 | 79.3 | 52.1 | 61.4 | 75.9 |

| 110 (背面加热) | 54.5 | 65.2 | 81.7 | 54.0 | 63.4 | 81.1 |

| 表 14.4 WBottom 与 WTop 加热器工作时的温度对比(110 mA) |

|---|

| 传感器位置 |

| ------------------- |

| WBottom 位置1 |

| WTop 站点1 |

| WBottom 站点2 |

| WTop 站点2 |

| BM 位置1 |

| BM 站点2 |

| 表 14.5 移除金属散热片后的温度升高(110 mA) |

|---|

| 传感器位置 |

| ------------------- |

| WTop 站点2 |

| WTop 站点1 |

| WBottom 位置1 |

| WBottom 站点2 |

| BM 位置1 |

| BM 站点2 |

14.3.3 多个对齐的有源模块

两个高度活跃的电路模块直接垂直对齐放置,会对3D集成电路的热分布产生显著影响。将一 个活跃模块放置在WBottom上所产生的热阻路径高于将其放置在WTop上的情况。通过对两 个垂直对齐的活跃电路模块进行分析,比较了仅在WBottom上放置一个加热器时的温度,与 在WTop和WBottom位置1同时放置两个活跃加热器所引起的温度升高情况。最大的温度升 高出现在WTop 站点 1,当施加电流为110毫安时,温度升高了79.4%(从69.6°C升至124.8°C)。最高芯片温度出现在WBottom位置1,当分别有110毫安电流流过一个加热器和两个加 热器时,该位置的最大温度从100.9°C上升到161.0°C,温度升高了59.6%。其余四个传感器 显示温度升高了56.5%至66.9%,对应的绝对温度从原来的52.1至55.6°C升至81.4至91.9°C。 当两个活跃电路模块相对于单个活跃模块垂直堆叠时,温度升高的百分比列于表14.6中,相 应的温度值列于表14.3中。

电流的大小也对3D集成电路内的热分布有显著影响。当两个加热器均施加40毫安电流时, 所有温度传感器测得的温升仍低于仅向WBottom加热器施加40毫安时的20%。两种缓解技术 包括限制电流流动,或停用电路模块以允许热量从热点散出。停用在高活动性电路模块中尤 为有效。主动与被动散热技术,如微流体通道和热通孔,也同样适用。

| 表 14.6 双加热器对齐时的温度升高(110 mA) |

|---|

| 传感器位置 |

| ------------------- |

| WTop 站点1 |

| WBottom 位置1 |

| WTop 站点2 |

| WBottom 站点2 |

| BM 位置1 |

| BM 站点2 |

14.3.4 多个非对齐有源模块

本小节讨论了增加间距对垂直非对齐有源电路之间最高温度的影响。比较了两个垂直对齐的 电阻式加热器(均位于位置1)与两个相距1.3毫米的加热器(WBottom加热器位于位置1, WTop加热器位于位置2)的情况。当将WTop加热器从位置1移动到位置2时,在电流达到 30毫安的情况下,六个温度传感器测得的温度降低了0.0%至5.4%。位于位置1的片上热传感 器显示,在电流达到90毫安时,温度变化范围为22.9%至0.5%。在峰值电流为110毫安时, 位置1处的温度最大升高了11.8%(WBottom)和9.9%(WTop),如表14.7所列。片上热 位置2的传感器检测到施加电流从40毫安(WTop为0.6%,WBottom为1.8%)增加到峰值 电流110毫安(WTop为54.3%,WBottom为51.0%)时,温度呈指数增长。当电流超过30 毫安时,背金属传感器处温度的指数增长表明通过背金属层存在强烈的热耦合。最高芯片温 度179.9°C出现在WBottom位置1。WTop站点1的最高温度为137.2°C,而其余传感器的最高 温度在121.0°C至130.6°C之间。

注意到三个主要的设计问题:(1)将同一层上高活跃度的电路模块相互分开,与垂直对 齐的电路相比,可以降低最高温度。(2)尽管非对齐的电路模块能够降低最高温度,但通向 散热器(此处为空气)路径的有效热阻显著影响最高芯片温度,如电流超过30毫安时温度上 升所表明的那样。(3)在三维集成电路中的合理布局规划需要分析每个电路模块产生的热量, 并在垂直和水平方向上适当放置发热模块,因为布局算法必须考虑这些问题以最小化芯片峰 值温度。

| 表 14.7 非对齐加热器下的温度变化(110 mA) |

|---|

| 传感器位置 |

| ------------------- |

| WBottom 位置1 |

| WTop 站点1 |

| WTop 站点2 |

| WBottom 站点2 |

| BM 位置1 |

| BM 站点2 |

14.3.5 附加设计考虑

三维结构对于异构系统特别有利。其中一些电路通常将模块连接到硅的背面 [568–570](例 如,光互连系统 [571] 中的垂直腔面发射激光器)。背面金属上的热加热器可模拟这些模块, 并支持分析从硅背面到其余三维结构的热分布和导热通道。

第四和第五种测试条件分别评估了从硅片背面的热源到片上热传感器的热传导,以及使 用风扇对3D集成电路进行对流冷却时最高温度的降低情况。在通过背面金属加热器施加的所 有电流负载条件下,所有热传感器的测量结果相互之间的差异均在6%以内。热量从背面金属 的热源流出,并均匀地向3D集成电路其余部分扩散。背面金属上热点的热扩散更为显著。然 而,很难使某一电路模块免受背面金属热源引起的热效应影响。在第五种测试条件下,当在 3D集成电路上方1英寸处放置一个风扇时,背面金属加热器通过10毫安电流时温度降低了 0.7%,而在130毫安电流负载下温度降低了21.9%。当位置1的两个片上加热器同时工作时, 在10毫安和110毫安电流下,最高温度分别降低了0.7%和11.9%。三种不同加热器配置下,加 热器电流从0毫安到110毫安时的温度降低百分比列于表14.8中。尽管使用风扇可使峰值温度 降低约12%,但对于位于3D集成电路内部深处的热点,仍需采用TTSVs和微流体通道等额外 的散热技术。

| 表 14.8 主动冷却(风扇)带来的温度降低 |

|---|

| 加热器配置 |

| ------------------------ |

| WBottom 位置1 |

| WBottom & WTop 位置1 |

| 背面金属 位置1 |

14.4 实验结果与仿真的验证

已对已制造的三维测试电路进行仿真,并与实验测量结果进行了比较。从仿真中提取了温度, 并确定了单位长度热阻。实验数据与这些仿真结果吻合良好。

14.4.1 仿真设置与工具

HotSpot模拟器[552,553,572]用于分析三维结构内的热传导路径。采用图14.8 所示结构来分 析三维堆叠内的热量传播路径,包括热导率对温度的依赖性。该堆叠由两层硅和一层铝背金 属层(即WTop、WBottom和BackMetal层)组成。背金属层通过TTSVs与WTop相连, TTSVs建模为 6 μm高的钨通孔。仿真中还包含了无源热层(不产生热量),以更准确地建模 三维测试电路(例如二氧化硅、体硅和金属层)。两个加热器被建模为散热块,分别放置在 背金属层上相距1.1毫米的位置,以及WTop和WBottom的金属层2上相距1.3毫米的位置。在 结构上分布有六个加热器/传感器位置,用于评估热量在水平和垂直方向上的传递情况。通过 开启不同的加热器来模拟片上不同功耗模块及其相关的热传导路径。在六个位置处测得相应 的温度。

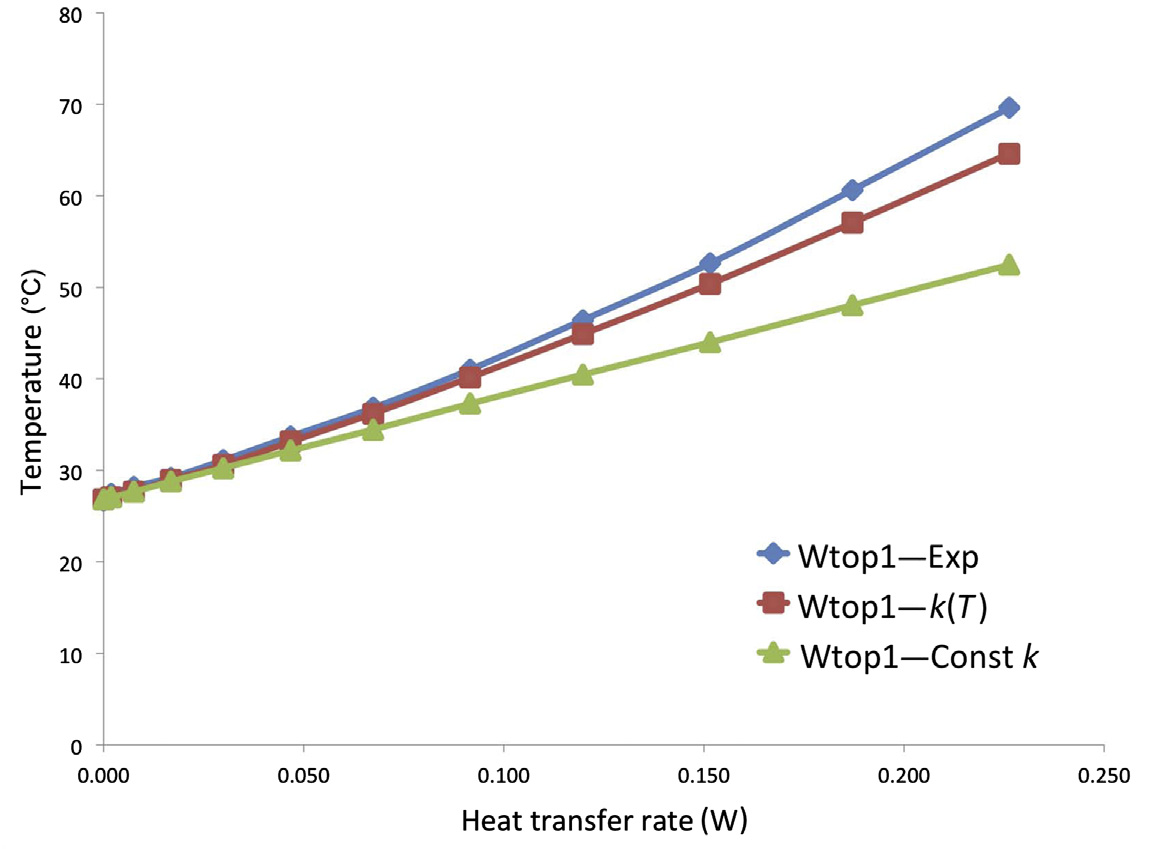

14.4.2 与实验结果的比较

测量温度与仿真的比较分别在图14.9 至14.11中给出,对应于水平、垂直和对角路径。对角路 径是从底层钨层位置1到顶层钨层位置2的路径。采用恒定热导率时,实验与仿真之间的最差 情况温差为25%,而采用温度相关热导率时,最差情况温差为7%。

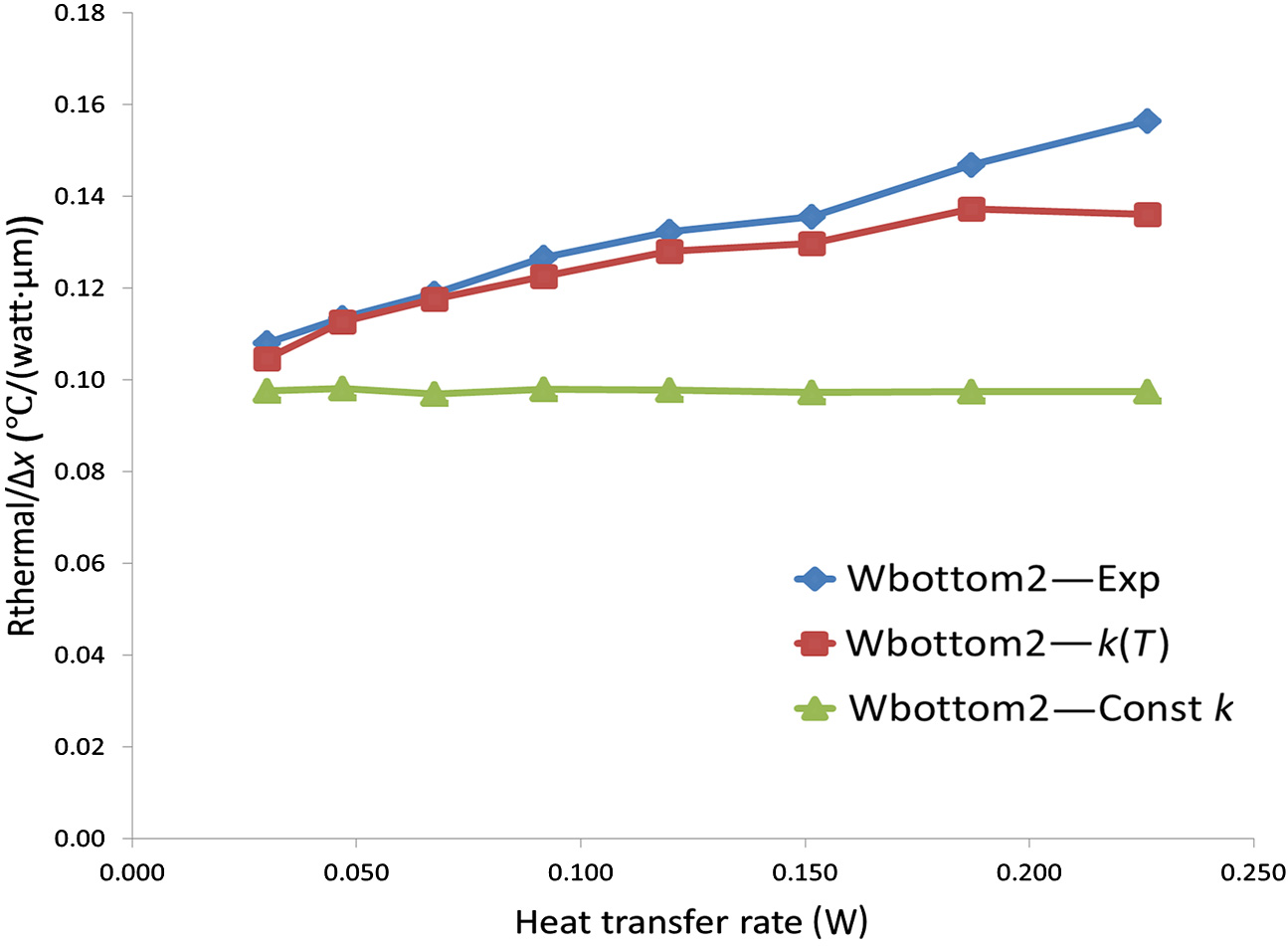

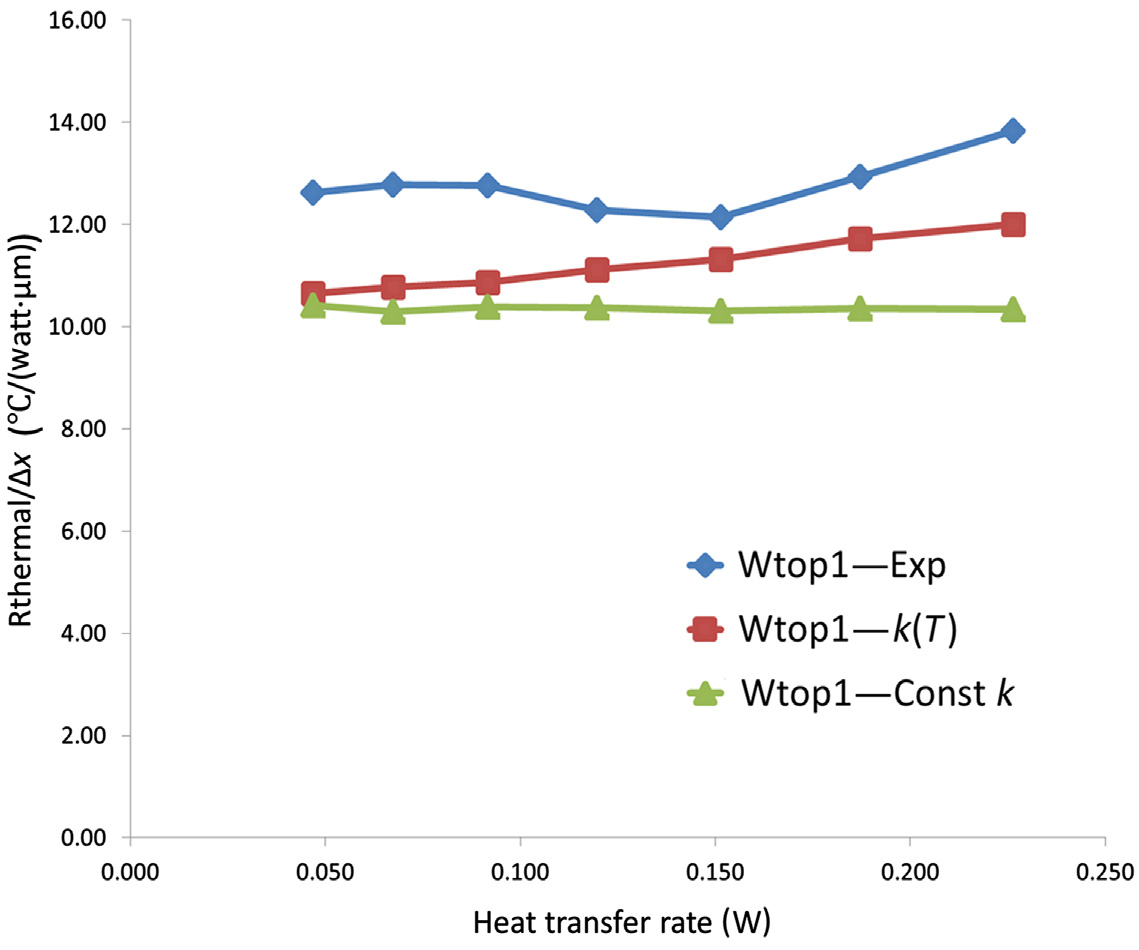

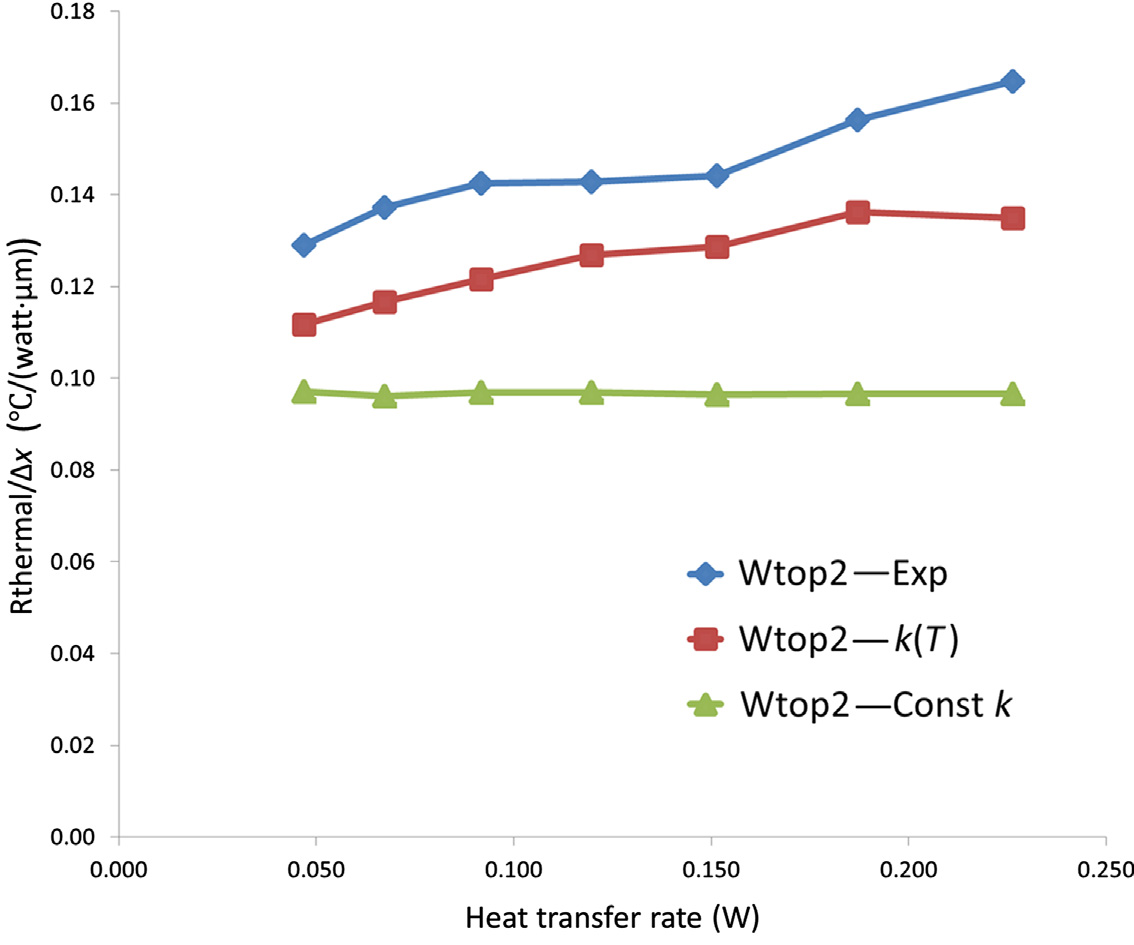

单位长度热阻在图14.12至14.14中分别针对水平、垂直和对角路径进行了比较。在图 14.13和图14.14中显示的第一个数据点偏离了实验数据和仿真结果的预期趋势,因此认为存 在测量误差,在评估仿真与实验数据差异时不予考虑。

实验和仿真均表明,横向热路径传导的热量大于纵向热路径。由于SiO₂的热导率远低于硅的热导率, 垂直路径的单位长度热阻比水平路径的单位长度热阻大两个数量级。

14.4.3 TSV密度对热耦合的影响

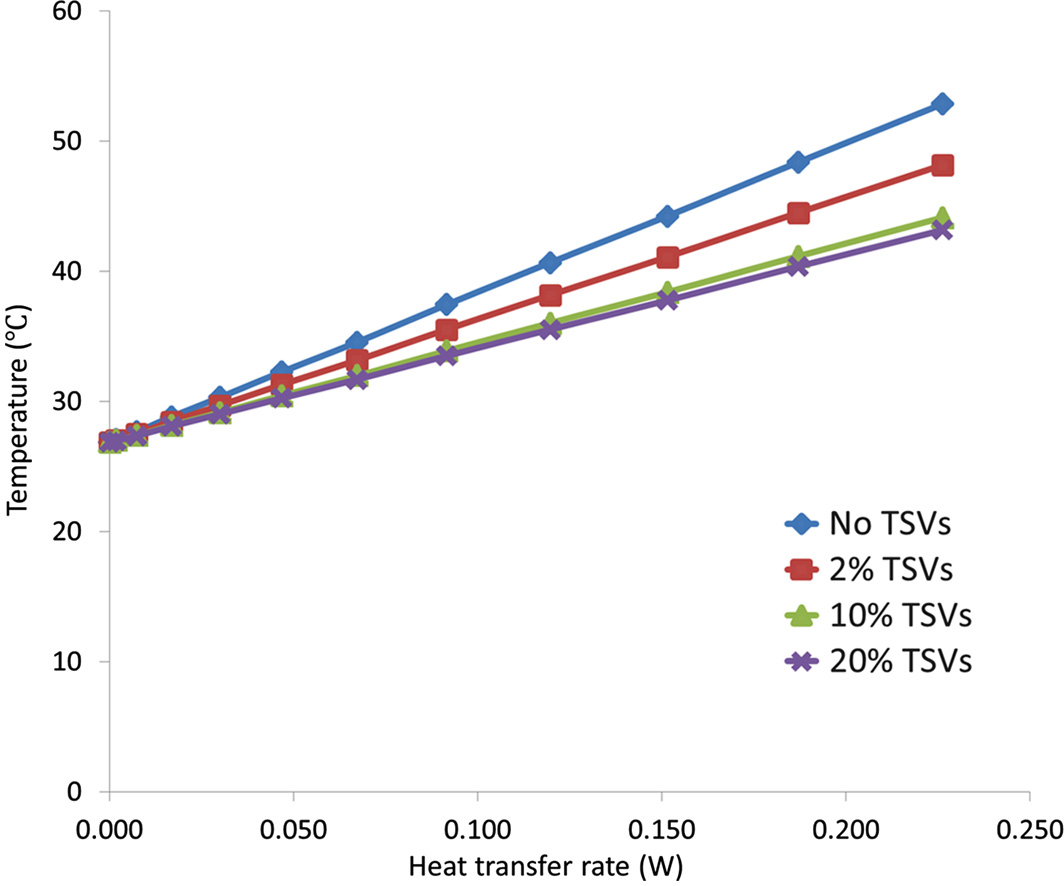

硅通孔的数量对层间的热耦合具有显著影响。硅通孔通常使用铜或钨制造,这些材料的热导 率高于绝缘层[127,173]。因此,硅通孔形成了将芯片内热点产生的热量传导至散热器的热传 导路径。科斯昆等人提出的HotSpot扩展模型[573]已被用于捕捉硅通孔密度对温度分布的影 响。该工具能够按模块分别表征材料的特性,从而支持设置不同数量硅通孔的多种仿真方案。

本仿真分析了WTop 站点 1的加热器/传感器对在四种不同配置下的情况:(1)无硅通孔, (2)2%硅通孔,(3)10%硅通孔,(4)20%硅通孔。仿真的硅通孔参数设定为直径1.25 μm, 100 μm间距,热阻率为0.005 mK/W,与已制造的三维测试电路中的硅通孔相似。每 种测试结构均在WTop 站点 1加热器的全功率范围内进行了仿真。仿真结果如图14.15所示。

这些结果表明,在WTop 站点 1 测得的温度随着硅通孔密度的增加而降低。该结果证实 了额外的硅通孔可形成从芯片内热点到散热器的热传导路径。一个有趣的发现是,温度的降 低并非恒定。这种行为是由于随着硅通孔密度的增加,热阻并联数量增多所致(类似于并联 的电阻)。

14.5 总结

三维集成电路的性能和可靠性受到显著热梯度的极大影响。本章的主要贡献总结如下:

- 由于热点形成,热效应可能会改变时钟和电源网络的性能。

- 适当的模块布局以及主动与被动散热技术对于确保三维集成电路在规定的热设计功耗(TDP)范围内运行至关重要。

- 已设计、制造并测试了一种用于研究三维堆叠内热传播的三维测试电路。

- 通过五种测试条件来表征三维集成电路中的热传播:(1)有源电路的位置,(2)层内热扩散的影响,(3)两个有源电路之间的相对垂直对齐,(4)来自硅片背面热源的热传导,以及(5)三维集成电路的对流冷却。

- 实验数据通过针对已制造的三维测试电路模型所进行的仿真得到了验证。

- 基于实验和仿真结果,提出了设计建议,以更好地管理热点形成,同时减少对相邻电路模块的影响。

- 描述了降低热量的两个重要考虑因素:(1)模块相对于散热器的位置显著影响热阻,从而影响热点的热量流动;(2)层间和层内热导通道的有效设计为散热提供了重要手段。

- 所述测试电路有助于增强对三维集成电路中热热点形成、传播及建模的理解。

582

582

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?