目录

| 章节 | 标题 | 核心内容 |

|---|---|---|

| 第一章 | 电路板江湖入门:FR4 基材的秘密 | FR4 材料特性、参数、选型指南 |

| 第二章 | 传输线武功秘籍:微带线阻抗计算 | 微带线结构、阻抗公式、影响因素 |

| 第三章 | 隐藏的高手:带状线阻抗设计 | 带状线结构、阻抗计算、优缺点 |

| 第四章 | 电磁原理心法:阻抗计算的物理本质 | 传输线理论、电磁场分布、特性阻抗推导 |

| 第五章 | 法拉第笼的结界:电磁屏蔽技术 | 屏蔽原理、材料选择、PCB 屏蔽设计 |

| 第六章 | PCB 布板布线实战宝典 | 布局原则、布线技巧、 impedance control 案例 |

| 第七章 | 常见问题与解决方案 | 阻抗不匹配、EMC 问题、测试与调试 |

第一章:电路板江湖入门:FR4 基材的秘密

1.1 FR4 材料的基本特性

| 参数 | 数值范围 | 单位 | 说明 |

|---|---|---|---|

| 介电常数 (εr) | 3.8 - 4.8 | - | 频率 1MHz 时的典型值,影响信号传播速度 |

| 介质损耗角正切 (tanδ) | 0.001 - 0.02 | - | 信号衰减的重要指标,越小越好 |

| 厚度 | 0.1 - 3.2 | mm | 常用厚度 0.2mm、0.4mm、0.8mm、1.6mm |

| 铜箔厚度 | 1/3 - 2 | oz | 1oz=35μm,影响电流承载能力和阻抗 |

| 玻璃化温度 (Tg) | 130 - 180 | ℃ | 衡量耐热性,高端板材可达 180℃以上 |

| 热膨胀系数 (CTE) | 10 - 20 | ppm/℃ | 影响尺寸稳定性,与铜箔 CTE 匹配重要 |

| 击穿电压 | 20 - 40 | kV/mm | 绝缘性能指标 |

1.2 FR4 材料的分类与选型

| 类型 | 特点 | 适用场景 | 价格等级 |

|---|---|---|---|

| 普通 FR4 | εr=4.2-4.5, tanδ=0.015 | 消费电子、一般工业产品 | 低 |

| 高频 FR4 | εr=3.8-4.0, tanδ=0.002-0.008 | 通信设备、高速信号 | 中 |

| 无卤素 FR4 | 环保、低烟、低毒 | 医疗设备、汽车电子 | 中高 |

| 高 Tg FR4 | Tg>150℃ | 高温环境、军工产品 | 高 |

| 厚铜 FR4 | 铜箔厚度 > 2oz | 大电流、电源板 | 高 |

1.3 FR4 材料对阻抗的影响

| 影响因素 | 对阻抗的作用 | 设计建议 |

|---|---|---|

| 介电常数 εr | εr↑ → Z0↓ | 精确控制 εr,选择稳定的板材 |

| 介质厚度 h | h↑ → Z0↑ | 根据目标阻抗调整 h,常用 0.4-1.2mm |

| 铜箔粗糙度 | 粗糙度↑ → 损耗↑ | 高速信号选择低粗糙度铜箔(≤1μm) |

| 频率特性 | εr 随频率变化 | 宽频设计需考虑 εr 的频率稳定性 |

第二章:传输线武功秘籍:微带线阻抗计算

2.1 微带线的结构与特点

| 结构参数 | 定义 | 常用范围 | 对阻抗的影响 |

|---|---|---|---|

| 线宽 w | 信号导体的宽度 | 0.1-5mm | w↑ → Z0↓ |

| 介质厚度 h | 信号层到参考平面的距离 | 0.1-2mm | h↑ → Z0↑ |

| 铜箔厚度 t | 信号导体的厚度 | 0.018-0.1mm | t↑ → Z0↓ |

| 介电常数 εr | 基材的介电常数 | 3.8-4.8 | εr↑ → Z0↓ |

| 参考平面 | 信号层下方的铜层 | - | 必须完整,减少开槽 |

2.2 微带线阻抗计算公式

| 公式名称 | 适用条件 | 公式 | 说明 |

|---|---|---|---|

| 近似公式 | w/h ≤ 1 | Z0 = (87/√(εr+1.41)) × ln(5.98h/(w+0.8t)) | 简单易用,误差较大 |

| 修正公式 | w/h > 1 | Z0 = (60/√((εr+1)/2)) × ln(4h/(0.67πt(1+1.39w/h+0.667ln(w/h+1.444)))) | 考虑铜箔厚度影响 |

| 精确公式 | 任意 w/h | Z0 = (120π/√(εeff)) / (w/h + 1.393 + 0.667ln(w/h + 1.444)) | 最准确,εeff 为有效介电常数 |

2.3 有效介电常数计算

| 公式 | 适用场景 | 说明 |

|---|---|---|

| εeff = (εr+1)/2 + (εr-1)/2 × 1/√(1+12h/w) | w/h ≥ 1 | 微带线的有效介电常数 |

| εeff = (εr+1)/2 + (εr-1)/2 × [1/√(1+12h/w) + 0.04(1-w/h)²] | w/h < 1 | 修正公式,提高精度 |

2.4 微带线阻抗影响因素分析

| 影响因素 | 变化趋势 | 影响程度 | 控制方法 |

|---|---|---|---|

| 线宽 w | w↑10% → Z0↓3-5Ω | 高 | 精确控制光刻工艺,线宽公差 ±0.05mm |

| 介质厚度 h | h↑10% → Z0↑5-7Ω | 高 | 选择高精度基材,厚度公差 ±10% |

| 介电常数 εr | εr↑10% → Z0↓3-4Ω | 中 | 选择 εr 稳定的板材,控制环境湿度 |

| 铜箔厚度 t | t↑10% → Z0↓1-2Ω | 低 | 根据电流需求选择合适铜厚,一般 0.5oz |

| 频率 | 1-10GHz 影响 < 5% | 低 | 宽频设计需考虑 εr 的频率特性 |

| 温度 | 0-100℃影响 < 3% | 低 | 工业级设计考虑温度补偿 |

第三章:隐藏的高手:带状线阻抗设计

3.1 带状线的结构与特点

| 结构参数 | 定义 | 常用范围 | 对阻抗的影响 |

|---|---|---|---|

| 线宽 w | 信号导体的宽度 | 0.1-5mm | w↑ → Z0↓ |

| 介质厚度 b | 上下参考平面间距 | 0.2-4mm | b↑ → Z0↑ |

| 导体厚度 t | 信号导体的厚度 | 0.018-0.1mm | t↑ → Z0↓ |

| 介电常数 εr | 基材的介电常数 | 3.8-4.8 | εr↑ → Z0↓ |

| 上下参考平面 | 信号层上下的铜层 | - | 必须完整覆盖,提供良好屏蔽 |

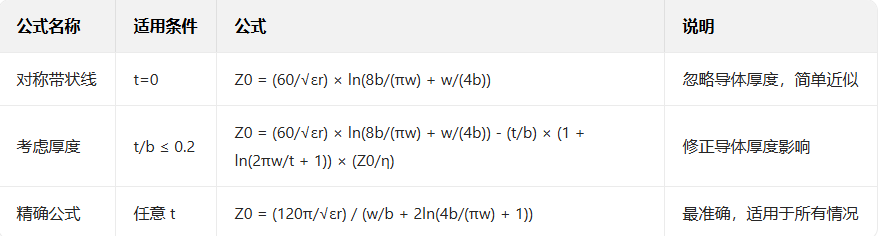

3.2 带状线阻抗计算公式

3.3 微带线与带状线对比

| 特性 | 微带线 | 带状线 | 应用场景 |

|---|---|---|---|

| 结构 | 单参考平面,半开放式 | 双参考平面,全封闭式 | 微带线:普通 PCB;带状线:高速、高屏蔽需求 |

| 阻抗范围 | 20-120Ω | 20-150Ω | 微带线:中低阻抗;带状线:全范围阻抗 |

| 信号完整性 | 易受干扰,辐射较大 | 屏蔽良好,干扰小 | 带状线适合高速信号(>1GHz) |

| 损耗 | 介质损耗 + 辐射损耗 | 仅介质损耗,损耗较小 | 高频应用优先选择带状线 |

| 制造难度 | 简单,成本低 | 复杂,成本高 | 微带线:大批量生产;带状线:高端产品 |

| 尺寸 | 相对较薄 | 相对较厚 | 空间受限选微带线,性能优先选带状线 |

第四章:电磁原理心法:阻抗计算的物理本质

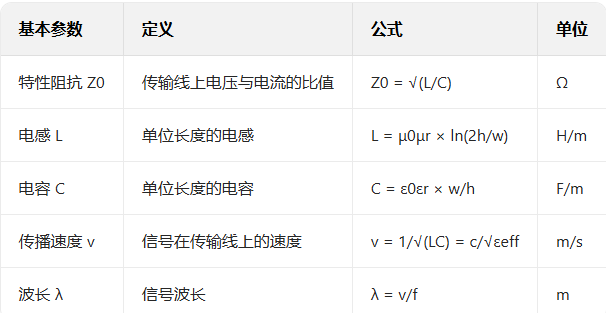

4.1 传输线理论基础

4.2 电磁场分布

| 传输线类型 | 电场分布 | 磁场分布 | 能量分布 |

|---|---|---|---|

| 微带线 | 集中在介质内和表面,部分辐射 | 围绕导体,呈同心圆分布 | 60-70% 在介质内,30-40% 在空气中 |

| 带状线 | 完全封闭在介质内,无辐射 | 围绕导体,呈同心圆分布 | 100% 在介质内,无辐射损耗 |

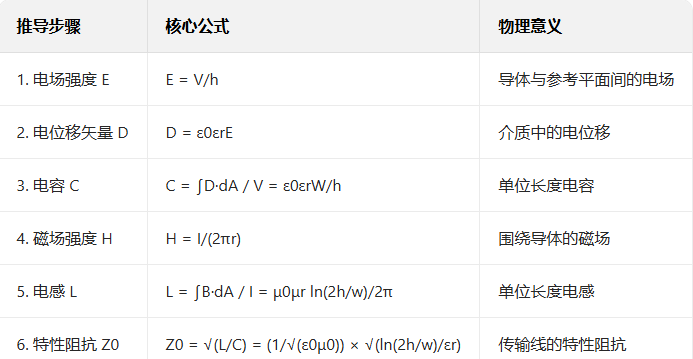

4.3 特性阻抗的电磁推导

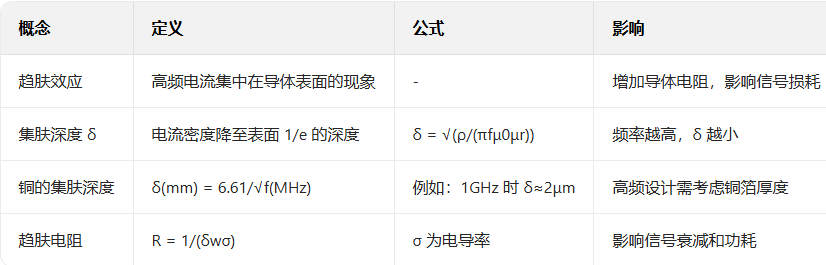

4.4 趋肤效应与集肤深度

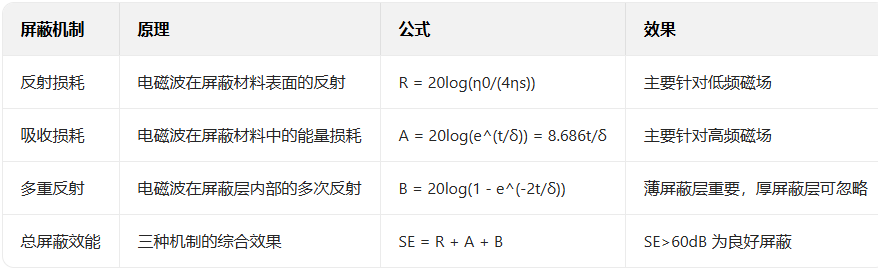

第五章:法拉第笼的结界:电磁屏蔽技术

5.1 电磁屏蔽原理

5.2 屏蔽材料选择

| 材料 | 电导率 σ(S/m) | 磁导率 μr | 集肤深度 δ(mm)@1GHz | 屏蔽效能 SE (dB)@1GHz | 应用场景 |

|---|---|---|---|---|---|

| 铜 | 5.8×10^7 | 1 | 0.002 | 120 | PCB 内层屏蔽、连接器 |

| 铝 | 3.8×10^7 | 1 | 0.0025 | 110 | 外壳屏蔽、散热片 |

| 钢 | 5.0×10^6 | 1000 | 0.01 | 80 | 低频磁场屏蔽 |

| 银 | 6.1×10^7 | 1 | 0.0018 | 125 | 高端精密设备 |

| 镍 | 1.4×10^7 | 600 | 0.004 | 90 | 电磁干扰滤波器 |

5.3 PCB 屏蔽设计技术

| 屏蔽类型 | 设计方法 | 优点 | 缺点 | 适用场景 |

|---|---|---|---|---|

| 接地平面 | 完整的铜层作为参考平面 | 成本低,效果好 | 占用 PCB 面积 | 所有 PCB 设计 |

| 屏蔽罩 | 金属罩覆盖敏感电路 | 屏蔽效果好,隔离彻底 | 增加成本和高度 | 射频电路、高速信号 |

| 屏蔽网 | 金属网覆盖 PCB | 重量轻,透气性好 | 屏蔽效能有限 | 一般干扰环境 |

| 导电涂层 | PCB 表面涂导电材料 | 工艺简单,成本低 | 耐久性差 | 临时或低成本产品 |

| 差动信号 | 平衡传输,相互抵消干扰 | 抗干扰能力强 | 设计复杂 | 高速数据传输 |

5.4 法拉第笼在 PCB 中的应用

| 应用场景 | 设计要点 | 实现方法 | 效果验证 |

|---|---|---|---|

| 敏感电路屏蔽 | 用接地平面和屏蔽罩包围 |

1. 完整接地平面 2. 屏蔽罩接地 3. 信号滤波 | 测试屏蔽效能 SE>60dB |

| 电源完整性 | 减少电源噪声干扰 |

1. 电源平面与接地平面紧密耦合 2. 去耦电容布局 3. 减少平面开槽 | 电源噪声 < 50mVpp |

| EMC compliance | 满足电磁兼容标准 |

1. 屏蔽设计 2. 滤波措施 3. 接地优化 | 通过 CE/FCC 认证 |

| 高速信号隔离 | 减少串扰 |

1. 带状线结构 2. 地线隔离 3. 屏蔽过孔 | 串扰 < -40dB |

第六章:PCB 布板布线实战宝典

6.1 PCB 布局原则

| 布局原则 | 具体要求 | 设计技巧 | 常见错误 |

|---|---|---|---|

| 功能分区 | 按功能划分区域:电源区、模拟区、数字区、射频区 |

1. 模拟区远离数字区 2. 高频区远离敏感区 3. 发热元件分散布局 | 功能混合布局,干扰严重 |

| 信号流向 | 按信号流向布局:输入→处理→输出 |

1. 直线布局,减少弯曲 2. 避免信号回流交叉 3. 关键信号最短路径 | 信号路径过长,延迟大 |

| 电源布局 | 电源区靠近负载,减少压降 |

1. 电源平面完整 2. 去耦电容靠近电源引脚 3. 大电流路径短而宽 | 电源路径长,压降大,噪声高 |

| 散热设计 | 发热元件布局考虑散热 |

1. 大功率元件靠近边缘 2. 散热片与通风配合 3. 避免热聚集 | 元件密集,散热不良,可靠性下降 |

| 可制造性 | 考虑 PCB 制造工艺 |

1. 线宽≥0.2mm 2. 间距≥0.2mm 3. 过孔大小合适 | 设计过于精细,无法制造 |

6.2 布线设计技巧

| 布线类型 | 设计要求 | 具体参数 | 验证方法 |

|---|---|---|---|

| 阻抗控制 | 严格控制传输线阻抗 |

1. 微带线:w=0.8mm, h=0.4mm, Z0=50Ω 2. 带状线:w=0.6mm, b=0.8mm, Z0=50Ω 3. 差分线:间距 = 线宽,Zdiff=100Ω | TDR 测试,阻抗偏差 ±10% |

| 差分信号 | 保持差分对长度匹配 |

1. 长度差≤5mm 2. 平行布线,间距一致 3. 远离其他信号 | 眼图测试,抖动 < 10% UI |

| 时钟信号 | 减少时钟辐射 |

1. 最短路径布线 2. 时钟线周围接地保护 3. 避免过孔和直角 | 频谱分析,辐射 < 30dBμV/m |

| 电源布线 | 降低电源噪声 |

1. 电源线宽≥1mm/1A 2. 多层板使用电源平面 3. 去耦电容布局合理 | 电源噪声测试,纹波 < 100mVpp |

| 接地设计 | 减少接地环路 |

1. 单点接地或星形接地 2. 模拟地与数字地分开 3. 接地平面完整 | 接地电阻测试,<0.1Ω |

6.3 阻抗控制案例分析

| 案例 | 设计要求 | 实现方案 | 测试结果 |

|---|---|---|---|

| 50Ω 微带线 | Z0=50Ω±10%, f=1GHz |

1. FR4 基材,εr=4.2 2. 介质厚度 h=0.4mm 3. 线宽 w=0.8mm 4. 铜箔厚度 t=0.035mm | TDR 测试:Z0=51.2Ω,偏差 + 2.4% |

| 100Ω 差分线 | Zdiff=100Ω±10%, f=2GHz |

1. 微带线结构 2. 线宽 w=0.6mm 3. 线间距 s=0.6mm 4. 介质厚度 h=0.4mm | 网络分析仪测试:Zdiff=98.5Ω,偏差 - 1.5% |

| 75Ω 带状线 | Z0=75Ω±10%, f=500MHz |

1. 带状线结构 2. 介质厚度 b=1.2mm 3. 线宽 w=0.8mm 4. 上下参考平面完整 | 阻抗测试仪:Z0=73.8Ω,偏差 - 1.6% |

| 高速 DDR4 | Zdiff=100Ω, 长度匹配 |

1. 带状线差分对 2. 长度差≤3mm 3. 过孔数量≤2 个 4. 端接电阻 100Ω | 眼图测试:眼高 > 200mV,抖动 < 5% UI |

第七章:常见问题与解决方案

7.1 阻抗不匹配问题

| 问题现象 | 原因分析 | 解决方案 | 预防措施 |

|---|---|---|---|

| 信号反射 | 阻抗突变,如线宽变化、过孔、连接器 |

1. 优化布线,保持阻抗一致 2. 增加端接电阻 3. 使用阻抗匹配网络 |

1. 严格控制线宽和间距 2. 减少过孔数量 3. 选择匹配的连接器 |

| 信号衰减 | 介质损耗、趋肤效应、辐射损耗 |

1. 选择低损耗基材 2. 增加线宽,减少长度 3. 使用屏蔽措施 |

1. 高频设计选择高频 FR4 2. 关键信号最短路径 3. 避免直角和过长平行 |

| 串扰 | 相邻信号耦合,电磁干扰 |

1. 增加信号间距 2. 使用地线隔离 3. 差分信号传输 |

1. 信号间距≥3 倍线宽 2. 敏感信号周围接地 3. 时钟信号差分传输 |

| 时序问题 | 信号延迟不一致,影响同步 |

1. 长度匹配 2. 调整线宽控制延迟 3. 使用延迟线 |

1. 关键信号长度匹配 2. 模拟信号与数字信号分离3. 考虑温度对延迟的影响 |

7.2 EMC 问题与解决方案

| EMC 问题 | 测试结果 | 原因分析 | 整改措施 |

|---|---|---|---|

| 辐射超标 | 辐射场强 > 30dBμV/m |

1. 时钟信号辐射 2. 未屏蔽的传输线 3. 接地不良 |

1. 时钟线增加屏蔽 2. 使用差分信号 3. 优化接地设计 |

| 传导干扰 | 电源线传导 > 40dBμV |

1. 电源噪声 2. 缺少滤波器 3. 接地环路 |

1. 增加 EMI 滤波器 2. 优化去耦电容 3. 单点接地 |

| 静电放电 | ESD 测试失败 |

1. 缺少 ESD 保护 2. 敏感元件暴露 3. 接地不良 |

1. 增加 ESD 保护器件 2. 屏蔽敏感元件 3. 加强接地 |

| 磁场耦合 | 磁场干扰 > 20dBμA/m |

1. 大电流环路 2. 缺少磁场屏蔽 3. 线圈靠近 |

1. 减少电流环路面积 2. 使用高磁导率材料 3. 线圈远离敏感电路 |

7.3 测试与调试方法

| 测试项目 | 测试设备 | 测试标准 | 合格指标 | 调试技巧 |

|---|---|---|---|---|

| 阻抗测试 | TDR 时域反射仪 | IPC-TM-650 | 阻抗偏差 ±10% |

1. 调整线宽和间距 2. 更换基材 3. 优化过孔设计 |

| 信号完整性 | 示波器、眼图仪 | IEEE 802.3 | 眼高 > 200mV,抖动 < 10% UI |

1. 增加端接电阻 2. 优化布线 3. 调整驱动强度 |

| EMC 测试 | 频谱分析仪、屏蔽室 | CISPR 22 | 辐射 < 30dBμV/m,传导 < 40dBμV |

1. 增加屏蔽 2. 优化滤波 3. 调整接地 |

| 电源完整性 | 电源分析仪 | IPC-9592 | 纹波 < 100mVpp,噪声 < 50mV |

1. 增加去耦电容 2. 优化电源平面 3. 调整稳压电路 |

| 热测试 | 红外热像仪 | IEC 60068 | 元件温度 < 85℃ |

1. 优化布局 2. 增加散热片 3. 调整功率分配 |

结语

电路板设计是一门集电磁学、材料科学、制造工艺于一体的综合技术。本文详细介绍了 FR4 基材特性、微带线和带状线阻抗计算方法、电磁屏蔽原理以及 PCB 布板布线设计技巧,希望能为电子工程师提供全面的技术参考。

在实际设计中,需要根据具体应用场景综合考虑各种因素,平衡性能、成本和可制造性。随着高速信号和高频电路的广泛应用,阻抗控制和电磁兼容性将变得越来越重要,工程师需要不断学习和掌握新的设计技术,以应对日益复杂的挑战。

2134

2134

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?