modelsim仿真时,如果使用到了vivado的IP就会报错,本次就告诉大家如何将vivado的IP添加到modelsim中直接仿真。

一、生成ini文件以及IP打包

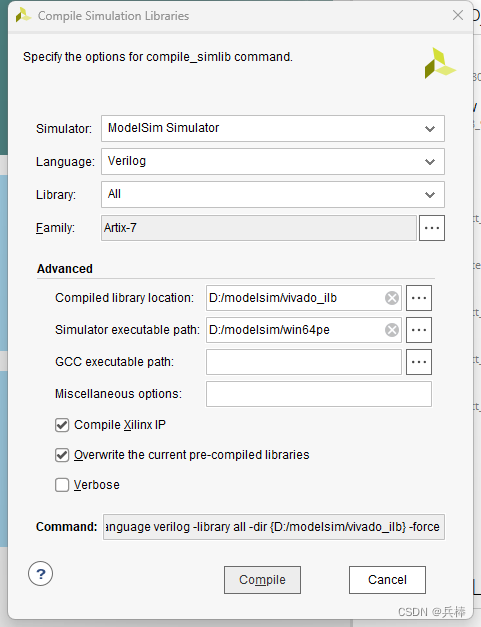

打开vivado,点击上方的Tools-->Compile Simulation Libraries得到如下界面

simulator:选择相应的仿真器,本次讲解的时modelsim,所以该选什么你们懂的。

language:选择语言,自行判断。

library:一个相关的一个是相关的,也就是你调用的IP是相关的,没有调用的就是不相关的。总之你不理解的话,就选All。

family:选择你所用的板子,同理不知道什么板子的就全选。

compiled library location:选择IP包和ini文件的存储位置(注意:要记清这个位置,而且最好是在modelsim安装的地方)。

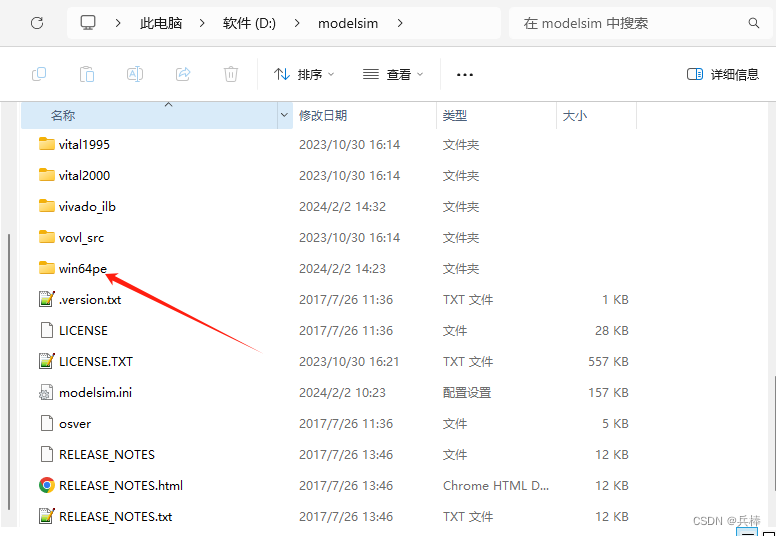

simulator executable path:选择modelsim启动程序,找到你modelsim安装的位置里面有win64类似的启动程序。比如我的位置在这里

后面的几个就不解释了,用不到!

勾选的话就选第一个就行,我把第二个也选了是因为我已经生成了,所以需要覆盖一下。

然后点击compile就可以了。那之后就是慢慢等了,大概要个半个多小时的时间。

二、综合IP与ini的关系

1.修改权限

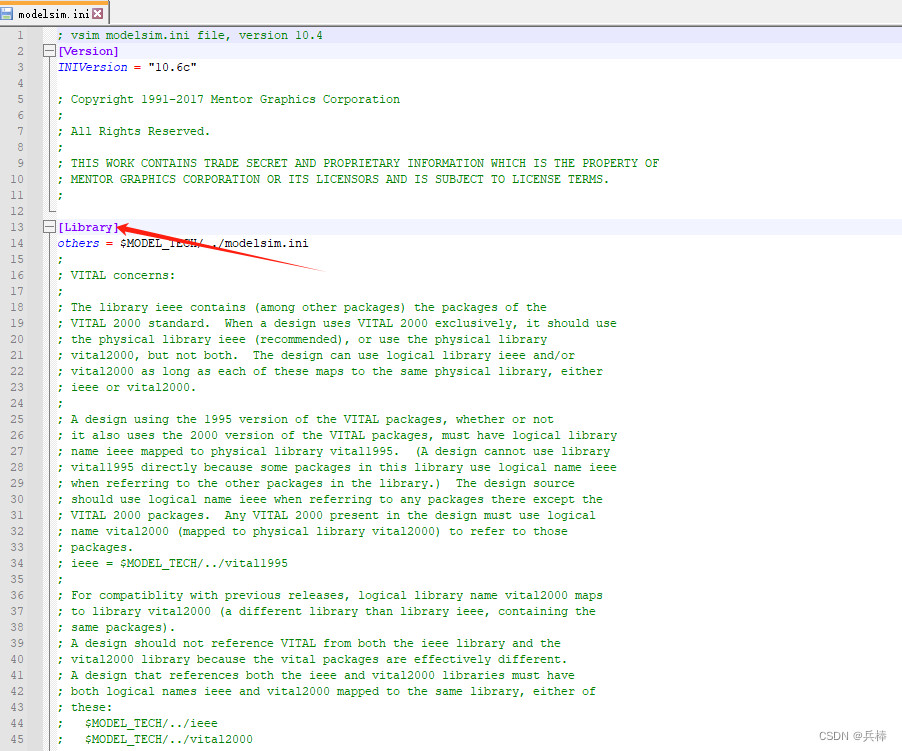

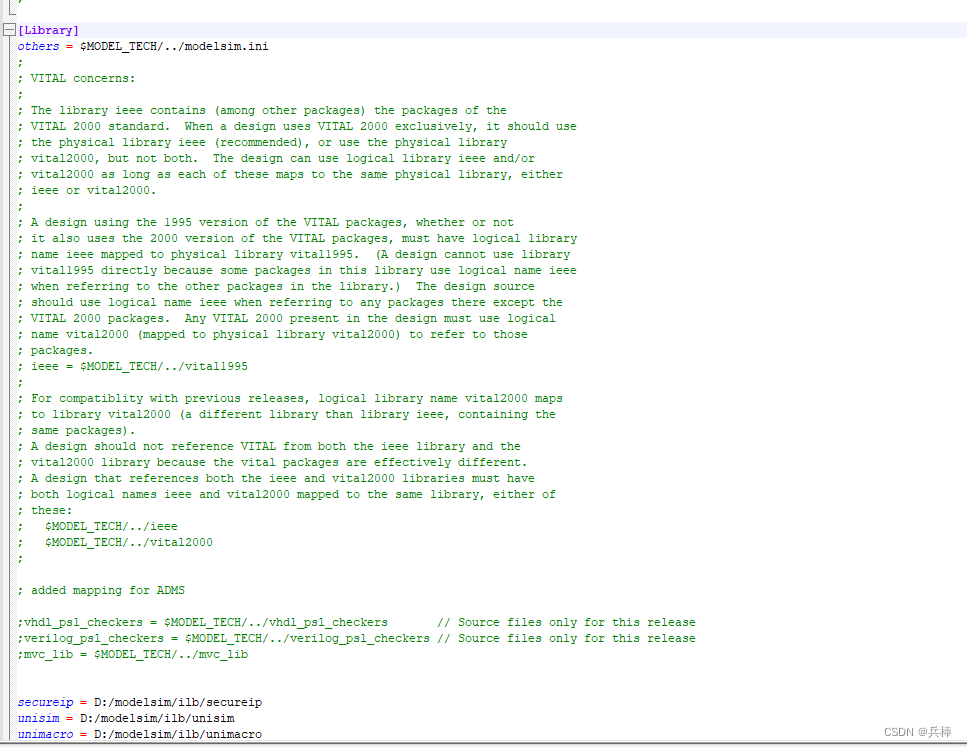

用文本方式打开modelsim安装下的modelsim.ini(后面简称为ini1),同时记得在属性里面修改一下它的权限,把它改为可改写。

2.修改

然后打开,找到library

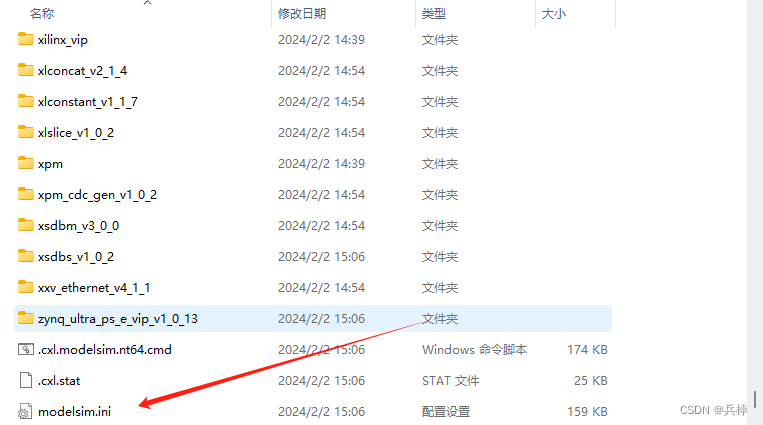

同时打开我们刚刚生成的ini,也就是上面我让你记住的文件位置。里面也会有一个modelsim.ini(后面就简称为ini2)

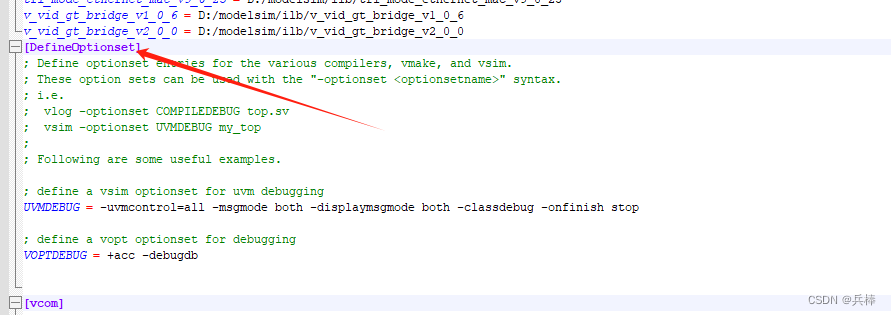

打开后别弄混淆了哦,两个可是长得很像的,也同样找到相应的位置library位置,将ini2中library下面,到DefineOptionset中间的数据复制到ini1相同的位置(要覆盖里面的library到DefineOptionset)。这一步慢慢看懂看清楚,错了就要重来的喔!

3.检查

3.检查

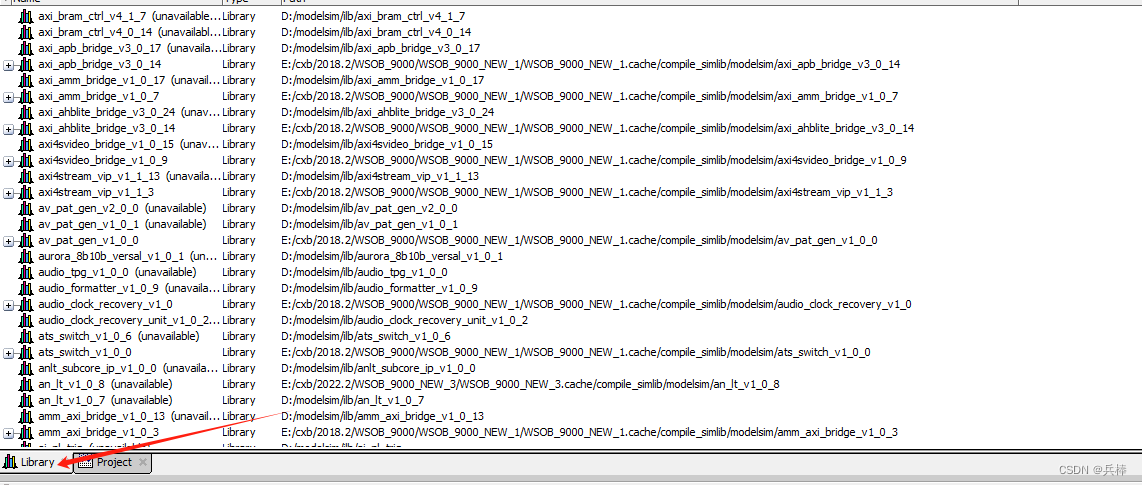

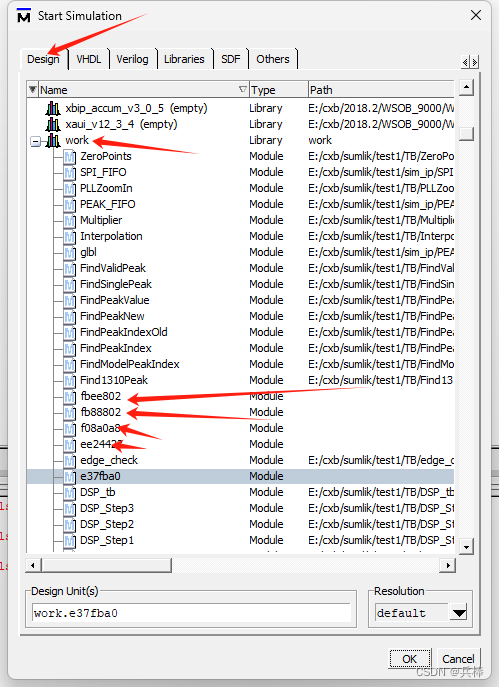

弄完之后你就可以检查一下modelsim有没有上面的IP,打开modelsim点开library,就可以看到相应的IP。但还没完,有后续的!

三、加入数据

1.找到IP

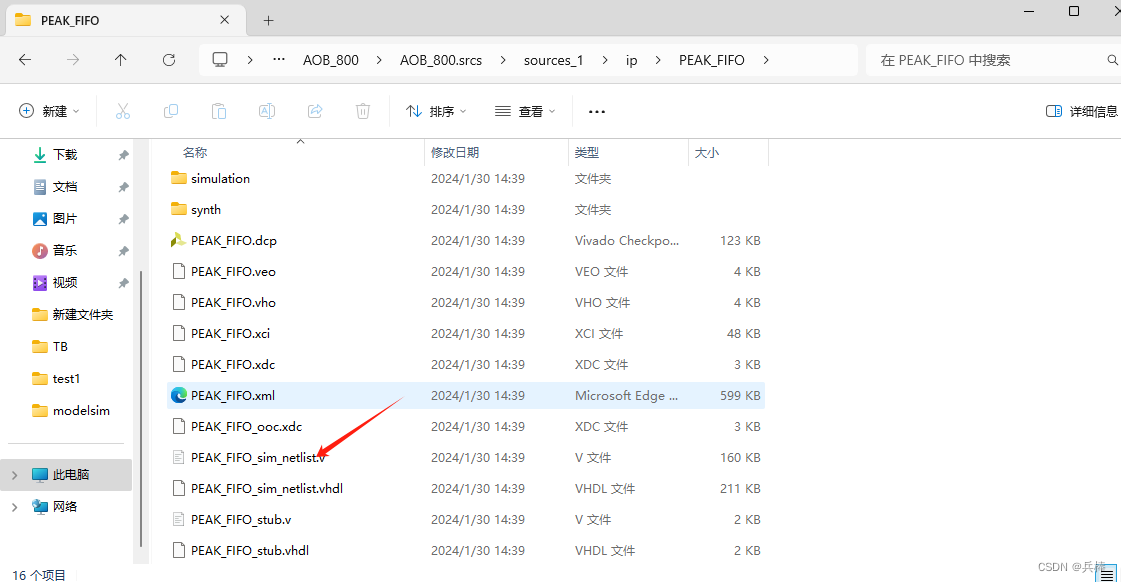

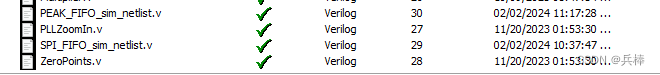

打开你vivado生成的程序文件夹,找到你想要仿真的IP,复制 xxx_sim_netlist.v,如果你用的是VHDL你就赋值下面那个。

2.存储IP

将IP粘贴到你的仿真程序文件夹里,再和你的仿真程序一起加到modelsim里(modelsim创建和加入文件应该不需要我交吧,需要的留言,我看看有多少,后面再补充),我用的是FIFO示例

3.加入库

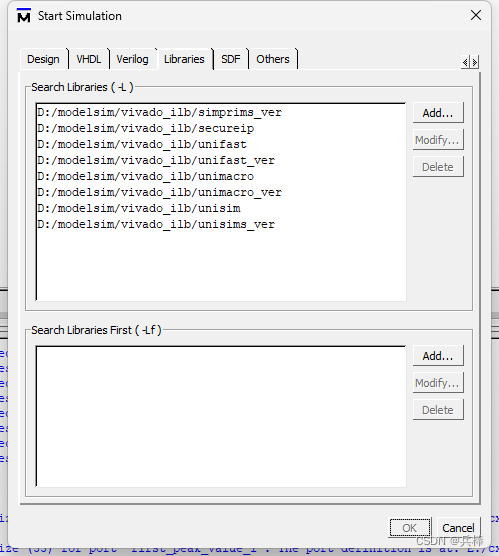

将程序compile之后,点simulate-->start simulate-->Libraries-->add...

向里面加入以下五个库secureip、simprims_ver、unifast、unifast_ver、unimacro、unimacro_ver、unisim、unisims_ver。这些库在刚刚vivado生成的文件夹里面!加完之后就可以在work里面找到一些数据命名的文件。

然后你就可以点击ok仿真了。

四、错误

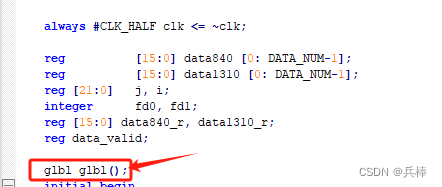

在仿真文件里面例化一下glbl,这样可以避免时钟报错,还有modelsim是不支持PS端的仿真,别瞎搞!另外其他报错,就是你需要重新添加一下上面的库,因为重新打开貌似需要重新添加库。还有vivado生成的那些文件不要删除、也不要移动或者改名字,改了那就改回来,要么你就从头开始!

后续有问题就留言吧,或者私聊,觉得有用就动动小手点个赞+收藏+关注,后续会出一些更多有意义的操作。

本文介绍了将Vivado的IP添加到Modelsim中进行仿真的方法。首先要生成ini文件并打包IP,接着处理综合IP与ini的关系,包括修改权限、复制数据和检查IP。然后加入数据,找到并存储IP,添加相关库。最后还提到了避免时钟报错等错误处理方法。

本文介绍了将Vivado的IP添加到Modelsim中进行仿真的方法。首先要生成ini文件并打包IP,接着处理综合IP与ini的关系,包括修改权限、复制数据和检查IP。然后加入数据,找到并存储IP,添加相关库。最后还提到了避免时钟报错等错误处理方法。

7975

7975

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?